## Intel® Xeon® E5-2600 v4 Processor Product Family

**Specification Update**

April 2022

Reference Number: 333811-008US

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel, the Intel logo, Intel Core, Pentium, Enhanced Intel SpeedStep Technology and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\ensuremath{\mathbb{C}}$  2022, Intel Corporation. All Rights Reserved.

## Contents

| Preface                       | 5  |

|-------------------------------|----|

| Identification Information    | 7  |

| Summary Tables of Changes     | 9  |

| Integrated Core/Uncore Errata | 14 |

T

## **Revision History**

| Revision | Description                                                                                                                          | Date           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 008      | Added BDF109                                                                                                                         | April 2022     |

| 007      | <ul><li>Added BDF108</li><li>Added Nomenclature S-Spec Number</li></ul>                                                              | March 2022     |

| 006      | Added BDF105 - BDF107                                                                                                                | November 2020  |

| 005      | Added BDF102 - BDF104                                                                                                                | September 2019 |

| 004      | Added BDF100 and BDF101                                                                                                              | March 2019     |

| 003      | Added BDF86 - BDF99                                                                                                                  | November 2018  |

| 002      | <ul> <li>Updated Table 1 and Table 2</li> <li>Added Table 5</li> <li>Removed BDF42 and BDF61</li> <li>Added BDF64 - BDF85</li> </ul> | December 2016  |

| 001      | • Initial Release                                                                                                                    | May 2015       |

§

## Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

### **Affected Documents**

| Document Title                                                                                      | Document<br>Number/Location |

|-----------------------------------------------------------------------------------------------------|-----------------------------|

| Intel® Xeon® Processor E5-2600 v4 Product Family Datasheet, Volume One:<br>Electrical Volume 1 of 2 | 333809                      |

| Intel® Xeon® Processor E5 v4 Product Family Datasheet Volume 2: Registers                           | 333810                      |

| Intel® Xeon® Processor E5 v4 Product Family Thermal Mechanical Specification and Design Guide       | 333812                      |

| Document Title                                                                                                                                                                                                                                                                                                                                                                              | Document Number/<br>Location                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| AP-485, Intel <sup>®</sup> Processor Identification Utility and the CPUID Instruction                                                                                                                                                                                                                                                                                                       | Note 1                                                            |

| Intel <sup>®</sup> Advanced Vector Extensions Programming Reference                                                                                                                                                                                                                                                                                                                         | Note 1                                                            |

| Intel <sup>®</sup> Trusted Execution Technology Server Extensions (LT-SX) BIOS Specification                                                                                                                                                                                                                                                                                                | Note 1                                                            |

| Intel <sup>®</sup> 64 and IA-32 Architecture Software Developer's Manual <sup>1</sup><br>• Volume 1: Basic Architecture<br>• Volume 2A: Instruction Set Reference Manual A-M<br>• Volume 2B: Instruction Set Reference Manual N-Z<br>• Volume 3A: System Programming Guide<br>• Volume 3B: System Programming Guide<br>• A-32 Intel <sup>®</sup> Architecture Optimization Reference Manual | http://www.intel.com/<br>products/processor/<br>manuals/index.htm |

Notes:

1. Contact your Intel representative for the latest revision and order number of this document.

#### Nomenclature

**Errata** are design defects or errors. These may cause the Product Name's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics, such as, core speed, L2 cache size, all notes associated with each S-Spec number.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

**Note:** Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so forth).

## **Identification Information**

### **Component Identification via Programming Interface**

The Intel® Xeon® E5-2600 v4 Processor Product Family Stepping can be identified by the following register contents:

| Reserved | Extended<br>Family <sup>1</sup> | Extended<br>Model <sup>2</sup> | Reserved | Processor<br>Type <sup>3</sup> | Family<br>Code <sup>4</sup> | Model<br>Number <sup>5</sup> | Stepping<br>ID <sup>6</sup> |

|----------|---------------------------------|--------------------------------|----------|--------------------------------|-----------------------------|------------------------------|-----------------------------|

| 31:28    | 27:20                           | 19:16                          | 15:14    | 13:12                          | 11:8                        | 7:4                          | 3:0                         |

|          | 00000000b                       | 0100b                          |          | 00b                            | 0110b                       | 1111b                        | varies per<br>stepping      |

#### Notes:

- The Extended Family, Bits [27:20] are used in conjunction with the Family Code, specified in Bits [11:8], to indicate whether the processor belongs to the Intel386<sup>™</sup>, Intel486<sup>™</sup>, Pentium<sup>®</sup>, Pentium 4, or Intel<sup>®</sup> Core<sup>™</sup> processor family.

- Core™ processor family.

The Extended Model, Bits [19:16] in conjunction with the Model Number, specified in Bits [7:4], are used to identify the model of the processor within the processor's family.

- 3. The Family Code corresponds to Bits [11:8] of the EDX register after RESET, Bits [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register accessible through Boundary Scan.

- 4. The Model Number corresponds to Bits [7:4] of the EDX register after RESET, Bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register accessible through Boundary Scan.

- The Stepping ID in Bits [3:0] indicates the revision number of that model. See Table 1 for the processor stepping ID number in the CPUID information.

When EAX is initialized to a value of '1', the CPUID instruction returns the *Extended Family, Extended Model, Processor Type, Family Code, Model Number and Stepping ID* value in the EAX register. Note that the EDX processor signature value after reset is equivalent to the processor signature output value in the EAX register.

Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with a 2 in the EAX register.

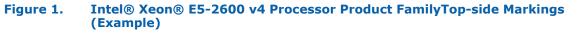

### **Component Marking Information**

For the Intel® Xeon® E5-2600 Processor Product family SKUs see https://ark.intel.com/content/www/us/en/ark/products/series/91287/intel-xeon-processor-e5-v4-family.html.

§

## **Summary Tables of Changes**

The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the Product Name product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables uses the following notations:

### **Codes Used in Summary Tables**

### Stepping

|        | X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|

|        | (No mark)       |                                                                                                               |

|        | or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| Page   |                 |                                                                                                               |

|        | (Page):         | Page location of item in this document.                                                                       |

| Status |                 |                                                                                                               |

|        | Doc:            | Document change or update will be implemented.                                                                |

|        | Plan Fix:       | This erratum may be fixed in a future stepping of the product.                                                |

|        | Fixed:          | This erratum has been previously fixed.                                                                       |

|        | No Fix:         | There are no plans to fix this erratum.                                                                       |

| -      |                 |                                                                                                               |

#### Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

#### Table 1. Integrated Core/Uncore Errata (Sheet 1 of 5)

| Number | Steppings | Status | Errata                                                                                                                                                  |

|--------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | B0/M0/R0  | Status | Ellata                                                                                                                                                  |

| BDF1   | Х         | No Fix | Enabling ISOCH Mode May Cause The System to Hang                                                                                                        |

| BDF2   | Х         | No Fix | PCI BARs in the Home Agent Will Return Non-Zero Values During Enumeration                                                                               |

| BDF3   | Х         | No Fix | PCIe* Header of a Malformed TLP is Logged Incorrectly                                                                                                   |

| BDF4   | Х         | No Fix | A Malformed TLP May Block ECRC Error Logging                                                                                                            |

| BDF5   | х         | No Fix | The System May Hang During an Intel $\ensuremath{\mathbb{R}}$ QuickPath Interconnect (Intel $\ensuremath{\mathbb{R}}$ QPI) Slow to Fast Mode Transition |

| BDF6   | Х         | No Fix | Unexpected Performance Loss When Turbo Disabled                                                                                                         |

| BDF7   | Х         | No Fix | Attempting to Enter ADR May Lead to Unpredictable System Behavior                                                                                       |

| BDF8   | х         | No Fix | Exiting From Package C3 or Package C6 With DDR4-2133 May Lead to Unpredictable System Behavior                                                          |

| Number | Steppings |        | - ·                                                                                                                         |

|--------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| Number | B0/M0/R0  | Status | Errata                                                                                                                      |

| BDF9   | Х         | No Fix | The System May Shut Down Unexpectedly During a Warm Reset                                                                   |

| BDF10  | Х         | No Fix | CAT May Not Behave as Expected                                                                                              |

| BDF11  | х         | No Fix | LBR, BTS, BTM May Report a Wrong Address when an Exception/Interrupt Occurs in 64-bit Mode                                  |

| BDF12  | х         | No Fix | EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change                                    |

| BDF13  | х         | No Fix | MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error                                         |

| BDF14  | Х         | No Fix | LER MSRs May Be Unreliable                                                                                                  |

| BDF15  | Х         | No Fix | MONITOR or CLFLUSH on the Local XAPIC's Address Space Results in Hang                                                       |

| BDF16  | х         | No Fix | $\#\mbox{GP}$ on Segment Selector Descriptor that Straddles Canonical Boundary May Not Provide Correct Exception Error Code |

| BDF17  | Х         | No Fix | FREEZE_WHILE_SMM Does Not Prevent Event From Pending PEBS During SMM                                                        |

| BDF18  | Х         | No Fix | APIC Error "Received Illegal Vector" May be Lost                                                                            |

| BDF19  | х         | No Fix | Performance Monitor Precise Instruction Retired Event May Present Wrong Indications                                         |

| BDF20  | Х         | No Fix | CR0.CD Is Ignored in VMX Operation                                                                                          |

| BDF21  | х         | No Fix | Instruction Fetch May Cause Machine Check if Page Size and Memory Type Was Changed Without Invalidation                     |

| BDF22  | х         | No Fix | Execution of VAESIMC or VAESKEYGENASSIST With An Illegal Value for VEX.vvvv May Produce a $\#\rm NM$ Exception              |

| BDF23  | Х         | No Fix | Interrupt From Local APIC Timer May Not Be Detectable While Being Delivered                                                 |

| BDF24  | Х         | No Fix | Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected                                                      |

| BDF25  | х         | No Fix | DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/POP SS is Followed by a Store or an MMX Instruction             |

| BDF26  | Х         | No Fix | VEX.L is Not Ignored with VCVT*2SI Instructions                                                                             |

| BDF27  | Х         | No Fix | Processor May Livelock During On Demand Clock Modulation                                                                    |

| BDF28  | х         | No Fix | Performance Monitor Events OTHER_ASSISTS.AVX_TO_SSE And OTHER_ASSISTS.SSE_TO_AVX May Over Count                             |

| BDF29  | Х         | No Fix | Performance Monitor Event DSB2MITE_SWITCHES.COUNT May Over Count                                                            |

| BDF30  | Х         | No Fix | Timed MWAIT May Use Deadline of a Previous Execution                                                                        |

| BDF31  | х         | No Fix | IA32_VMX_VMCS_ENUM MSR (48AH) Does Not Properly Report The Highest Index Value Used For VMCS Encoding                       |

| BDF32  | Х         | No Fix | Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Observed                                                      |

| BDF33  | Х         | No Fix | Locked Load Performance Monitoring Events May Under Count                                                                   |

| BDF34  | Х         | No Fix | Transactional Abort May Cause an Incorrect Branch Record                                                                    |

| BDF35  | Х         | No Fix | PMI May be Signaled More Than Once For Performance Monitor Counter Overflow                                                 |

| BDF36  | х         | No Fix | Execution of FXSAVE or FXRSTOR With the VEX Prefix May Produce a #NM Exception                                              |

| BDF37  | Х         | No Fix | VM Exit May Set IA32_EFER.NXE When IA32_MISC_ENABLE Bit 34 is Set to 1                                                      |

| BDF38  | х         | No Fix | A MOV to CR3 When EPT is Enabled May Lead to an Unexpected Page Fault or an Incorrect Page Translation                      |

| BDF39  | Х         | No Fix | Intel® Processor Trace Packet Generation May Stop Sooner Than Expected                                                      |

| BDF40  | Х         | No Fix | PEBS Eventing IP Field May be Incorrect After Not-Taken Branch                                                              |

| BDF41  | х         | No Fix | Reading The Memory Destination of an Instruction That Begins an HLE Transactior May Return The Original Value               |

### Table 1. Integrated Core/Uncore Errata (Sheet 2 of 5)

|        | Steppings |        |                                                                                                                       |

|--------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------|

| Number | B0/M0/R0  | Status | Errata                                                                                                                |

| BDF42  | Х         | Fixed  | Removed                                                                                                               |

| BDF43  | х         | No Fix | Performance Monitoring Event INSTR_RETIRED.ALL May Generate Redundant PEBS Records For an Overflow                    |

| BDF44  | Х         | No Fix | Reset During PECI Transaction May Cause a Machine Check Exception                                                     |

| BDF45  | х         | No Fix | Intel® Processor Trace (Intel® PT) MODE.Exec, PIP, and CBR Packets Are Not Generated as Expected                      |

| BDF46  | Х         | No Fix | Performance Monitor Instructions Retired Event May Not Count Consistently                                             |

| BDF47  | Х         | No Fix | General-Purpose Performance Counters May be Inaccurate with Any Thread                                                |

| BDF48  | Х         | No Fix | An Invalid LBR May Be Recorded Following a Transactional Abort                                                        |

| BDF49  | х         | No Fix | Executing an RSM Instruction With Intel $\circledast$ Processor Trace Enabled Will Signal a #GP                       |

| BDF50  | Х         | No Fix | Intel® Processor Trace PIP May be Unexpectedly Generated                                                              |

| BDF51  | Х         | No Fix | Processor Core Ratio Changes While in Probe Mode May Result in a Hang                                                 |

| BDF52  | Х         | No Fix | Processor Does Not Check IRTE Reserved Bits                                                                           |

| BDF53  | х         | No Fix | PCIe* TPH Request Capability Structure Incorrectly Advertises Device Specific<br>Mode as Supported                    |

| BDF54  | Х         | No Fix | Package C3 State or Deeper May Lead to a Reset                                                                        |

| BDF55  | Х         | No Fix | VMX-Preemption Timer May Stop Operating When ACC is Enabled                                                           |

| BDF56  | х         | No Fix | Intel® Advanced Vector Extensions (Intel® AVX) Workloads May Exceed ICCMAX Limits                                     |

| BDF57  | Х         | No Fix | Writing MSR_ERROR_CONTROL May Cause a #GP                                                                             |

| BDF58  | Х         | No Fix | Enabling ACC in VMX Non-Root Operation May Cause System Instability                                                   |

| BDF59  | Х         | No Fix | A Spurious Patrol Scrub Error May be Logged                                                                           |

| BDF60  | х         | No Fix | Performance Monitoring Counters May Produce Incorrect Results for<br>BR_INST_RETIRED Event on Logical Processor.      |

| BDF61  | Х         | No Fix | Removed                                                                                                               |

| BDF62  | Х         | No Fix | Processor Instability May Occur When Using The PECI RdIAMSR Command                                                   |

| BDF63  | Х         | No Fix | A #VE May Not Invalidate Cached Translation Information                                                               |

| BDF64  | х         | No Fix | Package C-state Transitions While Inband PECI Accesses Are in Progress May Cause Performance Degradation              |

| BDF65  | х         | No Fix | Attempting Concurrent Enabling of Intel® Processor Trace (Intel® PT) With LBR, BTS, or BTM Results in a $\#\mbox{GP}$ |

| BDF66  | х         | No Fix | A DDR4 C/A Parity Error in Lockstep Mode May Result in a Spurious Uncorrectable Error                                 |

| BDF67  | Х         | No Fix | Cores May be Unable to Reach Maximum Turbo Frequency                                                                  |

| BDF68  | Х         | No Fix | PEBS Record May Be Generated After Being Disabled                                                                     |

| BDF69  | Х         | No Fix | Software Using Intel® TSX May Behave Unpredictably                                                                    |

| BDF70  | х         | No Fix | Some E5-1607V4 And E5-1603V4 Parts Will Incorrectly Report Support For DDR4-2400                                      |

| BDF71  | х         | No Fix | PROCHOT# Assertion During Warm Reset May Cause Persistent Performance Reduction                                       |

| BDF72  | Х         | No Fix | Data Breakpoint Coincident With a Machine Check Exception May be Lost                                                 |

| BDF73  | х         | No Fix | Internal Parity Errors May Incorrectly Report Overflow in the IA32_MC0_STATUS MSR                                     |

| BDF74  | Х         | No Fix | Incorrect VMCS Used for PML-Index field on VMX Transitions Into and Out of SMM                                        |

### Table 1. Integrated Core/Uncore Errata (Sheet 3 of 5)

|        | Steppings |        |                                                                                                                            |

|--------|-----------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Number | B0/M0/R0  | Status | Errata                                                                                                                     |

| BDF75  | Х         | No Fix | Certain Microcode Updates May Result in Incorrect Throttling Causing Reduced System Performance                            |

| BDF76  | х         | No Fix | An Intel® Hyper-Threading Technology Enabled Processor May Exhibit Internal Parity Errors or Unpredictable System Behavior |

| BDF77  | х         | No Fix | Inband PECI Concurrent With OS Patch Load May Result in Incorrect Throttling<br>Causing Reduced System Performance         |

| BDF78  | Х         | No Fix | Writing The IIO_LLC_WAYS MSR Results in an Incorrect Value                                                                 |

| BDF79  | Х         | No Fix | Turbo May Be Delayed After Exiting C6 When Using HWP                                                                       |

| BDF80  | Х         | No Fix | IA32_MC4_STATUS.VAL May be Incorrectly Cleared by Warm Reset                                                               |

| BDF81  | Х         | No Fix | Interrupt Remapping May Lead to a System Hang                                                                              |

| BDF82  | R0        | No Fix | MEM_HOT_C23_N DIMM Temperature Reporting Does Not Function Correctly                                                       |

| BDF83  | Х         | No Fix | Bi-Directional PCIe* Posted Transactions May Lead to System Hang                                                           |

| BDF84  | х         | No Fix | Excessive Uncorrected and Corrected Memory Errors May Occur Following S3<br>Resume or Warm Reset                           |

| BDF85  | х         | No Fix | Writing MSR_LASTBRANCH_x_FROM_IP May #GP When Intel® TSX is Not<br>Supported                                               |

| BDF86  | Х         | No Fix | PCIe* Ports May Incorrectly Detect a Receiver                                                                              |

| BDF87  | Х         | No Fix | Some DRAM And L3 Cache Performance Monitoring Events May Undercount                                                        |

| BDF88  | х         | No Fix | APIC Timer Interrupt May Not be Generated at The Correct Time In TSC-Deadline Mode                                         |

| BDF89  | х         | No Fix | Loading Microcode Updates or Executing an Authenticated Code Module May Resul<br>in a System Hang                          |

| BDF90  | Х         | No Fix | NVDIMM Data May Not be Preserved Correctly on Power Loss or ADR Activation                                                 |

| BDF91  | х         | No Fix | Link Down Events behind PCIe Device connected to CPU Root Ports Can Cause CTC > 50ms on other Root Ports                   |

| BDF92  | Х         | No Fix | Removed                                                                                                                    |

| BDF93  | Х         | No Fix | Reads From MSR_LER_TO_LIP May Not Return a Canonical Address                                                               |

| BDF94  | Х         | No Fix | Processor May Hang After Multiple Microcode Updates Loaded                                                                 |

| BDF95  | х         | No Fix | In eMCA2 Mode, When The Retirement Watchdog Timeout Occurs CATERR# May be Asserted                                         |

| BDF96  | х         | No Fix | Systems That Enable Both OSB And IODC May Exhibit Unexpected System Behavior                                               |

| BDF97  | Х         | No Fix | VCVTPS2PH To Memory May Update MXCSR in The Case of a Fault on The Store                                                   |

| BDF98  | Х         | No Fix | Writing the CMCI_DISABLE bit in the ERROR_CONTROL MSR will #GP Fault                                                       |

| BDF99  | Х         | No Fix | System May Hang When Operating at High Temperatures                                                                        |

| BDF100 | Х         | No Fix | Using Intel® TSX Instructions May Lead to Unpredictable System Behavior                                                    |

| BDF101 | Х         | No Fix | The System May Hang When Exiting package C6 State                                                                          |

| BDF102 | Х         | No Fix | Intel® MBM Counters May Report System Memory Bandwidth Incorrectly                                                         |

| BDF103 | Х         | No Fix | When Operating at Maximum Uncore Frequency, The Processor May Hang                                                         |

| BDF104 | Х         | No Fix | A Pending Fixed Interrupt May Be Dispatched Before an Interrupt of The Same<br>Priority Completes                          |

| BDF105 | Х         | No Fix | Overflow Flag in IA32_MC0_STATUS MSR May be Incorrectly Set                                                                |

| BDF106 | Х         | No Fix | PECI RdAMSR() to Non-existent MSR Might Result in IERR                                                                     |

### Table 1. Integrated Core/Uncore Errata (Sheet 4 of 5)

|        | Number   | Steppings | Status | Errata                                                                  |

|--------|----------|-----------|--------|-------------------------------------------------------------------------|

| Number | B0/M0/R0 | Status    | Eilata |                                                                         |

|        | BDF107   | Х         | No Fix | System logs a message channel timeout in MCA Bank                       |

|        | BDF108.  | Х         | No Fix | Retried PECI PCIConfigLocal Register Accesses May Not Operate Correctly |

|        | BDF109.  | Х         | No Fix | Debug Exceptions May Be Lost in The Case Of Machine Check Exception     |

#### Table 1. Integrated Core/Uncore Errata (Sheet 5 of 5)

Т

### **Specification Changes**

| Number | SPECIFICATION CHANGES                                |  |

|--------|------------------------------------------------------|--|

| 1      | None for this revision of this specification update. |  |

### **Specification Clarifications**

| No. | SPECIFICATION CLARIFICATIONS                         |

|-----|------------------------------------------------------|

| 1   | None for this revision of this specification update. |

### **Documentation Changes**

| No. | DOCUMENTATION CHANGES                                |

|-----|------------------------------------------------------|

| 1   | None for this revision of this specification update. |

## **Integrated Core/Uncore Errata**

#### **BDF1** Enabling ISOCH Mode May Cause The System to Hang When ISOCH (Isochronous) operation is enabled within BIOS, the system may hang Problem: and fail to boot. Implication: Due to this erratum, the system may hang and fail to boot. Workaround: It is possible for the BIOS to contain a workaround for this erratum. Status: For the Steppings affected, see the Summary Tables of Changes. **BDF2** PCI BARs in the Home Agent Will Return Non-Zero Values During Enumeration During system initialization the Operating System may access the standard PCI BARs Problem: (Base Address Registers). Due to this erratum, accesses to the Home Agent BAR registers (Bus 1; Device 18; Function 0,4; Offsets 0x14-0x24) will return non-zero values. The operating system may issue a warning. Intel has not observed any functional Implication: failures due to this erratum. Workaround: None identified. For the Steppings affected, see the Summary Tables of Changes. Status: BDF3 PCIe\* Header of a Malformed TLP is Logged Incorrectly If a PCIe port receives a malformed TLP (Transaction Layer Packet), an error is logged Problem: in the UNCERRSTS register (Device 0; Function 0; Offset 14CH and Device 2-3; Function 0-3; Offset 14CH). Due to this erratum, the header of the malformed TLP is logged incorrectly in the HDRLOG register (Device 0; Function 0; Offset 164H and Device 2-3; Function 0-3; Offset 164H). Implication: The PCIe header of a malformed TLP is not logged correctly. Workaround: None identified. For the Steppings affected, see the Summary Tables of Changes. Status: A Malformed TLP May Block ECRC Error Logging **BDF4** If a PCIe\* port receives a Malformed TLP that also would generate an ECRC Check Problem: Failed error, it should report a Malformed TLP error. When Malformed TLP errors are masked, the processor should report the lower-precedence ECRC Check Failed error but, due to this erratum, it does not. Implication: Software that relies upon ECRC Check Failed error indication may not behave as expected. Workaround: None identified. Status: For the Steppings affected, see the Summary Tables of Changes. **BDF5** The System May Hang During an Intel® QuickPath Interconnect (Intel® OPI) Slow to Fast Mode Transition Problem: During an Intel QPI slow mode to fast mode transition, the LL STATUS field of the QPIPCSTS register (Bus 0; Device 8,9,10; Function 0; Offset 0xc0) may not be correctly updated to reflect link readiness. The system may hang waiting for the QPIPCSTS.LL\_STATUS to update. Implication: Workaround: It is possible for the BIOS to contain a workaround for this erratum. For the Steppings affected, see the Summary Tables of Changes. Status:

| BDF6         | Unexpected Performance Loss When Turbo Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | When Intel Turbo Boost Technology is disabled by IA32_MISC_ENABLES MSR (416H) TURBO_MODE_DISABLE bit 38, the Ring operating frequency may be below P1 operating frequency.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Implication: | Processor performance may be below expectations for P1 operating frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Workaround:  | It is possible for the BIOS to contain a workaround for this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BDF7         | Attempting to Enter ADR May Lead to Unpredictable System Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Problem:     | Due to this erratum, an attempt to transition the memory subsystem to ADR (Asynchronous DRAM Self Refresh) mode may fail.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Implication: | This erratum may lead to unpredictable system behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround:  | It is possible for the BIOS to contain a workaround for this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BDF8         | Exiting From Package C3 or Package C6 With DDR4-2133 May Lead to Unpredictable System Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Problem:     | Due to this erratum, with DDR4-2133 memory, exiting from PC3 (package C3) or PC6 (package C6) state may lead to unpredictable system behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Implication: | This erratum may lead to unpredictable system behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround:  | It is possible for the BIOS to contain a workaround for this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BDF9         | The System May Shut Down Unexpectedly During a Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Problem:     | Certain complex internal timing conditions present when a warm reset is requested can<br>prevent the orderly completion of in-flight transactions. It is possible under these<br>conditions that the warm reset will fail and trigger a full system shutdown.                                                                                                                                                                                                                                                                                                                  |

| Implication: | When this erratum occurs, the system will shut down and all machine check error logs will be lost.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Workaround:  | It is possible for the BIOS to contain a workaround for this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BDF10        | CAT May Not Behave as Expected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Problem:     | Due to this erratum, CAT (Cache Allocation Technology) way enforcement may not behave as configured.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Implication: | When this erratum occurs, cache quality of service guarantees may not be met.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Workaround:  | It is possible for the BIOS to contain a workaround for this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BDF11        | LBR, BTS, BTM May Report a Wrong Address when an Exception/<br>Interrupt Occurs in 64-bit Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Problem:     | An exception/interrupt event should be transparent to the LBR (Last Branch Record),<br>BTS (Branch Trace Store) and BTM (Branch Trace Message) mechanisms. However,<br>during a specific boundary condition where the exception/interrupt occurs right after<br>the execution of an instruction at the lower canonical boundary (0x00007FFFFFFFFFF)<br>in 64-bit mode, the LBR return registers will save a wrong return address with bits 63<br>to 48 incorrectly sign extended to all 1's. Subsequent BTS and BTM operations which<br>report the LBR will also be incorrect. |

| Implication: | LBR, BTS and BTM may report incorrect information in the event of an exception/interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Workaround: None identified.

Status: For the Steppings affected, see the Summary Tables of Changes.

## **BDF12 EFLAGS** Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change

- Problem: EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change

- Problem: This erratum is regarding the case where paging structures are modified to change a linear address from writable to non-writable without software performing an appropriate TLB invalidation. When a subsequent access to that address by a specific instruction (ADD, AND, BTC, BTR, BTS, CMPXCHG, DEC, INC, NEG, NOT, OR, ROL/ROR, SAL/SAR/SHL/SHR, SHLD, SHRD, SUB, XOR, and XADD) causes a page fault or an EPT-induced VM exit, the value saved for EFLAGS may incorrectly contain the arithmetic flag values that the EFLAGS register would have held had the instruction completed without fault or VM exit. For page faults, this can occur even if the fault causes a VM exit or if its delivery causes a nested fault.

- Implication: None identified. Although the EFLAGS value saved by an affected event (a page fault or an EPT-induced VM exit) may contain incorrect arithmetic flag values, Intel has not identified software that is affected by this erratum. This erratum will have no further effects once the original instruction is restarted because the instruction will produce the same results as if it had initially completed without fault or VM exit.

- Workaround: If the handler of the affected events inspects the arithmetic portion of the saved EFLAGS value, then system software should perform a synchronized paging structure modification and TLB invalidation.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF13 MCi\_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error

- Problem: A single Data Translation Look Aside Buffer (DTLB) error can incorrectly set the Overflow (bit [62]) in the MCi\_Status register. A DTLB error is indicated by MCA error code (bits [15:0]) appearing as binary value, 000x 0000 0001 0100, in the MCi\_Status register.

- Implication: Due to this erratum, the Overflow bit in the MCi\_Status register may not be an accurate indication of multiple occurrences of DTLB errors. There is no other impact to normal processor functionality.

- Workaround: None identified.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF14 LER MSRs May Be Unreliable

Problem: Due to certain internal processor events, updates to the LER (Last Exception Record) MSRs, MSR\_LER\_FROM\_LIP (1DDH) and MSR\_LER\_TO\_LIP (1DEH), may happen when no update was expected.

Implication: The values of the LER MSRs may be unreliable.

- Workaround: None Identified.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

## BDF15 MONITOR or CLFLUSH on the Local XAPIC's Address Space Results in Hang

- Problem: If the target linear address range for a MONITOR or CLFLUSH is mapped to the local xAPIC's address space, the processor will hang.

- Implication: When this erratum occurs, the processor will hang. The local xAPIC's address space must be uncached. The MONITOR instruction only functions correctly if the specified linear address range is of the type write-back. CLFLUSH flushes data from the cache.

Intel has not observed this erratum with any commercially available software.

Workaround: Do not execute MONITOR or CLFLUSH instructions on the local xAPIC address space.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF16 #GP on Segment Selector Descriptor that Straddles Canonical Boundary May Not Provide Correct Exception Error Code

Problem: During a #GP (General Protection Exception), the processor pushes an error code on to the exception handler's stack. If the segment selector descriptor straddles the canonical boundary, the error code pushed onto the stack may be incorrect.

Implication: An incorrect error code may be pushed onto the stack. Intel has not observed this erratum with any commercially available software.

Workaround: None identified.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF17 FREEZE\_WHILE\_SMM Does Not Prevent Event From Pending PEBS During SMM

- Problem: In general, a PEBS record should be generated on the first count of the event after the counter has overflowed. However, IA32\_DEBUGCTL\_MSR.FREEZE\_WHILE\_SMM (MSR 1D9H, bit [14]) prevents performance counters from counting during SMM (System Management Mode). Due to this erratum, if

- 1. A performance counter overflowed before an SMI

- 2. A PEBS record has not yet been generated because another count of the event has not occurred.

- The monitored event occurs during SMM then a PEBS record will be saved after the next RSM instruction. When FREEZE\_WHILE\_SMM is set, a PEBS should not be generated until the event occurs outside of SMM.

- Implication: A PEBS record may be saved after an RSM instruction due to the associated performance counter detecting the monitored event during SMM; even when FREEZE\_WHILE\_SMM is set.

- Workaround: None identified.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF18 APIC Error "Received Illegal Vector" May be Lost

- Problem: APIC (Advanced Programmable Interrupt Controller) may not update the ESR (Error Status Register) flag Received Illegal Vector bit [6] properly when an illegal vector error is received on the same internal clock that the ESR is being written (as part of the write-read ESR access flow). The corresponding error interrupt will also not be generated for this case.

- Implication: Due to this erratum, an incoming illegal vector error may not be logged into ESR properly and may not generate an error interrupt.

- Workaround: None identified.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF19 Performance Monitor Precise Instruction Retired Event May Present Wrong Indications

Problem: When the PDIR (Precise Distribution for Instructions Retired) mechanism is activated (INST\_RETIRED.ALL (event COH, umask value 00H) on Counter 1 programmed in PEBS mode), the processor may return wrong PEBS/PMI interrupts and/or incorrect counter values if the counter is reset with a SAV below 100 (Sample-After-Value is the counter reset value software programs in MSR IA32\_PMC1[47:0] in order to control interrupt frequency).

Implication: Due to this erratum, when using low SAV values, the program may get incorrect PEBS or PMI interrupts and/or an invalid counter state.

Workaround: The sampling driver should avoid using SAV<100.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF20 CR0.CD Is Ignored in VMX Operation

Problem: If CR0.CD=1, the MTRRs and PAT should be ignored and the UC memory type should be used for all memory accesses. Due to this erratum, a logical processor in VMX operation will operate as if CR0.CD=0 even if that bit is set to 1.

Implication: Algorithms that rely on cache disabling may not function properly in VMX operation.

Workaround: Algorithms that rely on cache disabling should not be executed in VMX root operation.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### **BDF21** Instruction Fetch May Cause Machine Check if Page Size and Memory Type Was Changed Without Invalidation

- Problem: This erratum may cause a machine-check error (IA32\_MCi\_STATUS.MCACOD=0150H) on the fetch of an instruction that crosses a 4-KByte address boundary. It applies only if (1) the 4-KByte linear region on which the instruction begins is originally translated using a 4-KByte page with the WB memory type; (2) the paging structures are later modified so that linear region is translated using a large page (2-MByte, 4-MByte, or 1-GByte) with the UC memory type; and (3) the instruction fetch occurs after the paging structure modification but before software invalidates any TLB entries for the linear region.

- Implication: Due to this erratum an unexpected machine check with error code 0150H may occur, possibly resulting in a shutdown. Intel has not observed this erratum with any commercially available software.

- Workaround: Software should not write to a paging-structure entry in a way that would change, for any linear address, both the page size and the memory type. It can instead use the following algorithm: first clear the P flag in the relevant paging-structure entry (for example, PDE); then invalidate any translations for the affected linear addresses; and then modify the relevant paging-structure entry to set the P flag and establish the new page size and memory type.

- Status: For the Steppings affected, see the Summary Tables of Changes.

### BDF22 Execution of VAESIMC or VAESKEYGENASSIST With An Illegal Value for VEX.vvvv May Produce a #NM Exception

- Problem: The VAESIMC and VAESKEYGENASSIST instructions should produce a #UD (Invalid-Opcode) exception if the value of the vvvv field in the VEX prefix is not 1111b. Due to this erratum, if CR0.TS is "1", the processor may instead produce a #NM (Device-Not-Available) exception.

- Implication: Due to this erratum, some undefined instruction encodings may produce a #NM instead of a #UD exception.

- Workaround: Software should always set the vvvv field of the VEX prefix to 1111b for instances of the VAESIMC and VAESKEYGENASSIST instructions.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF23 Interrupt From Local APIC Timer May Not Be Detectable While Being Delivered

Problem: If the local-APIC timer's CCR (current-count register) is 0, software should be able to determine whether a previously generated timer interrupt is being delivered by first reading the delivery-status bit in the LVT timer register and then reading the bit in the IRR (interrupt-request register) corresponding to the vector in the LVT timer register. If both values are read as 0, no timer interrupt should be in the process of being delivered. Due to this erratum, a timer interrupt may be delivered even if the CCR is 0

and the LVT and IRR bits are read as 0. This can occur only if the DCR (Divide Configuration Register) is greater than or equal to 4. The erratum does not occur if software writes zero to the Initial Count Register before reading the LVT and IRR bits.

- Implication: Software that relies on reads of the LVT and IRR bits to determine whether a timer interrupt is being delivered may not operate properly.

- Workaround: Software that uses the local-APIC timer must be prepared to handle the timer interrupts, even those that would not be expected based on reading CCR and the LVT and IRR bits; alternatively, software can avoid the problem by writing zero to the Initial Count Register before reading the LVT and IRR bits.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF24 Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected

Problem: x87 instructions that trigger #MF normally service interrupts before the #MF. Due to this erratum, if an instruction that triggers #MF is executed while Enhanced Intel SpeedStep® Technology transitions, Intel® Turbo Boost Technology transitions, or Thermal Monitor events occur, the pending #MF may be signaled before pending interrupts are serviced.

Implication: Software may observe #MF being-signaled before pending interrupts are serviced.

- Workaround: None identified.

- Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF25 DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/POP SS is Followed by a Store or an MMX Instruction

- Problem: Normally, data breakpoints matches that occur on a MOV SS, r/m or POP SS will not cause a debug exception immediately after MOV/POP SS but will be delayed until the instruction boundary following the next instruction is reached. After the debug exception occurs, DR6.B0-B3 bits will contain information about data breakpoints matched during the MOV/POP SS as well as breakpoints detected by the following instruction. Due to this erratum, DR6.B0-B3 bits may not contain information about data breakpoints matched during the MOV/POP SS when the following instruction is either an MMX instruction that uses a memory addressing mode with an index or a store instruction.

- Implication: When this erratum occurs, DR6 may not contain information about all breakpoints matched. This erratum will not be observed under the recommended usage of the MOV SS,r/m or POP SS instructions (that is, following them only with an instruction that writes (E/R)SP).

Workaround: None identified.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF26 VEX.L is Not Ignored with VCVT\*2SI Instructions

- Problem: The VEX.L bit should be ignored for the VCVTSS2SI, VCVTSD2SI, VCVTTSS2SI, and VCVTTSD2SI instructions, however due to this erratum the VEX.L bit is not ignored and will cause a #UD.

- Implication: Unexpected #UDs will be seen when the VEX.L bit is set to 1 with VCVTSS2SI, VCVTSD2SI, VCVTSS2SI, and VCVTSD2SI instructions.

- Workaround: Software should ensure that the VEX.L bit is set to 0 for all scalar instructions.

Status: For the Steppings affected, see the Summary Tables of Changes.

#### BDF27 Processor May Livelock During On Demand Clock Modulation

Problem: The processor may livelock when (1) a processor thread has enabled on demand clock modulation via bit 4 of the IA32\_CLOCK\_MODULATION MSR (19AH) and the clock modulation duty cycle is set to 12.5% (02H in bits 3:0 of the same MSR), and (2) the

|              | other processor thread does not have on demand clock modulation enabled and that thread is executing a stream of instructions with the lock prefix that either split a cacheline or access UC memory.                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implication: | Program execution may stall on both threads of the core subject to this erratum.                                                                                                                                                                                                                                                   |

| Workaround:  | This erratum will not occur if clock modulation is enabled on all threads when using on demand clock modulation or if the duty cycle programmed in the IA32_CLOCK_MODULATION MSR is 18.75% or higher.                                                                                                                              |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                     |

| BDF28        | Performance Monitor Events OTHER_ASSISTS.AVX_TO_SSE And<br>OTHER_ASSISTS.SSE_TO_AVX May Over Count                                                                                                                                                                                                                                 |

| Problem:     | The Performance Monitor events OTHER_ASSISTS.AVX_TO_SSE (Event C1H; Umask 08H) and OTHER_ASSISTS.SSE_TO_AVX (Event C1H; Umask 10H) incorrectly increment and over count when an HLE (Hardware Lock Elision) abort occurs.                                                                                                          |

| Implication: | The Performance Monitor Events OTHER_ASSISTS.AVX_TO_SSE And<br>OTHER_ASSISTS.SSE_TO_AVX may over count.                                                                                                                                                                                                                            |

| Workaround:  | None identified.                                                                                                                                                                                                                                                                                                                   |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                     |

| BDF29        | Performance Monitor Event DSB2MITE_SWITCHES.COUNT May Over<br>Count                                                                                                                                                                                                                                                                |

| Problem:     | The Performance Monitor Event DSB2MITE_SWITCHES.COUNT (Event ABH; Umask 01H) should count the number of DSB (Decode Stream Buffer) to MITE (Macro Instruction Translation Engine) switches. Due to this erratum, the DSB2MITE_SWITCHES.COUNT event will count speculative switches and cause the count to be higher than expected. |

| Implication: | The Performance Monitor Event DSB2MITE_SWITCHES.COUNT may report count higher than expected.                                                                                                                                                                                                                                       |

| Workaround:  | None identified.                                                                                                                                                                                                                                                                                                                   |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                     |

| BDF30        | Timed MWAIT May Use Deadline of a Previous Execution                                                                                                                                                                                                                                                                               |

| Problem:     | A timed MWAIT instruction specifies a TSC deadline for execution resumption. If a wake<br>event causes execution to resume before the deadline is reached, a subsequent timed<br>MWAIT instruction may incorrectly use the deadline of the previous timed MWAIT when<br>that previous deadline is earlier than the new one.        |

| Implication: | A timed MWAIT may end earlier than expected.                                                                                                                                                                                                                                                                                       |

| Workaround:  | It is possible for the BIOS to contain a workaround for this erratum.                                                                                                                                                                                                                                                              |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                     |

| BDF31        | IA32_VMX_VMCS_ENUM MSR (48AH) Does Not Properly Report The<br>Highest Index Value Used For VMCS Encoding                                                                                                                                                                                                                           |

| Problem:     | IA32_VMX_VMCS_ENUM MSR (48AH) bits 9:1 report the highest index value used for any VMCS encoding. Due to this erratum, the value 21 is returned in bits 9:1 although there is a VMCS field whose encoding uses the index value 23.                                                                                                 |

| Implication: | Software that uses the value reported in IA32_VMX_VMCS_ENUM[9:1] to read and write all VMCS fields may omit one field.                                                                                                                                                                                                             |

| Workaround:  | None identified.                                                                                                                                                                                                                                                                                                                   |

| Status:      | For the Steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                     |

|              |                                                                                                                                                                                                                                                                                                                                    |

#### BDF32 Incorrect FROM\_IP Value For an RTM Abort in BTM or BTS May be Observed

- Problem: During RTM (Restricted Transactional Memory) operation when branch tracing is enabled using BTM (Branch Trace Message) or BTS (Branch Trace Store), the incorrect EIP value (From\_IP pointer) may be observed for an RTM abort.

- Implication: Due to this erratum, the From\_IP pointer may be the same as that of the immediately preceding taken branch.

- Workaround: None identified.

Status: For the Steppings affected, see the *Summary Tables of Changes*.

#### BDF33 Locked Load Performance Monitoring Events May Under Count