# **Intel® Firmware Support Package**

**External Architecture Specification v2.1**

May 2019

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

${}^{*}\mathrm{Other}$  names and brands may be claimed as the property of others.

Copyright  $\ensuremath{\text{@}}$  2019, Intel Corporation. All rights reserved.

## **Contents**

| 1 | Introdu    | uction         |                                           | 9        |

|---|------------|----------------|-------------------------------------------|----------|

|   | 1.1        |                |                                           |          |

|   | 1.2        |                | Audience                                  |          |

|   | 1.3        |                | Documents                                 |          |

|   | 1.4        | Terminol       | ogy                                       | 10       |

| 2 | Intel®     | FSP Over       | view                                      | 11       |

|   | 2.1        |                | hilosophy                                 |          |

|   | 2.2        |                | l Overview                                |          |

|   |            | 2.2.1          | Data Structure Descriptions               | 11       |

| 3 | Intel®     | FSP Integ      | ration                                    | 12       |

|   | 3.1        | Intel® F       | SP Distribution Package                   | 12       |

| 4 | Intel®     | FSP Binar      | y Format                                  | 13       |

| T | Interior   | 4.1.1          | FSP-T: Temporary RAM initialization phase |          |

|   |            | 4.1.1          | FSP-M: Memory initialization phase        |          |

|   |            | 4.1.3          | FSP-S: Silicon initialization phase       |          |

|   |            | 4.1.4          | OEM Components (FSP-O)                    | 14       |

|   | 4.2        | Intel® F       | SP Component Identification               |          |

|   |            | 4.2.1          | Intel® FSP Image ID and Revision          |          |

|   |            | 4.2.2          | Intel® FSP Component Layout               | 14       |

| 5 | Intel®     | FSP Infor      | mation tables                             | 16       |

|   |            | 5.1.1          | FSP_INFO_HEADER                           | 16       |

|   |            | 5.1.2          | FSP_INFO_EXTENDED_HEADER                  |          |

|   |            | 5.1.3          | Locating FSP_INFO_HEADER                  |          |

|   |            | 5.1.4<br>5.1.5 | FSP Description File                      |          |

|   |            | 3.1.3          | 5.1.5.1 Example                           |          |

| _ |            |                | ·                                         |          |

| 6 |            |                | guration Data                             |          |

|   | 6.1        |                | ndard Fields                              |          |

|   |            | 6.1.1          | FSP-T UPD Structure                       |          |

|   |            | 6.1.2<br>6.1.3 | FSP-M UPD Structure                       |          |

|   |            |                |                                           |          |

| 7 |            |                |                                           |          |

|   | 7.1        |                | Boot Flow                                 |          |

|   |            |                | Boot Flow Description                     |          |

|   | 7.2        | •              | Mode Boot Flow                            |          |

|   |            | 7.2.1<br>7.2.2 | High Level Overview                       |          |

|   |            | 7.2.2          | Alternate Boot Flow Description           |          |

| 0 | T          |                | •                                         |          |

| 8 |            |                | Mode Interface                            |          |

|   | 8.1        | •              | nt Invocation Environment                 |          |

|   | 8.2        |                | ucture Convention                         |          |

|   | 8.3<br>8.4 | -              | nt Calling Convention                     | 34<br>34 |

|   | 0.4        |                | IGUD LUUE                                 |          |

#### Introduction

|   | 8.5    |          | TempRamInit API 3 |                                   |    |  |

|---|--------|----------|-------------------|-----------------------------------|----|--|

|   |        | 8.5.1    | Prototype         | e                                 | 36 |  |

|   |        | 8.5.2    | Paramete          | ers                               | 36 |  |

|   |        | 8.5.3    | Return Va         | alues                             | 36 |  |

|   |        | 8.5.4    | Description       | on                                | 36 |  |

|   | 8.6    | FspMen   |                   | I                                 |    |  |

|   |        | 8.6.1    |                   | e                                 |    |  |

|   |        | 8.6.2    |                   | ers                               |    |  |

|   |        | 8.6.3    |                   | alues                             |    |  |

|   |        | 8.6.4    |                   | on                                | _  |  |

|   | 8.7    |          | •                 |                                   |    |  |

|   | 0.7    | •        |                   |                                   |    |  |

|   |        | 8.7.1    |                   | e                                 |    |  |

|   |        | 8.7.2    |                   | ers                               |    |  |

|   |        | 8.7.3    |                   | alues                             |    |  |

|   |        | 8.7.4    | •                 | on                                |    |  |

|   | 8.8    | FspSilic |                   |                                   |    |  |

|   |        | 8.8.1    |                   | e                                 |    |  |

|   |        | 8.8.2    | Paramete          | ers                               | 40 |  |

|   |        | 8.8.3    | Return Va         | alues                             | 41 |  |

|   |        | 8.8.4    | Description       | on                                | 41 |  |

|   | 8.9    | NotifyP  | hase API          |                                   | 41 |  |

|   |        | 8.9.1    | Prototype         | <del>2</del>                      | 42 |  |

|   |        | 8.9.2    | , ,               | ers                               |    |  |

|   |        | 8.9.3    |                   | Definitions                       |    |  |

|   |        | 8.9.4    |                   | alues                             |    |  |

|   |        | 8.9.5    |                   | on                                |    |  |

|   |        |          | •                 |                                   |    |  |

| 9 | Intel® | FSP Dis  | patch Mode        | Interface                         | 45 |  |

|   | 9.1    | Dispato  | h Mode Des        | sign                              | 45 |  |

|   | 9.2    | •        |                   | ments                             |    |  |

|   | 9.3    |          | •                 | se Requirements                   |    |  |

|   |        |          |                   | ·                                 |    |  |

|   | 9.4    | -        |                   |                                   |    |  |

|   |        | 9.4.1    |                   | mInit API                         |    |  |

|   |        | 9.4.2    |                   | Core Firmware Volume Location PPI |    |  |

|   |        | 9.4.3    |                   | porary RAM Exit PPI               |    |  |

|   |        |          | 9.4.3.1           | Summary                           |    |  |

|   |        |          | 9.4.3.2           | GUID                              |    |  |

|   |        |          | 9.4.3.3           | Prototype                         |    |  |

|   |        |          | 9.4.3.4           | Parameters                        |    |  |

|   |        |          | 9.4.3.5           | Description                       |    |  |

|   |        | 9.4.4    | _                 | P_RAM_EXIT_PPI.TempRamExit ()     |    |  |

|   |        |          | 9.4.4.1           | Summary                           |    |  |

|   |        |          | 9.4.4.2           | Prototype                         |    |  |

|   |        |          | 9.4.4.3           | Parameters                        | 49 |  |

|   |        |          | 9.4.4.4           | Description                       | 49 |  |

|   |        |          | 9.4.4.5           | Return Values                     |    |  |

|   |        | 9.4.5    | FSP-M Ar          | chitectural Configuration PPI     | 50 |  |

|   |        |          | 9.4.5.1           | Summary                           |    |  |

|   |        |          | 9.4.5.2           | GUID                              |    |  |

|   |        |          | 9.4.5.3           | Prototype                         |    |  |

|   |        |          | 9.4.5.4           | Parameters                        |    |  |

|   |        |          | 9.4.5.5           | Description                       |    |  |

|   |        | 9.4.6    |                   | r Information                     |    |  |

|   |        | 21 110   | 9.4.6.1           | Summary                           |    |  |

|   |        |          |                   |                                   |    |  |

#### Introduction

|    |         | 9.4.7      | 9.4.6.2<br>9.4.6.3<br>9.4.6.4<br>9.4.6.5<br>FSP Debu | GUID Prototype Parameters Description Ig Messages | 51<br>51<br>51 |

|----|---------|------------|------------------------------------------------------|---------------------------------------------------|----------------|

| 10 | Intel®  | FSP Outp   | out                                                  |                                                   | 53             |

|    | 10.1    | FSP RES    | SERVED M                                             | EMORY_RESOURCE_HOB                                | 54             |

|    | 10.2    | FSP_NO     | N_VOLATIL                                            | LE_STORAGE_HOB                                    | 54             |

|    | 10.3    | FSP_BO     | OTLOADER                                             | _TOLUM_HOB                                        | 55             |

|    | 10.4    |            | _                                                    | S_INFO_HOB                                        |                |

|    | 10.5    |            |                                                      | S_DEVICE_INFO_HOB                                 |                |

|    | 10.6    | FSP_ERF    | ROR_INFO_                                            | _HOB                                              | 56             |

| 11 | Other I | Host Boot  | Loader Co                                            | nsiderations                                      | 58             |

|    | 11.1    | ACPI       |                                                      |                                                   | 58             |

|    | 11.2    |            |                                                      |                                                   |                |

|    | 11.3    | Security   |                                                      |                                                   | 58             |

| 12 | Annen   | div A = Da | ata Structu                                          | ires                                              | 50             |

| 12 | 12.1    |            |                                                      |                                                   |                |

|    | 12.1    | 12.1.1     |                                                      | de.h                                              |                |

|    | 12.2    |            |                                                      | ue.n.                                             |                |

|    | 12.2    | 12.2.1     |                                                      | Гуре.h                                            |                |

|    |         | 12.2.2     |                                                      | us Code                                           |                |

|    | 12.3    | EFI PEI    |                                                      | S_INFO_HOB                                        |                |

|    |         |            |                                                      | <br>InfoHob.h                                     |                |

|    | 12.4    | EFI_PEI_   | _GRAPHICS                                            | S_DEVICE_INFO_HOB                                 | 62             |

|    |         | 12.4.1     | GraphicsI                                            | infoHob.h                                         | 62             |

|    | 12.5    | EFI_GUI    | D                                                    |                                                   | 62             |

|    |         | 12.5.1     |                                                      |                                                   |                |

|    |         | 12.5.2     |                                                      | Гуре.h                                            |                |

|    | 12.6    | _          | _                                                    | <u> </u>                                          |                |

|    | 40.7    | 12.6.1     |                                                      | Phase.h                                           |                |

|    | 12.7    |            | •                                                    | OB)                                               |                |

|    | 12.8    | 12.7.1     |                                                      | and Firmware Filesystem                           |                |

|    | 12.0    | 12.8.1     |                                                      | reVolume.h                                        |                |

|    |         | 12.8.2     |                                                      | reFile.h                                          |                |

|    | 12.9    |            |                                                      |                                                   |                |

|    | 12.5    | 12.9.1     |                                                      | .h                                                |                |

|    |         |            |                                                      |                                                   |                |

## **Figures**

| Figure 1: Intel® FSP Component Logical View Figure 2: Intel® FSP Component Layout View Figure 3: Intel® FSP Component Headers Figure 4: API Mode Boot Flow Figure 5: Dispatch Mode Boot Flow Figure 6: Dispatch Mode Design | 15<br>20<br>27<br>29 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Tables                                                                                                                                                                                                                      |                      |

| Table 1. FSP_INFO_HEADER                                                                                                                                                                                                    | 16                   |

| Table 2. FSP_INFO_EXTENDED_HEADER                                                                                                                                                                                           | 18                   |

| Table 3. FSPP - PatchData Encoding                                                                                                                                                                                          |                      |

| Table 4. UPD Standard Fields                                                                                                                                                                                                |                      |

| Table 5. Return Values - TempRamInit() API                                                                                                                                                                                  |                      |

| Table 6. Return Values - FspMemoryInit() API                                                                                                                                                                                | 37                   |

| Table 7. Return Values - TempRamExit() API                                                                                                                                                                                  |                      |

| Table 8. Return Values – FspSiliconInit() API                                                                                                                                                                               | 41                   |

| Table 9. Return Values – NotifyPhase() API                                                                                                                                                                                  |                      |

| Table 10. Return Values - TempRamExit() PPI                                                                                                                                                                                 | 49                   |

# **Revision History**

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2019   | 2.1      | <ul> <li>Based on FSP EAS v2.0 - Backward compatibility is retained.</li> <li>Added Dispatch Mode to ease integration with UEFI bootloaders.</li> <li>FSP_INFO_HEADER changes         <ul> <li>Updated SpecVersion from 0x20 to 0x21</li> <li>Updated HeaderRevision from 3 to 4</li> <li>Defined bit 1 in ImageAttribute to indicate support for dispatch mode.</li> </ul> </li> <li>FSPM_ARCH_UPD changes         <ul> <li>Modified StackBase and StackSize to only contain FSP heap data during pre-memory phase.</li> </ul> </li> <li>FSP_STATUS_RESET_REQUIRED_* may now be returned by NotifyPhase()</li> <li>Added description of dispatch mode boot flow</li> <li>Added dispatch mode API definitions</li> </ul> <li>Added FSP_ERROR_INFO &amp; FSP_ERROR_INFO_HOB</li>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |          | Added EFI_PEI_GRAPHICS_DEVICE_INFO_HOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| April 2016 | 2.0      | <ul> <li>Based on FSP EAS v1.1a - Removed compatibility with v1.x</li> <li>Updated FSP Binary format with FSP component information, layout, parsing and identification</li> <li>FSP_INFO_HEADER changes         <ul> <li>Updated HeaderRevision from 2 to 3</li> <li>Reduced ImageAttribute field from 4 to 2 bytes</li> <li>Defined new ComponentAttribute field and defined ComponentType (Bits15:12)</li> <li>Defined Bit0 and Bit1 in ComponentAttribute for Debug/Release &amp; Test/Official respectively</li> <li>Renamed Reserved to Reserved1</li> <li>Renamed ApiEntryNum to Reserved2</li> <li>Renamed FspInitEntryOffset to Reserved3</li> <li>Added SpecVersion at offset 11</li> </ul> </li> <li>Removed VPD configuration data and updated UPD configuration data &amp; UPD common header structure</li> <li>Added Reset Request status return types</li> <li>Updated API sections to clarify optional API and calling order of API</li> <li>Updated the input parameters of TempRamInit(), FspMemoryInit(), TempRamExit(), FspSiliconInit() and NotifyPhase() API</li> <li>TempRamInit()</li> <li>Stack usage/stack allocation to bootloader clarified</li> <li>Calling convention exception clarified</li> <li>Removed parameter structure/description.</li> <li>Updated API parameters to use FSPT_UPD</li> </ul> |

| <ul> <li>Simplified the API and remove the parameter structures</li> </ul>         |

|------------------------------------------------------------------------------------|

| <ul> <li>Minor clarification related to stack base and size and cleanup</li> </ul> |

| <ul> <li>Defined Arch UPDs for FSP-M component FSPM_ARCH_UPD</li> </ul>            |

| TempRamExit() - Updated API parameters                                             |

| NotifyPhase() - Added EndOfFirmware phase                                          |

| Clarified NVS HOB Fast Boot / S3 path                                              |

| Updated BootFlow diagram and added description                                     |

§

## 1 Introduction

#### 1.1 Purpose

The purpose of this document is to describe the external architecture and interfaces provided in the Intel® Firmware Support Package (Intel® FSP). Implementation specific details are outside the scope of this document. Refer to *Integration Guide* for details.

#### 1.2 Intended Audience

This document is targeted at all platform and system developers who need to generate or consume Intel® FSP binaries in their bootloader solutions. This includes, but is not limited to: System firmware or UEFI firmware or BIOS developers, bootloader developers, system integrators, as well as end users.

#### 1.3 Related Documents

- Intel® FSP EAS version 2.0 <a href="http://www.intel.com/content/dam/www/public/us/en/documents/technical-specifications/fsp-architecture-spec-v2.pdf">http://www.intel.com/content/dam/www/public/us/en/documents/technical-specifications/fsp-architecture-spec-v2.pdf</a>

- Boot Specification File (BSF) Specification https://firmware.intel.com/sites/default/files/BSF 1 0.pdf

- Unified Extensible Firmware Interface (UEFI) Specification http://www.uefi.org/specifications

- Platform Initialization (PI) Specification v1.7

https://uefi.org/sites/default/files/resources/PI Spec 1 7 final Jan 2019.pdf

- Binary Configuration Tool (BCT) for Intel<sup>®</sup> Firmware Support Package available at http://www.intel.com/fsp

- Intel® Firmware Module Management Tool (Intel® FMMT) available at https://firmware.intel.com/develop

## 1.4 Terminology

| ACPI    | Advanced Configuration and Power Interface                               |

|---------|--------------------------------------------------------------------------|

| ВСТ     | Binary Configuration Tool                                                |

| BIOS    | Basic Input Output System                                                |

| BSP     | Boot Strap Processor                                                     |

| BSF     | Boot Setting File                                                        |

| BWG     | BIOS Writer's Guide a.k.a. BIOS Specification a.k.a. IA FW Specification |

| FDF     | Flash Description File                                                   |

| FSP     | Firmware Support Package(s)                                              |

| FSP API | Firmware Support Package Interface(s)                                    |

| FV      | Firmware Volume                                                          |

| GUI     | Graphical User Interface                                                 |

| GUID    | Globally Unique IDentifier(s)                                            |

| НОВ     | Hand Off Block(s)                                                        |

| PI      | Platform Initialization                                                  |

| PIC     | Position Independent Code                                                |

| RAM     | Random Access Memory                                                     |

| ROM     | Read Only Memory                                                         |

| SMM     | System Management Mode                                                   |

| SOC     | System-On-Chip(s)                                                        |

| TOLUM   | Top of low usable memory                                                 |

| TPM     | Trusted Platform Module                                                  |

| UEFI    | Unified Extensible Firmware Interface                                    |

| UPD     | Updatable Product Data                                                   |

## 2 Intel® FSP Overview

### 2.1 Design Philosophy

Intel recognizes that it holds the key programming information that is crucial for initializing Intel silicon. Some key programming information is treated as proprietary information and may only be available with legal agreements.

Intel® Firmware Support Package (Intel® FSP) is a binary distribution of necessary Intel silicon initialization code. The first design goal of the Intel® FSP is to provide ready access to the key programming information that is not publicly available. The second design goal is to abstract the complexities of Intel Silicon initialization and expose a limited number of well-defined interfaces.

A fundamental design philosophy is to provide the ubiquitously required silicon initialization code. As such, FSP will often provide only a subset of the product's features.

#### 2.2 Technical Overview

Intel® FSP provides chipset and processor initialization in a format that can easily be incorporated into many existing bootloaders.

Intel® FSP performs the necessary initialization steps as documented in the BIOS Writers Guide (BWG) / BIOS Specification including initialization of the processor, memory controller, chipset and certain bus interfaces, if necessary.

Intel® FSP is not a stand-alone bootloader; therefore it needs to be integrated into a bootloader to carry out other functions such as:

- Initializing non-Intel components

- Bus enumeration and device discovery

- Industry standards

#### **2.2.1** Data Structure Descriptions

All data structures defined in this specification conform to the "little endian" byte order i.e., the low-order byte of a multibyte data items in memory is at the lowest address, while the high-order byte is at the highest address.

All reserved fields defined in this specification must be zero unless stated otherwise.

# 3 Intel® FSP Integration

The Intel® FSP binary can be integrated into many different bootloaders and embedded operating systems.

Below are some required steps for the integration:

#### Customizing

The Intel® FSP has configuration parameters that can be customized to meet the needs of the target platform.

#### Rebasing

The Intel® FSP is not Position Independent Code (PIC) and each FSP component has to be rebased if it is placed at a location which is different from the preferred base address specified during the FSP build.

#### Placing

Once the Intel® FSP binary is ready for integration, the bootloader needs to be modified to place this FSP binary at the specific base address identified above.

#### Interfacing

The bootloader needs to add code to setup the operating environment for the Intel® FSP, call the FSP API with the correct parameters, and parse the FSP output to retrieve the necessary information returned by the FSP.

## 3.1 Intel® FSP Distribution Package

The Intel® FSP distribution package contains the following:

- Intel® FSP Binary

- Integration Guide

- · Data structure definitions

- Boot Settings File (BSF)

The Binary Configuration Tool (BCT) can be used to configure the FSP. BCT is available as a separate package.

## 4 Intel® FSP Binary Format

The Intel® FSP binary follows the *UEFI Platform Initialization Firmware Volume*Specification format. The Firmware Volume (FV) format is described in the *Platform Initialization (PI) Specification - Volume 3: Shared Architectural Elements* specification as referenced in *Section 1.3 Related Documents*.

Firmware Volume (FV) is a way to organize/structure binary **components** and enables a standardized way to parse the binary and handle the individual binary components that make up the Firmware Volume (FV).

Intel® FSP will have several components each containing one or more Firmware Volumes (FV). Each component provides a phase of initialization as below.

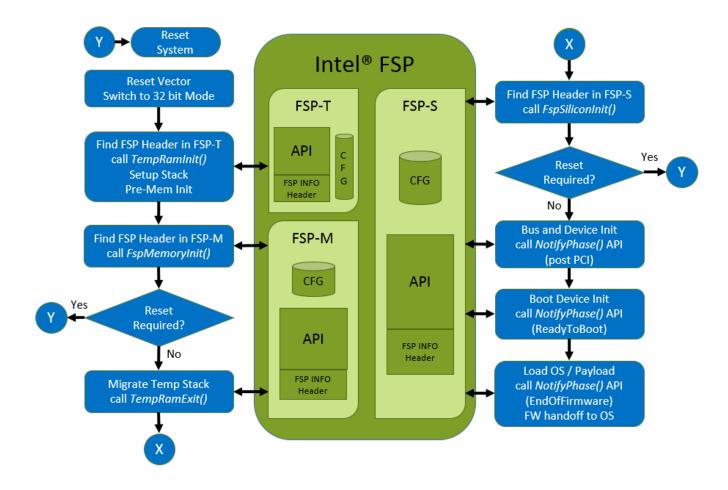

# **4.1.1 FSP-T: Temporary RAM initialization** phase

Primary purpose of this phase is to initialize the Temporary RAM along with any other early initialization.

This phase consists of below FSP API

TempRamInit()

#### 4.1.2 FSP-M: Memory initialization phase

Primary purpose of this phase is to initialize the permanent memory along with any other early silicon initialization.

This phase consists of below FSP API

FspMemoryInit()

TempRamExit()

### **4.1.3** FSP-S: Silicon initialization phase

Primary purpose of this phase is to complete the silicon initialization including CPU and IO controller initialization.

This phase consists of below FSP API

FspSiliconInit()

NotifyPhase() - Post PCI bus enumeration, Ready To Boot and End of Firmware.

Figure 1: Intel® FSP Component Logical View

May 2019

Intel® Firmware Support Package EAS

#### 4.1.4 OEM Components (FSP-O)

An FSP may include optional OEM components that provide OEM extensibility. This component shall have an FSP\_INFO\_HEADER with component type in Image attribute field set to FSP-O.

#### 4.2 Intel® FSP Component Identification

Each FSP component will have an **FSP\_INFO\_HEADER** as the first FFS file in the first Firmware Volume (FV). The **FSP\_INFO\_HEADER** will have an attribute field that can be used to identify that component as an FSP-T/FSP-M/FSP-S/FSP-O component.

There can be only one instance of the FSP-T / FSP-M / FSP-S in an FSP binary, while multiple instances of the FSP-O component are valid.

#### 4.2.1 Intel® FSP Image ID and Revision

The **FSP\_INFO\_HEADER** structure inside each FSP component also contains an Image Identifier field and an Image Revision field that provide the identification and revision information for the FSP binary. It is important to verify these fields while integrating the FSP binary as the FSP configuration data could change over different FSP Image identifiers and revisions.

The FSP Image Identifier field should be the same for all the FSP components within the same FSP binary.

#### 4.2.2 Intel® FSP Component Layout

All the FSP components are packaged back to back within the FSP and the size of each component is available in the component's **FSP\_INFO\_HEADER** structure.

Further more, if there are multiple Firmware Volume(s) inside the FSP component, they are also packaged back to back. These components can be packaged in any order inside the FSP binary.

Figure 2: Intel® FSP Component Layout View

FSP-T

Temp RAM Phase Data

FSP\_INFO\_HEADER - T

FSP-M

Memory Init Phase Data

FSP\_INFO\_HEADER - M

FSP-S

Silicon Init Phase Data

FSP\_INFO\_HEADER - S

FSP\_Base

## 5 Intel® FSP Information tables

Each Intel® FSP component has an **FSP\_INFO\_HEADER** table and may optionally have additional tables as described below.

All Intel® FSP tables must have a 4 byte aligned base address and a size that is a multiple of 4 bytes.

All Intel® FSP tables must be placed back-to-back.

All Intel® FSP tables must begin with a DWORD signature followed by a DWORD length field.

A generic table search algorithm for additional tables can be implemented with a signature search algorithm until a terminator signature 'FSPP' is found.

#### 5.1.1 FSP\_INFO\_HEADER

The **FSP\_INFO\_HEADER** structure conveys the information required by the bootloader to interface with the Intel(R) FSP binary.

Table 1. FSP\_INFO\_HEADER

| Byte<br>Offset | Size<br>in<br>Bytes | Field          | Description                                                                                                                                                                      |

|----------------|---------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | 4                   | Signature      | `FSPH'. Signature for the FSP_INFO_HEADER.                                                                                                                                       |

| 4              | 4                   | HeaderLength   | Length of the header in bytes. The current value for this field is 72.                                                                                                           |

| 8              | 2                   | Reserved1      | Reserved bytes for future.                                                                                                                                                       |

| 10             | 1                   | SpecVersion    | Indicates compliance with a revision of this specification in the BCD format.  3:0-Minor Version  7:4-Major Version  For revision v2.1 the value will be 0x21                    |

| 11             | 1                   | HeaderRevision | Revision of the header. The current value for this field is 4.                                                                                                                   |

| 12             | 4                   | ImageRevision  | Revision of the FSP binary. Major.Minor.Revision.Build The ImageRevision can be decoded as follows: 7:0 - Build Number 15:8 - Revision 23:16- Minor Version 31:24- Major Version |

| Byte<br>Offset | Size<br>in<br>Bytes | Field              | Description                                                                                                                                                                                                                                                                                                                                |

|----------------|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16             | 8                   | ImageId            | 8 ASCII character byte signature string that will help match the FSP binary to a supported hardware configuration. BootLoader should not assume null-terminated.                                                                                                                                                                           |

| 24             | 4                   | ImageSize          | Size of this component in bytes.                                                                                                                                                                                                                                                                                                           |

| 28             | 4                   | ImageBase          | Preferred base address for this component. If the FSP component is located at the address different from the preferred address, the FSP component needs to be rebased.                                                                                                                                                                     |

| 32             | 2                   | ImageAttribute     | Attributes of the FSP binary.                                                                                                                                                                                                                                                                                                              |

|                |                     |                    | <ul> <li>Bit 0: Graphics Support – Set to 1 when FSP supports enabling Graphics Display.</li> <li>Bit 1: Dispatch Mode Support – Set to 1 when FSP supports the optional Dispatch Mode API defined in Section 7.2 and 9.</li> <li>Bits 15:2 - Reserved</li> </ul>                                                                          |

| 34             | 2                   | ComponentAttribute | Attributes of the FSP Component  • Bit 0 - Build Type  0 - Debug Build  1 - Release Build  • Bit 1 - Release Type  0 - Test Release  1 - Official Release  • Bit 11:2 - Reserved  • Bits 15:12 - Component Type  0000 - Reserved  0001 - FSP-T  0010 - FSP-M  0011 - FSP-S  0100 to 0111 - Reserved  1000 - FSP-O  1001 to 1111 - Reserved |

| 36             | 4                   | CfgRegionOffset    | Offset of the UPD configuration region. This offset is relative to the respective FSP Component base address. Please refer Section 6 for details.                                                                                                                                                                                          |

| 40             | 4                   | CfgRegionSize      | Size of the UPD configuration region. Please refer Section 6 for details.                                                                                                                                                                                                                                                                  |

| 44             | 4                   | Reserved2          | This value must be 0x00000000 if the FSP HeaderRevision is >=3.                                                                                                                                                                                                                                                                            |

| Byte<br>Offset | Size<br>in<br>Bytes | Field                     | Description                                                                                                                                                                |

|----------------|---------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48             | 4                   | TempRamInitEntryOffset    | Offset for the API to setup a temporary stack till the memory is initialized.  If the value is set to 0x00000000, then this API is not available in this component.        |

| 52             | 4                   | Reserved3                 | This value must be 0x00000000 if the FSP HeaderRevision is >=3.                                                                                                            |

| 56             | 4                   | NotifyPhaseEntryOffset    | Offset for the API to inform the FSP about the different stages in the boot process.  If the value is set to 0x00000000, then this API is not available in this component. |

| 60             | 4                   | FspMemoryInitEntryOffset  | Offset for the API to initialize the Memory.  If the value is set to 0x00000000, then this API is not available in this component.                                         |

| 64             | 4                   | TempRamExitEntryOffset    | Offset for the API to tear down the temporary memory.  If the value is set to 0x0000000, then this API is not available in this component.                                 |

| 68             | 4                   | FspSiliconInitEntryOffset | Offset for the API to initialize the processor and chipset.  If the value is set to 0x0000000, then this API is not available in this component.                           |

#### 5.1.2 FSP\_INFO\_EXTENDED\_HEADER

The **FSP\_INFO\_EXTENDED\_HEADER** structure conveys additional information about the FSP binary component. This allows FSP producers to provide additional information about the FSP instantiation.

Table 2. FSP\_INFO\_EXTENDED\_HEADER

| Byte<br>Offset | Size<br>in<br>Bytes | Field               | Description                                                                                          |

|----------------|---------------------|---------------------|------------------------------------------------------------------------------------------------------|

| 0              | 4                   | Signature           | `FSPE'. Signature for the FSP_INFO_EXTENDED_HEADER.                                                  |

| 4              | 4                   | Length              | Length of the table in bytes, including all additional FSP producer defined data.                    |

| 8              | 1                   | Revision            | FSP producer defined revision of the table.                                                          |

| 9              | 1                   | Reserved            | Reserved for future use.                                                                             |

| 10             | 6                   | FspProducerId       | FSP producer identification string.                                                                  |

| 16             | 4                   | FspProducerRevision | FSP producer implementation revision number.<br>Larger numbers are assumed to be newer<br>revisions. |

| Byte<br>Offset | Size<br>in<br>Bytes | Field               | Description                                                           |

|----------------|---------------------|---------------------|-----------------------------------------------------------------------|

| 20             | 4                   | FspProducerDataSize | Size of the FSP producer defined data (n) in bytes.                   |

| 24             | n                   |                     | FSP producer defined data of size (n) defined by FspProducerDataSize. |

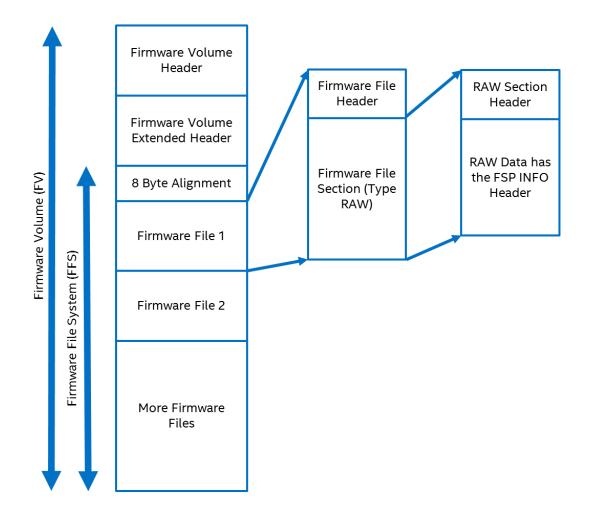

#### 5.1.3 Locating FSP\_INFO\_HEADER

The FSP\_INFO\_HEADER structure is stored in a firmware file, called the FSP\_INFO\_HEADER file and is placed as the first firmware file within each of the FSP component's first Firmware Volume (FV). All firmware files will have a GUID that can be used to identify the files, including the FSP\_INFO\_HEADER file. The FSP\_INFO\_HEADER file GUID is FSP\_FFS\_INFORMATION\_FILE\_GUID

```

#define FSP_FFS_INFORMATION_FILE_GUID \

{ 0x912740be, 0x2284, 0x4734, { 0xb9, 0x71, 0x84, 0xb0, 0x27,

0x35, 0x3f, 0x0c }};

```

The bootloader can find the offset of the **FSP\_INFO\_HEADER** within the FSP component's first Firmware Volume (FV) by the following steps described below:

- Use **EFI\_FIRMWARE\_VOLUME\_HEADER** to parse the FSP FV header and skip the standard and extended FV header.

- The **EFI\_FFS\_FILE\_HEADER** with the **FSP\_FFS\_INFORMATION\_FILE\_GUID** is located at the 8-byte aligned offset following the FV header.

- The **EFI\_RAW\_SECTION** header follows the FFS File Header.

- Immediately following the EFI\_RAW\_SECTION header is the raw data. The format of this data is defined in the FSP\_INFO\_HEADER and additional header structures.

A pictorial representation of the data structures that is parsed in the above flow is provided below.

**Figure 3: Intel® FSP Component Headers**

#### **5.1.4 FSP Description File**

An FSP component may optionally include an FSP description file. This file will provide information about the FSP including information about different silicon revisions the FSP supports. The contents of the FSP description file must be an ASCII encoded text string.

The file, if present, must have the following file GUID and be included in the FDF file as shown below.

#### 5.1.5 FSP Patch Table (FSPP)

FSP Patch Table contains offsets inside the FSP binary which store absolute addresses based on the FSP base. When the FSP is rebased the offsets listed in this table needs to be patched accordingly.

A PatchEntryNum of 0 is valid and indicates that there are no entries in the patch table and should be handled as a valid patch table by the rebasing software.

#### Table 3. FSPP - PatchData Encoding

| BIT [23:00] | Image OFFSET to patch                                                                                                                          |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BIT [27:24] | Patch type  0000: Patch DWORD at OFFSET with the delta of the new and old base.  NewValue = OldValue + (NewBase - OldBase)  1111: Same as 0000 |  |

|             | Others: Reserved                                                                                                                               |  |

| BIT [28:30] | Reserved                                                                                                                                       |  |

May 2019 Document Number: 611786-2.1

```

BIT [31]

0: The FSP image offset to patch is determined by Bits[23:0]

1: The FSP image offset to patch is calculated by (ImageSize - (0x1000000 - Bits[23:0]))

If the FSP image offset to patch is greater than the ImageSize in the FSP_INFO_HEADER, then this patch entry should be ignored.

```

#### **5.1.5.1** Example

Let's assume the FSP image size is 0x38000. And we need to rebase the FSP base from 0xFFFC0000 to 0xFFF00000.

Below is an example of the typical implementation of the FSP\_PATCH\_TABLE:

Looking closer at the patch table entries:

```

0xFFFFFFC, ///< Patch FVBASE at end of FV</pre>

```

The image offset to patch in the FSP image is indicated by BIT[23:0], 0xFFFFFC. Since BIT[31] is 1, the actual FSP image offset to patch should be:

```

ImageSize - (0x1000000 - 0xFFFFFC) = 0x38000 - 4 = 0x37FFC

```

If the DWORD at offset 0x37FFC in the original FSP image is 0xFFFC0000, then the new value should be:

```

OldValue + (NewBase - OldBase) = 0xFFFC0000 + (0xFFF00000 - 0xFFFC0000) = 0xFFF00000

```

Thus the DWORD at FSP image offset 0x37FFC should be patched to xFFF00000 after the rebasing.

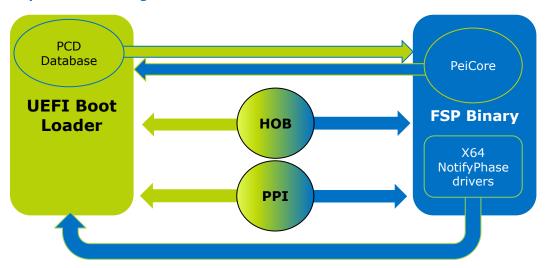

# 6 Intel® FSP Configuration Data

Each Intel® FSP module contains a configurable data region which can be used by the FSP during initialization. This configuration region is a data structure called the Updateable Product Data (UPD) and will contain the default parameters for FSP initialization. The UPD data structure is only used by the FSP when the FSP is being invoked using the API mode interface defined in Section 8.

When the FSP is invoked according to the dispatch mode interface defined in Section 9, the UPD configuration region and the UPD data structure are not used by the FSP. In dispatch mode, the PPI database and PCD database are shared between the bootloader and the FSP. Because they are shared, the UPD configuration region is not needed to provide a mechanism to pass configuration data from the bootloader to the FSP. Instead, configuration data is communicated to the FSP using PCD and PPI. The bootloader may utilize the UPD to influence PCD and PPI contents provided to the FSP in dispatch mode.

The UPD parameters can be statically customized using a separate Binary Configuration Tool (BCT). There will be a Boot Setting File (BSF) provided along with FSP binary to describe the configuration options within the FSP. This file contains the detailed information on all configurable options, including description, help information, valid value range and the default value.

The UPD data can also be dynamically overridden by the bootloader during runtime in addition to static configuration. Platform limitations like lack of updateable memory before calling *TempRamInit()* API may pose restrictions on the FSP-T data runtime update. Any such restrictions will be documented in the Integration Guide.

The UPD data is organized as a structure. The <code>TempRamInit()</code>, <code>FspMemoryInit()</code> and <code>FspSiliconInit()</code> API parameters include a pointer which can be initialized to point to the UPD data structure. If this pointer is initialized to NULL when calling these API, the FSP will use the default built-in UPD configuration data in the respective FSP components. However, if the bootloader needs to update any of the UPD parameters, it is recommended to copy the whole UPD structure from the FSP component to memory, update the parameters and initialize the UPD pointer to the address of the updated UPD structure. The FSP API will then use this data structure instead of the default configuration region data for platform initialization. The UPD data structure is a project specific structure. Please refer to the <code>Integration Guide</code> for the details of this structure.

The UPD structure has some standard fields followed by platform specific parameters and the UPD structure definition will be provided as part of the FSP distribution package.

#### 6.1 UPD Standard Fields

The first few fields of the UPD Region are standard for all FSP implementations as documented below.

#### **Table 4. UPD Standard Fields**

| Offset      | Field                                                                                     |

|-------------|-------------------------------------------------------------------------------------------|

| 0x00 - 0x07 | UPD Region Signature. The signature will be                                               |

|             | "XXXXXX_T" for FSP-T                                                                      |

|             | "XXXXXX_M" for FSP-M                                                                      |

|             | "XXXXXX_S" for FSP-S                                                                      |

|             | Where XXXXXX is an unique signature                                                       |

| 0x08        | Revision of the Data structure                                                            |

| 0x09 - 0x1F | Reserved[23]                                                                              |

| 0x20 - n    | Platform Specific Parameters, where the n is equal to (FSP_INFO_HEADER.CfgRegionSize – 1) |

```

typedef struct {

UINT64 Signature;

UINT8 Revision;

UINT8 Reserved[23];

} FSP UPD HEADER;

```

#### **6.1.1** FSP-T UPD Structure

The UPD data structure definition for the FSP-T component will be provided as part of the FSP release package and documented in the integration guide as well.

#### 6.1.2 FSP-M UPD Structure

The UPD data structure definition for the FSP-M component will be provided as part of the FSP release package and documented in the integration guide as well.

```

typedef struct {

FSP UPD HEADER

UpdHeader;

FSPM ARCH UPD

FspmArchUpd;

/**

Platform specific parameters

**/

} FSPM UPD;

typedef struct {

UINT8

Revision;

UINT8

Reserved[3]

VOID

*NvsBufferPtr;

VOID

*StackBase;

UINT32

StackSize;

UINT32

BootLoaderTolumSize;

UINT32

BootMode;

UINT8

Reserved1[8];

} FSPM ARCH UPD;

```

| Revision     | Revision of the structure is 1 for this version of the specification.                                                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NvsBufferPtr | Pointer to the non-volatile storage (NVS) data buffer. If it is <b>NULL</b> it indicates the NVS data is not available. Refer to Section 10.2 for more details.                                                                                                                                                                                                      |

| StackBase    | Pointer to the temporary RAM base address to be consumed inside <i>FspMemoryInit()</i> API.                                                                                                                                                                                                                                                                          |

|              | For FSP implementations compliant to v2.0 of this specification, the temporary RAM is used to establish a stack and a HOB heap. For FSP implementations compliant to v2.1 of this specification, the temporary RAM is only used for a HOB heap.                                                                                                                      |

|              | Starting with v2.1 of this specification, FSP will run on top of the stack provided by the bootloader instead of establishing a separate stack. This allows the stack memory to be reused after FspMemoryInit() returns to the bootloader. To retain backwards compatibility with earlier versions of this specification, this parameter retains the StackBase name. |

| StackSize           | For FSP implementations compliant to v2.0 of this specification, the temporary RAM size used to establish a stack and HOB heap. Consumed by the FspMemoryInit() API.                                                                                                                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | For FSP implementations compliant to v2.1 of this specification, the temporary RAM size used to establish a HOB heap inside the <i>FspMemoryInit()</i> API.                                                                                                                                                                                                          |

|                     | Starting with v2.1 of this specification, FSP will run on top of the stack provided by the bootloader instead of establishing a separate stack. This allows the stack memory to be reused after FspMemoryInit() returns to the bootloader. To retain backwards compatibility with earlier versions of this specification, this parameter retains the StackSize name. |

|                     | Refer to the <i>Integration Guide</i> for the minimum required temporary RAM size. In the case of FSP v2.1, the <i>Integration Guide</i> shall also specify the minimum free stack space required at the point where the FSP API entrypoints are called.                                                                                                             |

| BootloaderTolumSize | Size of memory to be reserved by FSP below "top of low usable memory" for bootloader usage. Refer to Section 10.3 for more details.                                                                                                                                                                                                                                  |

| BootMode            | Current boot mode. Values are defined in Section 12.1 Appendix A – Data Structures. Refer to the Integration Guide for supported boot modes.                                                                                                                                                                                                                         |

#### **6.1.3** FSP-S UPD Structure

The UPD data structure definition for the FSP-S component will be provided as part of the FSP release package and documented in the integration guide as well.

## 7 Boot Flow

The Intel® FSP v2.1 specification defines two possible FSP boot flows. The first boot flow is the "API mode" boot flow. This boot flow is identical to the boot flow defined in the Intel® FSP v2.0 specification. This specification also defines the "dispatch mode" boot flow. It is not required for a specific implementation of FSP to support the dispatch mode boot flow. The API mode boot flow is mandatory for all FSP implementations. **FSP\_INFO\_HEADER** indicates if dispatch mode is supported by the FSP.

#### 7.1 API Mode Boot Flow

Figure 4: API Mode Boot Flow

#### **7.1.1** Boot Flow Description

- 1. Bootloader starts executing from Reset Vector.

- a) Switches the mode to 32-bit mode.

- b) Initializes the early platform as needed.

- c) Finds FSP-T and calls the *TempRamInit()* API. The bootloader also has the option to initialize the temporary memory directly, in which case this step and step 2 are skipped.

- 2. FSP initializes temporary memory and returns from *TempRamInit()* API.

- 3. Bootloader initializes the stack in temporary memory.

- a) Initializes the platform as needed.

- b) Finds FSP-M and calls the FspMemoryInit() API.

- 4. FSP initializes memory and returns from FspMemoryInit() API.

- 5. Bootloader relocates itself to Memory.

- 6. Bootloader calls *TempRamExit()* API. If Bootloader initialized the temporary memory in step 1.c)... this step and the next step are skipped.

- 7. FSP returns from TempRamExit() API.

- 8. Bootloader finds FSP-S and calls FspSiliconInit() API.

- 9. FSP returns from FspSiliconInit() API.

- 10. Bootloader continues and device enumeration.

- 11. Bootloader calls NotifyPhase() API with AfterPciEnumeration parameter.

- 12. Bootloader calls *NotifyPhase()* API with *ReadyToBoot* parameter before transferring control to OS loader.

- 13. When booting to a non-UEFI OS, Bootloader calls *NotifyPhase()* API with *EndOfFirmware* parameter immediately after *ReadyToBoot*.

- 14. When booting to a UEFI OS, Bootloader calls NotifyPhase() with EndOfFirmware parameter during ExitBootServices.

**Note:** : If FSP returns the reset required status in any of the API, then bootloader performs the reset. Refer to the *Integration Guide* for more details on Reset Types.

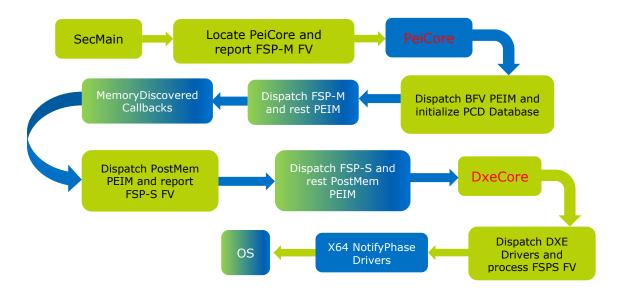

#### 7.2 Dispatch Mode Boot Flow

Dispatch mode is an optional boot flow intended to enable FSP to integrate well in to UEFI bootloader implementations. Implementation of this boot flow necesitates that the underlying FSP implementation uses the Pre-EFI Initialization (PEI) environment defined in the *PI Specification*. It is possible to implement an FSP without using PEI, so bootloaders must check that dispatch mode is available using the **FSP\_INFO\_HEADER**, see Section 5.1.1 for further details. The *Integration Guide* will also specify if an FSP implements dispatch mode. See Section 9 for a full description of dispatch mode.

#### 7.2.1 High Level Overview

Figure 5: Dispatch Mode Boot Flow

Blue blocks are from the FSP binary and green blocks are from the bootloader. Blocks with mixed colors indicate that both bootloader and FSP modules are dispatched during that phase of the boot flow.

Dispatch mode is intended to implement a boot flow that is as close to a standard UEFI boot flow as possible. In dispatch mode, FSP exposes Firmware Volumes (FV) directly to the bootloader. The PEIM in these FV are executed directly in the context of the PEI environment provided by the bootloader. FSP-T, FSP-M, and FSP-S could contain one or multiple FVs. The exact FVs layout will be described in the *Integration Guide*. In dispatch mode, the PPI database, PCD database, and HOB list are shared between the bootloader and the FSP.

In dispatch mode, the *NotifyPhase()* API is not used. Instead, FSP-S contains DXE drivers that implement the native callbacks on equivalent events for each of the *NotifyPhase()* invocations.

#### 7.2.2 Boot Flow Description

This boot flow assumes that the bootloader is a typical UEFI firmware implementation conforming to the *PI Specification*. Therefore, the bootloader will follow the standard four phase PI boot flow progressing from SEC phase, to PEI phase, to DXE phase, to BDS phase.

- 1. Bootloader provided SEC phase starts executing from Reset Vector.

- a) Switches the mode to 32-bit mode.

- b) Initializes the early platform as needed.

- c) Finds FSP-T and calls the *TempRamInit()* API. SEC also has the option to initialize the temporary memory directly, in which case this step and step 2 are skipped.

- 2. FSP initializes temporary memory and returns from TempRamInit() API.

- 3. SEC initializes the stack in temporary memory.

- SEC finds FSP-M and adds an instance of EFI\_PEI\_CORE\_FV\_LOCATION\_PPI containing the address of FSP-M to the PpiList passed in to PEI core.

- 5. SEC calls the entry point for the PEI core inside FSP-M.

- a) Bootloader passes the FSP-M PEI core a EFI\_SEC\_PEI\_HAND\_OFF data structure with the BootFirmwareVolumeBase and BootFirmwareVolumeSize members pointing to a FV provided by the platform.

- The bootloader provides the Boot Firmware Volume (BFV).

Consequently, in FSP dispatch mode PEI core is not in the BFV unlike most UEFI firmware implementations.

- 6. PEI core dispatches the PEIM in the BFV provided by the bootloader.

- 7. Bootloader installs FSPM\_ARCH\_CONFIG\_PPI.

- 8. One of the PEIM provided by the bootloader installs a **EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI** for each FV contained in FSP-M.

- a) The bootloader must not install the EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI(s) for FSP-M until the bootloader is ready for FSP-M to execute.

- b) If FSP-M requires any DynamicEx PCD values, the bootloader must ensure those PCD contain valid data before installing the EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI(s) for FSP-M.

- 9. PEI core will continue to dispatch PEIM. During the course of dispatch, PEIM included with FSP-M will be executed.

- a) Some of the PEIM contained in FSP-M may require configuration data to be provided by the bootloader. If this is the case, the configuration data may be stored in either DynamicEx PCD or PPI.

- If the configuration data is stored in PCD, then it is assumed that the PCD contain valid data before FSP-M begins execution.

- If the configuration data is stored in PPI, then the needed PPI will either be in the PEIM's DEPEX, or the PEIM will register a callback for the needed PPI and not attempt to access the PPI until the callback is invoked by PEI core.

- 10. FSP-M installs FSP\_TEMP\_RAM\_EXIT\_PPI.

- 11. After dispatching the PEIM in FSP-M, memory will be initialized. Accordingly, FSP-M will call (\*PeiServices)->InstallPeiMemory().

- a) PEI core shadows to main memory.

- b) PEI core invokes TemporaryRamDone() from EFI\_PEI\_TEMPORARY\_RAM\_DONE\_PPI. The implementation of EFI\_PEI\_TEMPORARY\_RAM\_DONE\_PPI is provided by the bootloader.

- c) The bootloader implementation of EFI\_PEI\_TEMPORARY\_RAM\_DONE\_PPI calls TempRamExit() from FSP\_TEMP\_RAM\_EXIT\_PPI.

- For platforms that use the SEC implementation in UefiCpuPkg, SEC core implements

EFI\_PEI\_TEMPORARY\_RAM\_DONE\_PPI. The TemporaryRamDone() implementation in SEC core will call SecPlatformDisableTemporaryMemory(). This function would then locate FSP\_TEMP\_RAM\_EXIT\_PPI and call TempRamExit().

- If the bootloader did not call *TempRamInit()* in step 1.c) then the bootloader would not call *TempRamExit()*.

- d) PEI core follows up with an installation of the **EFI\_PEI\_PERMANENT\_MEMORY\_INSTALLED\_PPI**. Refer to Volume 1 of the *PI Specification* for details.

- 12. Post memory PEIM provided by the bootloader are now executed.

- 13. One of the PEIM provided by the bootloader installs a **EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI** for each FV contained in FSP-S.

- The bootloader must not install the EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI(s) for FSP-S until the bootloader is ready for FSP-S to execute.

- b) If FSP-S requires any DynamicEx PCD values, the bootloader must ensure those PCD contain valid data before installing the **EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI**(s) for FSP-S.

- 14. PEI core will continue to dispatch PEIM. During the course of dispatch, PEIM included with FSP-S will be executed.

- a) Some of the PEIM contained in FSP-S may require configuration data to be provided by the bootloader. If this is the case, the configuration data may be stored in either DynamicEx PCD or PPI.

- If the configuration data is stored in PCD, then it is assumed that the PCD contain valid data before FSP-S begins execution.

- If the configuration data is stored in PPI, then the needed PPI will either be in the PEIM's DEPEX, or the PEIM will register a callback for the needed PPI and not attempt to access the PPI until the callback is invoked by PEI core.

- 15. End of PEI is reached, and DXE begins execution.

- 16. Any DXE drivers included in FSP-S are dispatched. These drivers may create events to be notified at different points in the boot flow. FSP shall use a subset of the events defined by the *PI Specification*, see Section 9.3 for the full list of events the FSP may use.

- 17. DXE signals **EFI\_END\_OF\_DXE\_EVENT\_GROUP\_GUID** and transitions to BDS phase.

- a) Note: The *PI Specification* does not require that Step 17 occurs before Step 18, however most implementations appear to use this order.

- 18. BDS starts the PCI bus driver, which enumerates PCI devices. After enumeration, the PCI bus driver installs the **EFI\_PCI\_ENUMERATION\_PROTOCOL**. DXE signals any applicable events.

- 19. BDS signals **EFI\_EVENT\_GROUP\_READY\_TO\_BOOT** immediately before loading the OS boot loader.

- 20. BDS executes the OS boot loader. The OS boot loader loads the OS kernel into memory.

- 21. The OS boot loader calls *ExitBootServices()*, DXE signals this event before shutting down the UEFI Boot Services.

#### **7.2.3** Alternate Boot Flow Description

In some scenarios, the bootloader may wish to use a customized version of the PEI Foundation. For example, many software debugger implementations need to be linked with PEI core directly. For this reason, as an alternative to using the PEI core included with FSP-M, the bootloader may instead elect to use its own implementation of PEI core. In this case, the bootloader provided SEC will not produce the **EFI\_PEI\_CORE\_FV\_LOCATION\_PPI**, and instead of calling the entry point for the PEI core inside FSP-M it shall call the entry point for the PEI core inside the BFV. Note that this will result in two copies of PEI core being present in the final image, one in the BFV and one in the FSP-M. If firmware storage space is under pressure, one may elect to post process FSP-M using Intel® FMMT to remove the PEI core included with FSP.

This is generally considered to be a debug feature, and is discouraged for use in a production environment as it deviates from the boot flow that receives the most validation. It is also inefficient due to the duplicate copy of PEI core it introduces.

- 1. Bootloader provided SEC phase starts executing from Reset Vector.

- a) Switches the mode to 32-bit mode.

- b) Initializes the early platform as needed.

- c) Finds FSP-T and calls the *TempRamInit()* API. SEC also has the option to initialize the temporary memory directly, in which case this step and step 2 are skipped.

- 2. FSP initializes temporary memory and returns from *TempRamInit()* API.

- 3. SEC initializes the stack in temporary memory.

- 4. SEC calls the entry point for the PEI core inside the *Boot Firmware Volume* (BFV).

- 5. PEI core dispatches the PEIM in the BFV provided by the bootloader.

- 6. Bootloader installs FSPM\_ARCH\_CONFIG\_PPI.

- One of the PEIM provided by the bootloader installs a EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI for each FV contained in FSP-M.

- a) The bootloader must not install the EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI(s) for FSP-M until the bootloader is ready for FSP-M to execute.

- b) If FSP-M requires any DynamicEx PCD values, the bootloader must ensure those PCD contain valid data before installing the **EFI\_PEI\_FIRMWARE\_VOLUME\_INFO\_PPI**(s) for FSP-M.

- 8. PEI core will encounter a second PEI core in FSP-M. Because it is not a PEIM, the dispatcher will skip it. PEI core will proceed to dispatch the PEIM in FSP-M.

- 9. The boot flow proceeds the same as step 9 in the primary boot flow from here forwards.

## 8 Intel® FSP API Mode Interface

### 8.1 Entry-Point Invocation Environment

There are some requirements regarding the operating environment for Intel® FSP execution. The bootloader is responsible to set up this operating environment before calling the Intel® FSP API.

These conditions have to be met before calling any entry point (otherwise, the behavior is not determined). These conditions include:

- The system is in flat 32-bit mode.

- Both the code and data selectors should have full 4GB access range.

- Interrupts should be turned off.

- The FSP API should be called only by the system BSP, unless otherwise noted.

- Sufficient stack space should be available for the FSP API function to execute. Consult the *Integration Guide* for platform specific stack space requirements.

Other requirements needed by individual FSP API will be covered in the respective sections.

#### 8.2 Data Structure Convention

All data structure definitions should be packed using compiler provided directives such as **#pragma pack(1)** to avoid alignment mismatch between the FSP and the bootloader.

### 8.3 Entry-Point Calling Convention