### Intel Atom<sup>®</sup> x6000E Series, and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series Processors for IoT Applications

**Datasheet, Volume 1**

May 2024 Revision 1.9

Document Number: 636112-1.9

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

No computer system can provide absolute security under all conditions. Intel<sup>®</sup> Trusted Execution Technology (Intel<sup>®</sup> TXT) requires a computer system with Intel<sup>®</sup> Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). The MLE could consist of a virtual machine monitor, an OS or an application. In addition, Intel TXT requires the system to contain a TPM v1.2, as defined by the Trusted Computing Group and specific software for some uses. For more information, see http://www.intel.com/technology/security/

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

Intel<sup>®</sup> High Definition Audio (Intel<sup>®</sup> HD Audio): Requires an Intel<sup>®</sup> HD Audio enabled system. Consult your PC manufacturer for more information. Sound quality will depend on equipment and actual implementation. For more information about Intel<sup>®</sup> HD Audio, refer to http://www.intel.com/design/chipsets/hdaudio.htm

Hyper-Threading Technology requires a computer system with a processor supporting HT Technology and an HT Technologyenabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. For more information including details on which processors support HT Technology, see <a href="http://www.intel.com/info/hyperthreading">http://www.intel.com/info/hyperthreading</a>.

Enhanced Intel SpeedStep<sup>®</sup> Technology See the Processor Spec Finder or contact your Intel representative for more information.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel<sup>®</sup> 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="https://www.intel.com/products/processor\_number">www.intel.com/products/processor\_number</a> for details.

The Bluetooth® word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by Intel is under license.

$\bigcirc$  Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

### Contents

| 1 | Intro                                                                                                                                                 | 17 Juction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1                                                                                                                                                   | About this Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 1.2                                                                                                                                                   | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 1.3                                                                                                                                                   | Processor Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 1.4                                                                                                                                                   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 1.5                                                                                                                                                   | Intel Atom® x6000E Series processors, Intel® Pentium® and Celeron® N and J Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                                                                                                                       | processors Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 1.6                                                                                                                                                   | Processor SKUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 1.7                                                                                                                                                   | Processor Volatility Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2 | Techn                                                                                                                                                 | ologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2 | 2.1                                                                                                                                                   | Tremont ISA Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 2.2                                                                                                                                                   | Security Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 2.2                                                                                                                                                   | Power and Performance Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| _ |                                                                                                                                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3 |                                                                                                                                                       | r Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 3.1                                                                                                                                                   | Power Management States Supported40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 3.2                                                                                                                                                   | Processor IA Core Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 3.3                                                                                                                                                   | PM Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 3.4                                                                                                                                                   | Processor Voltage Rails                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 3.5                                                                                                                                                   | Voltage Rail Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.6                                                                                                                                                   | Intel® Programmable Services Engine (Intel® PSE) Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 3.7                                                                                                                                                   | SMI#/SCI Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 3.8                                                                                                                                                   | Sleep States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 3.9                                                                                                                                                   | Event Input Signals and Their Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 3.10                                                                                                                                                  | Reset Behavior73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4 | Thern                                                                                                                                                 | nal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4 | Thern<br>4.1                                                                                                                                          | Thermal and Power Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4 |                                                                                                                                                       | Thermal and Power Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4 | 4.1                                                                                                                                                   | Thermal and Power Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4 | 4.1<br>4.2<br>4.3                                                                                                                                     | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 4.1<br>4.2<br>4.3                                                                                                                                     | Thermal and Power Specifications       76         Processor Thermal Management       77         PCH Thermal Management       86         pry       89                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 4.1<br>4.2<br>4.3<br>Memo                                                                                                                             | Thermal and Power Specifications       76         Processor Thermal Management       77         PCH Thermal Management       86         pry       89         System Memory Interface       89                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.1<br>4.2<br>4.3<br>Memo<br>5.1                                                                                                                      | Thermal and Power Specifications       76         Processor Thermal Management       77         PCH Thermal Management       86         pry       89         System Memory Interface       89         Power Management       99                                                                                                                                                                                                                                                                                                                                  |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3                                                                                                        | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp                                                                                                | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107                                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1                                                                                         | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107                                                                                                                                                                                                                                                                                                                                                                   |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2                                                                                  | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109                                                                                                                                                                                                                                                                                                                                        |

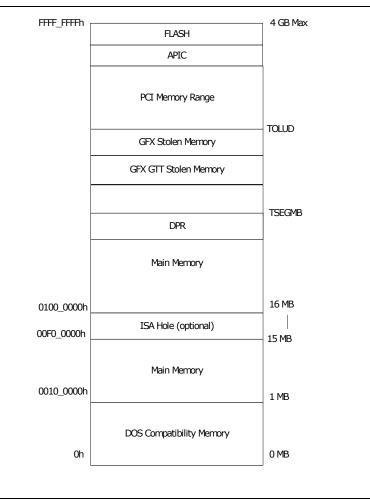

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3                                                                           | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB – TOLUD)112                                                                                                                                                                                                                                                                                       |

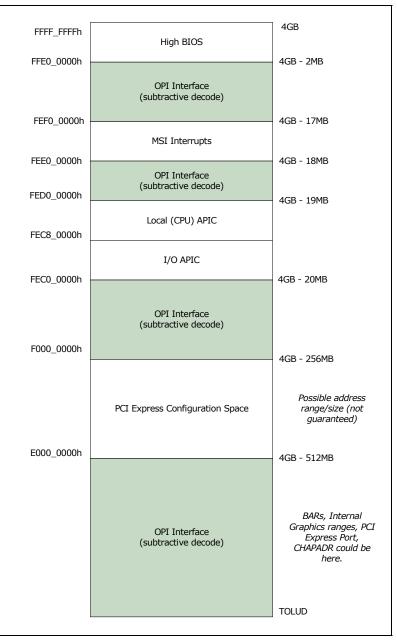

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4                                                                    | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114                                                                                                                                                                                                                                             |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                             | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116                                                                                                                                                                                           |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                      | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB – TOLUD)112PCI Memory Address Range (TOLUD – 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116Graphics Memory Address Ranges118                                                                                                                                                          |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                               | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB – TOLUD)112PCI Memory Address Range (TOLUD – 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116Graphics Memory Address Ranges118System Management Mode (SMM)119                                                                                                                           |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                        | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Ranges118System Management Mode (SMM)119SMM and VGA Access Through GTT TLB119                                                                                                                                      |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9                                 | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range.109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116Graphics Memory Address Ranges118System Management Mode (SMM)119SMM and VGA Access Through GTT TLB119Legacy VGA and I/O Range Decode Rules120                                             |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10                         | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Ranges118System Management Mode (SMM)119SMM and VGA Access Through GTT TLB119Legacy VGA and I/O Range Decode Rules120I/O Mapped Registers122                                                                       |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11                 | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116Graphics Memory Address Ranges118System Management Mode (SMM)119SMM and VGA Access Through GTT TLB119Legacy VGA and I/O Range Decode Rules120I/O Mapped Registers122PCH Address Mapping123 |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12         | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86Dry89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116Graphics Memory Address Ranges118System Management Mode (SMM)119Legacy VGA and I/O Range Decode Rules120I/O Mapped Registers122PCH Address Mapping123Variable I/O Decode Ranges126         |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13 | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86ory89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Ranges118System Management Mode (SMM)119SMM and VGA Access Through GTT TLB119Legacy VGA and I/O Range Decode Rules120I/O Mapped Registers122PCH Address Mapping123Variable I/O Decode Ranges126Memory Map128       |

| 5 | 4.1<br>4.2<br>4.3<br>Memo<br>5.1<br>5.2<br>5.3<br>Mapp<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13 | Thermal and Power Specifications76Processor Thermal Management77PCH Thermal Management86Dry89System Memory Interface89Power Management99IBECC102ing Address Spaces107System Address Mapping107DOS Legacy Address Range109Lower Main Memory Address Range (1 MB - TOLUD)112PCI Memory Address Range (TOLUD - 4 GB)114Upper Main Memory Address Space (4 GB to TOUUD)116Graphics Memory Address Ranges118System Management Mode (SMM)119Legacy VGA and I/O Range Decode Rules120I/O Mapped Registers122PCH Address Mapping123Variable I/O Decode Ranges126         |

| 7.2                                                                                                             | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135                                                                                            |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

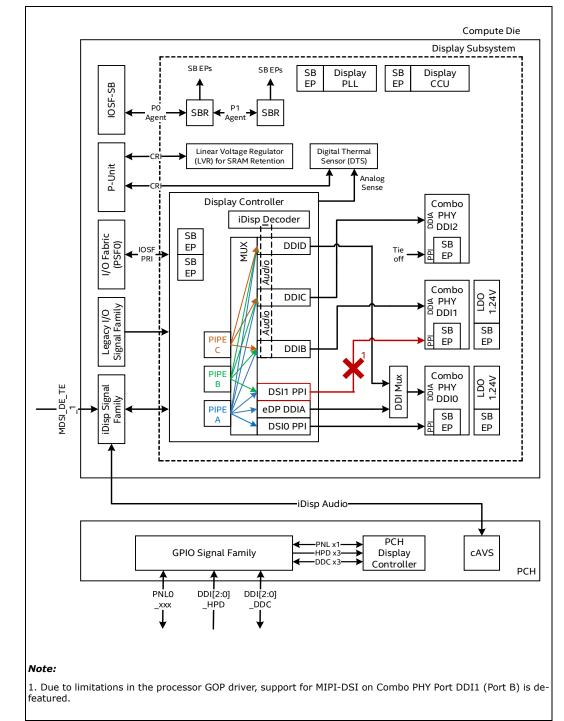

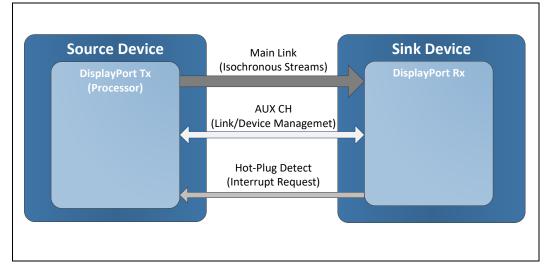

| 8 Disp<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.1<br>8.1<br>8.1<br>8.1<br>8.1<br>3.1 | <ul> <li>Diay</li> <li>Display Technologies</li> <li>General Capabilities</li> <li>Display Features</li> <li>Port Configuration</li> <li>Display Interfaces</li> <li>Multi-Stream Transport (MST) Configuration</li> <li>Multiple Display Configurations</li> <li>High-bandwidth Digital Content Protection (HDCP)</li> <li>Display Technologies</li> <li>D PCH Display</li> <li>Panel Control Signals</li> <li>Embedded DisplayPort (eDP) Signals</li> <li>MIPI DSI Signals</li> <li>MIPI DSI Signals</li> <li>Minerface (DDI) Signals</li> </ul> | 136<br>136<br>137<br>137<br>139<br>141<br>141<br>141<br>142<br>146<br>147<br>147<br>147<br>149 |

| 9 Flex<br>9.1<br>9.2<br>9.3<br>9.4                                                                              | tible I/O<br>Acronyms<br>HSIO Controller (PCH)<br>Overview/Functional Description<br>Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 150<br>150<br>152                                                                              |

| 10 Aud<br>10.<br>10.<br>10.<br>10.<br>10.<br>10.                                                                | <ul> <li>Legacy Audio Interface - Signal Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 154<br>155<br>156<br>158<br>158                                                                |

| 11 Univ<br>11.<br>11.<br>11.                                                                                    | 2 Integrated Pull-Ups and Pull-Down11.3 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 160<br>165                                                                                     |

| 12 PCI<br>12<br>12<br>12<br>12<br>12<br>12<br>12                                                                | <ul> <li>Signal Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 166<br>166<br>166<br>167<br>167                                                                |

| 13 Ser<br>13.<br>13.<br>13.<br>13.<br>13.<br>13.<br>13.                                                         | <ul> <li>References</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 175<br>175<br>175<br>175<br>175                                                                |

| 14 Hos<br>14.<br>14.<br>14.<br>14.                                                                              | 2 Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 181<br>181<br>181                                                                              |

| 15 | 15.1 Ove<br>15.2 Fea<br>15.3 Gbb<br>15.4 Gbb<br>15.5 Ext<br>15.6 Sig<br>15.7 Gbb  | hernet Controller and Time-Sensitive Networking                                                                                                                                                                                               | 3<br>4<br>8<br>9<br>0<br>2 |

|----|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|    | 15.10 Reg                                                                         | oported System Configurations                                                                                                                                                                                                                 | 6                          |

| 16 | 16.1 Fur                                                                          | Serial Peripheral Interface (eSPI)                                                                                                                                                                                                            | 7                          |

| 17 | 17.1 Acr<br>17.2 Fea<br>17.3 Sig<br>17.4 Inte<br>17.5 I/O<br>17.6 Fur<br>17.7 VCC | ipheral Interface (SPI) Flash Memory and TPM Only.214ronyms214inture Overview.214nal Description211egrated Pull-Ups and Pull-Downs.211O Signal Planes and States216inctional Description216CSPI Voltage (3.3V or 1.8V) Selection222gisters224 | 4<br>5<br>5<br>6<br>3      |

| 18 | 18.1 Inte<br>18.2 Inte                                                            | 5)22!<br>el® Serial I/O Universal Asynchronous Receiver/Transmitter (UART) Controllers22!<br>el® Serial I/O Inter-Integrated Circuit (I2C) Controllers                                                                                        | 5<br>3                     |

| 19 | 19.1 em                                                                           | 244<br>bedded Multi Media Card (eMMC*)244<br>cure Digital eXtended Capacity (SDXC)24                                                                                                                                                          | 4                          |

| 20 | 20.1 Inte<br>20.2 PCF<br>20.3 PCF<br>20.4 Sur                                     | 24<br>egrated Clock Controller (ICC)                                                                                                                                                                                                          | 7<br>7<br>2<br>2           |

| 21 | 21.1 Ove<br>21.2 Pad<br>21.3 Fur<br>21.4 GPI                                      | urpose Input and Output (GPIO)                                                                                                                                                                                                                | 4<br>4<br>3                |

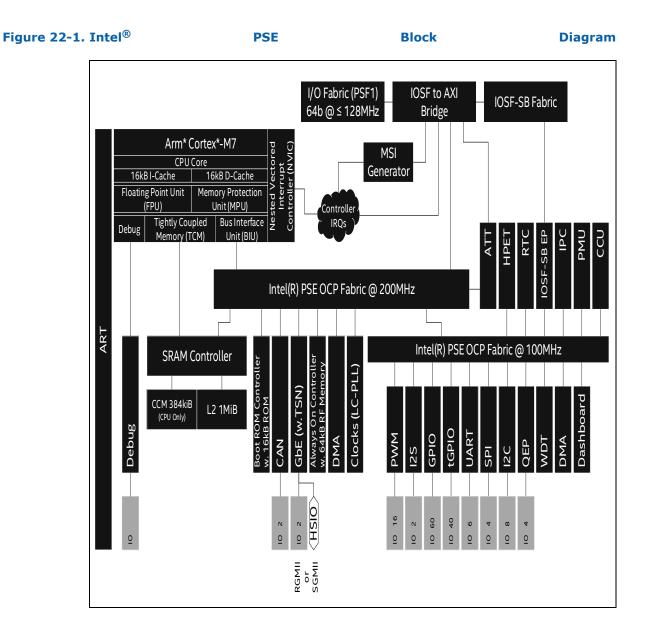

| 22 | 22.1 Ove<br>22.2 Fur<br>22.3 Blo<br>22.4 Inte<br>22.5 Arm                         | ogrammable Services Engine (Intel® PSE)                                                                                                                                                                                                       | 6<br>6<br>7<br>8<br>9      |

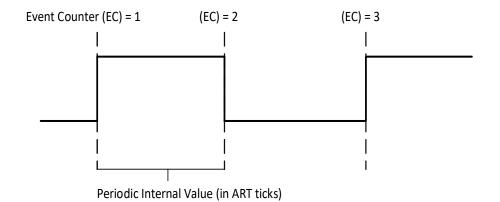

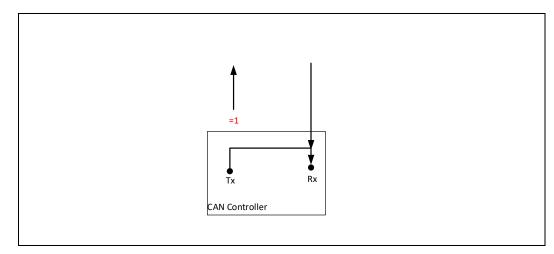

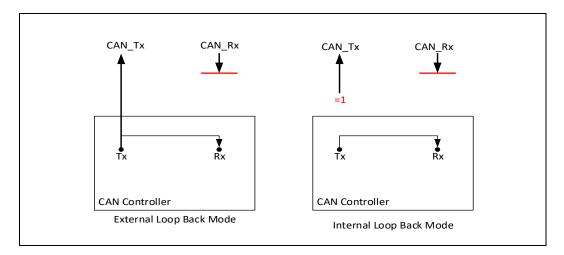

|    | 22.10<br>22.11<br>22.12<br>22.13<br>22.14<br>22.15<br>22.16<br>22.17<br>22.18<br>22.19<br>22.20<br>22.21<br>22.22 | Clock Control Unit (CCU) and PLL<br>Power Management Unit (PMU)<br>Address Translation Table (ATT)<br>AON Controller.<br>Timer<br>I/O Ownership and Interrupts<br>Controller Area Network (CAN) Bus Controller<br>I2C Controller<br>UART Controller<br>SPI Controller<br>SPI Controller<br>Time-Aware GPIO.<br>I2S Controller.<br>Pulse Width Modulation (PWM)<br>Quadrature Encoder Peripheral (QEP)<br>Time Synchronous Support.<br>DMA | 311<br>311<br>312<br>312<br>317<br>334<br>352<br>378<br>391<br>393<br>400<br>407<br>410<br>424 |

|----|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 23 | 23.1<br>23.2<br>23.3<br>23.4                                                                                      | Safety Island (Intel® SI)<br>Feature Overview<br>Error Reporting<br>Integrated Pull-Ups and Pull - Downs<br>I/O Signal Planes and States<br>Registers                                                                                                                                                                                                                                                                                     | 437<br>440<br>442<br>442                                                                       |

| 24 | 24.1                                                                                                              | onal Safety (FuSa)<br>Overview<br>Processor and FuSa Safety Package                                                                                                                                                                                                                                                                                                                                                                       | 444                                                                                            |

| 25 | 25.1                                                                                                              | ry to Sideband Bridge (P2SB)<br>Overview<br>Integrated Error Handler<br>Registers                                                                                                                                                                                                                                                                                                                                                         | 445<br>446                                                                                     |

| 26 | 26.1<br>26.2<br>26.3<br>26.4<br>26.5<br>26.6<br>26.7                                                              | y Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                              | 448<br>451<br>453<br>459<br>464<br>468<br>473                                                  |

| 27 |                                                                                                                   | rap                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

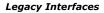

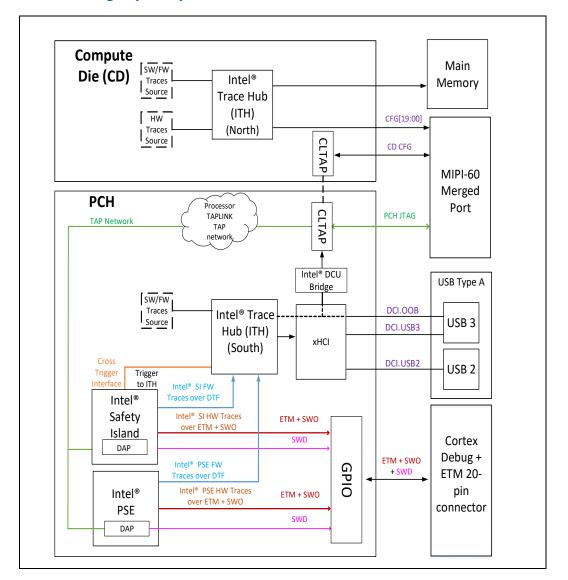

| 28 | 28.1<br>28.2<br>28.3<br>28.4<br>28.5<br>28.6                                                                      | nd Debug<br>Debug Capability and Technologies<br>Signal Description<br>Intel® Atom Debug and Tool.<br>Arm* Debug and Tool<br>Debug Interface Availability<br>References                                                                                                                                                                                                                                                                   | 479<br>484<br>485<br>487<br>490<br>490                                                         |

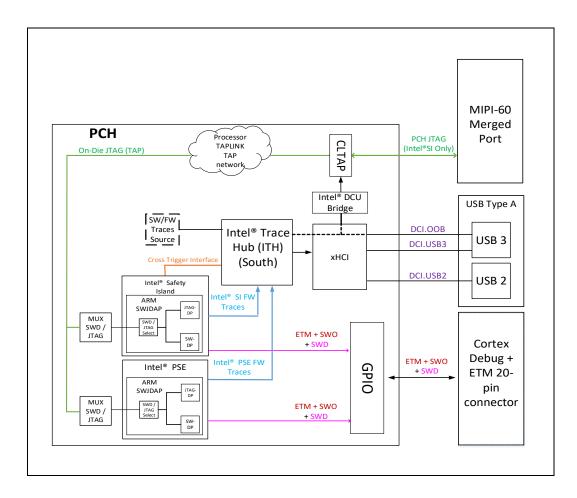

| 29 | Intel®<br>29.1<br>29.2<br>29.3                                                                                    | ) Time Coordinated Computing<br>Intel® Time Coordinated Computing Overview<br>Intel® Time Coordinated Computing Features<br>Intel® TCC Tools                                                                                                                                                                                                                                                                                              | 491<br>492                                                                                     |

| 30 | Globa   | al Device IDs                                  | 500 |

|----|---------|------------------------------------------------|-----|

|    | 30.1    | Overview                                       | 500 |

|    | 30.2    | PCH Global Device IDs                          |     |

|    | 30.3    | PCH ACPI IDs                                   |     |

|    | 30.4    | Compute Die Global Device ID                   | 504 |

| 31 | Proces  | ssor Ball Map and Pin Location                 | 507 |

| 32 | Packa   | ge Information                                 | 546 |

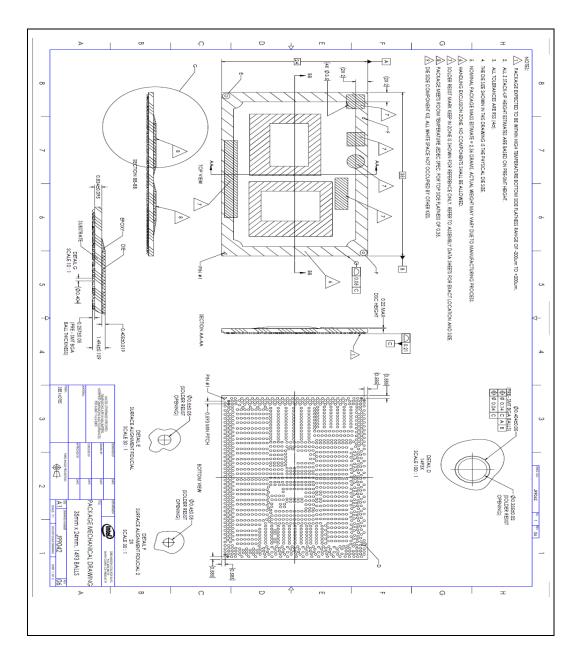

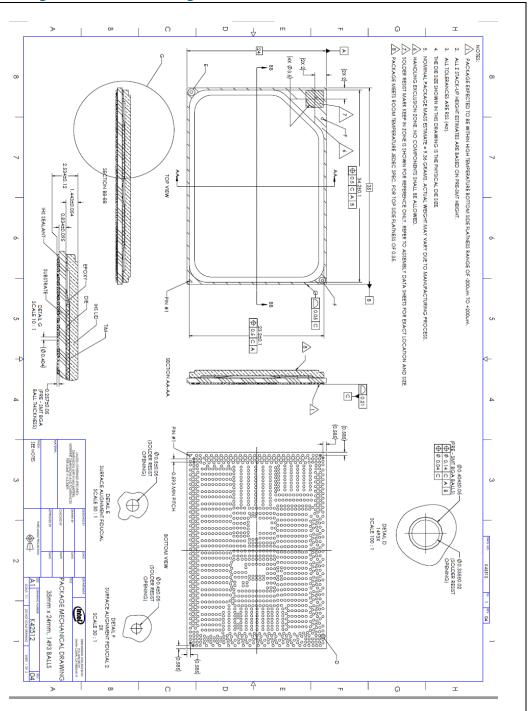

|    | 32.1    | Package Mechanical Drawing - Non IHS           | 546 |

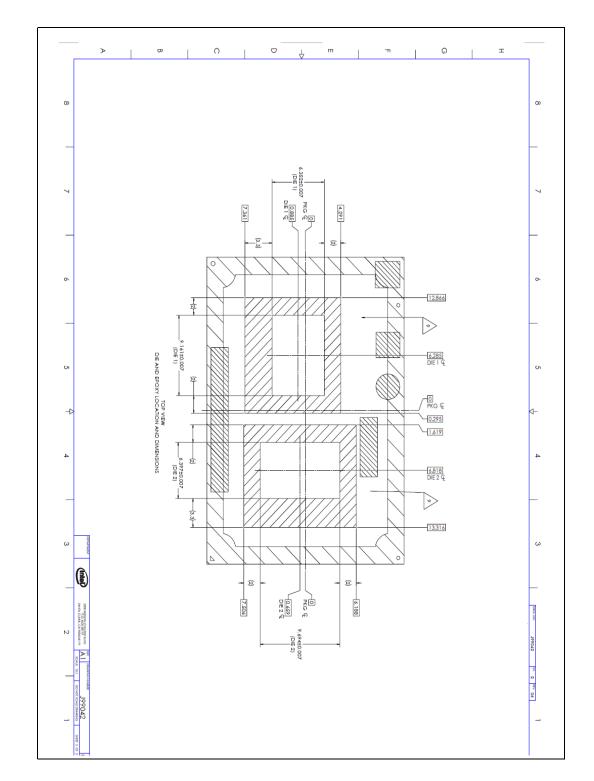

|    | 32.2    | Package Mechanical Drawing - IHS               |     |

| 33 | Proces  | ssor Transaction Router (PTR)                  | 549 |

|    | 33.1    |                                                |     |

|    | 33.2    | I/O Port (IOP)                                 | 549 |

| 34 | Machi   | ne Check Architecture (MCA)                    | 551 |

|    | 34.1    | Overview                                       |     |

|    | 34.2    | Machine Check Architecture (MCA) MSR Addresses | 551 |

|    | 34.3    | Registers                                      | 553 |

| 35 | Intel®  | © Converged Security Engine (Intel® CSE)       | 554 |

|    |         | Overview                                       |     |

| 36 | Electri | ical Specifications                            | 557 |

|    | 36.1    |                                                |     |

|    | 36.2    | Storage Conditions                             |     |

|    | 36.3    | DC Specifications                              |     |

| 37 | Termi   | nology                                         | 583 |

|    |         | ····· , ···                                    |     |

### **List of Figures**

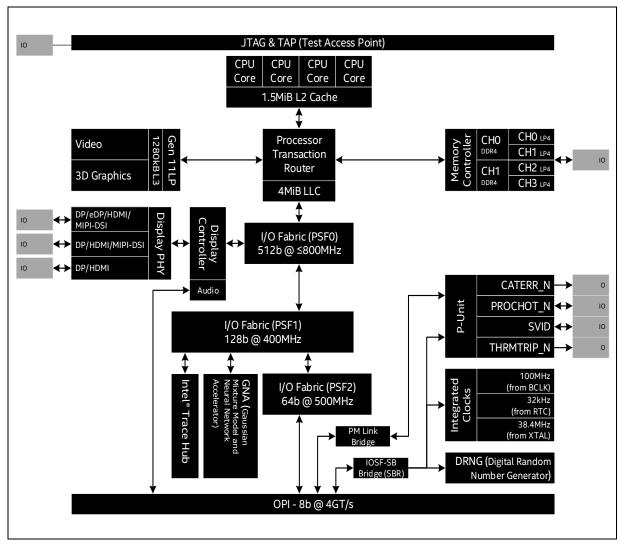

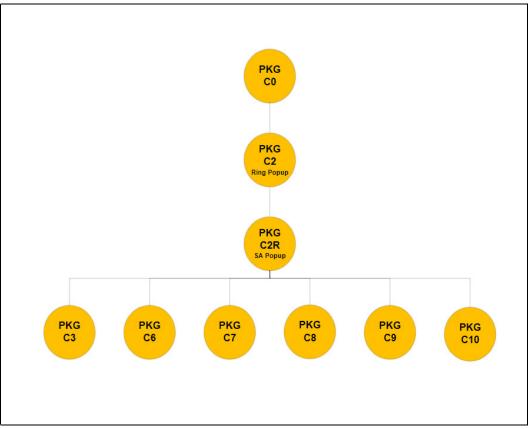

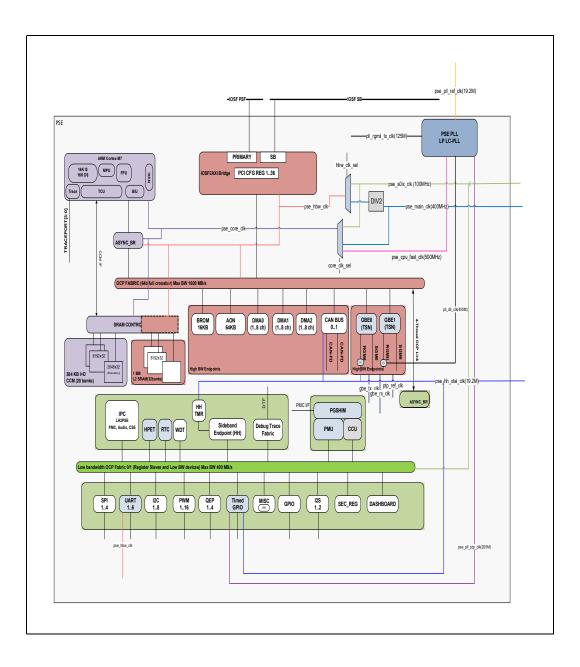

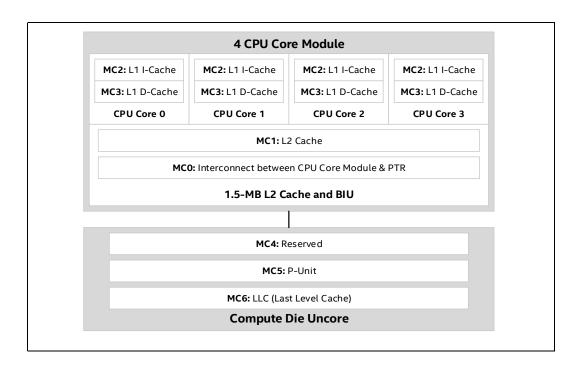

| Figure 1-1Compute Die Block Diagram                                 | 23  |

|---------------------------------------------------------------------|-----|

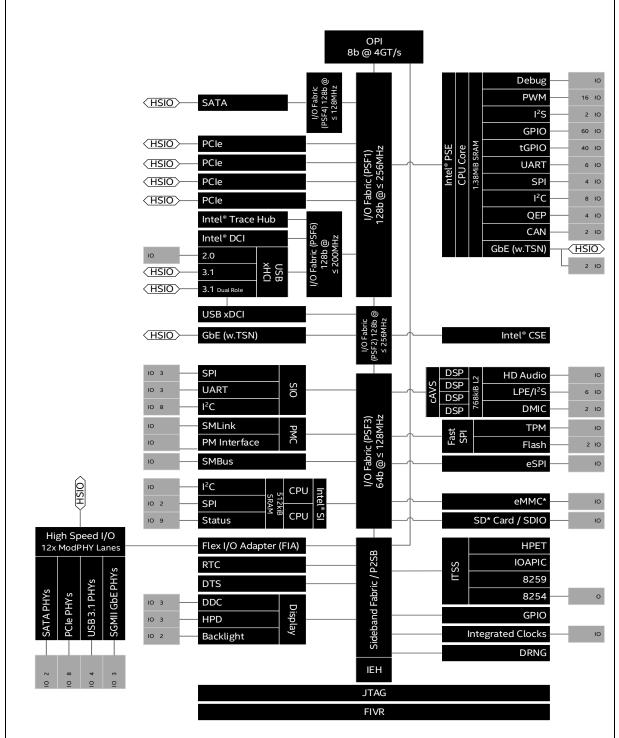

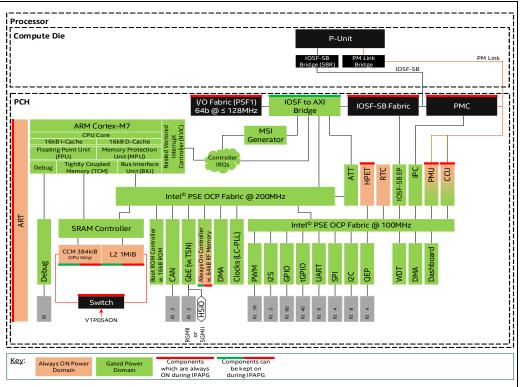

| Figure 1-2PCH Block Diagram                                         | 24  |

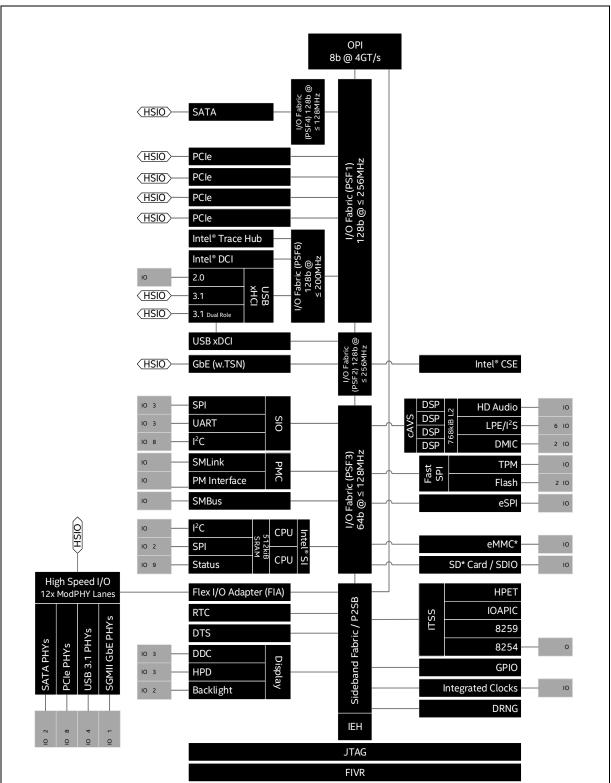

| Figure 1-3PSE Disabled - PCH Block Diagram                          | 25  |

| Figure 3-1System Power States                                       |     |

| Figure 3-21dle Power Management Breakdown of the Processor IA Cores | 44  |

| Figure 3-3Package C-State Entry and Exit                            | 47  |

| Figure 3-4System Power States                                       |     |

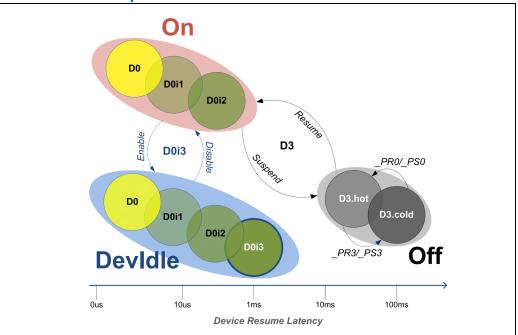

| Figure 3-5Device States Latency                                     | 63  |

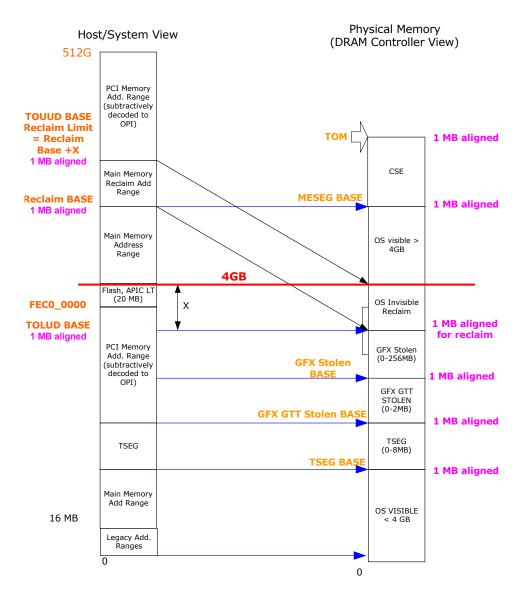

| Figure 6-1System Address Range Example                              | 109 |

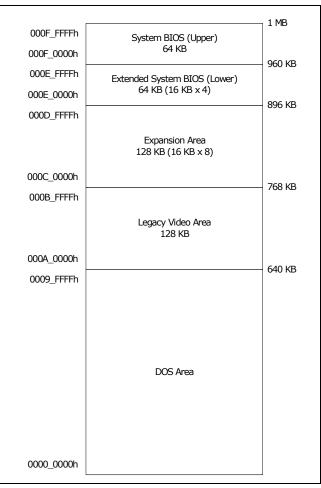

| Figure 6-2DOS Legacy Address Range                                  | 110 |

| Figure 6-3PAM Region Space                                          | 111 |

| Figure 6-4Main Memory Address Range                                 | 112 |

| Figure 6-5PCI Memory Address Range                                  | 115 |

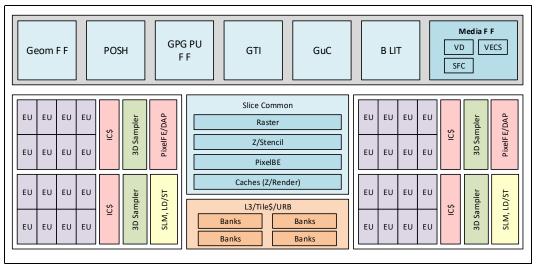

| Figure 7-1Block Diagram                                             | 133 |

| Figure 8-1Display Subsystem Block Diagram                           | 138 |

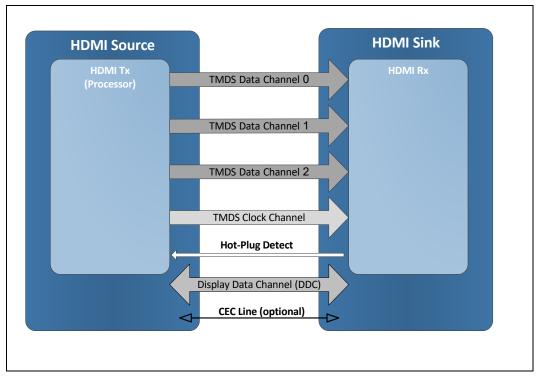

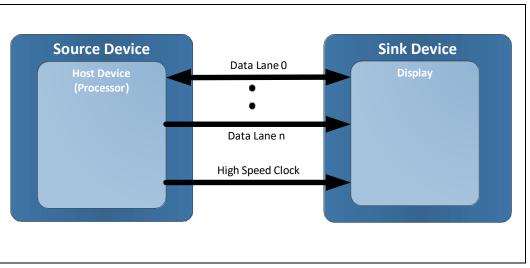

| Figure 8-2DisplayPort Overview                                      | 142 |

| Figure 8-3HDMI Overview                                             |     |

| Figure 8-4MIPI DSI Overview                                         | 145 |

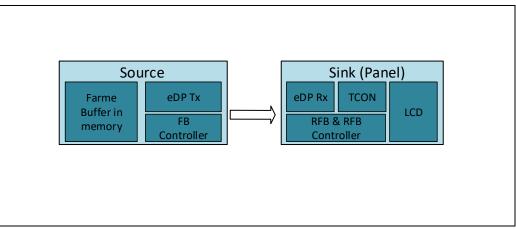

| Figure 8-5Panel Self Refresh Diagram                                | 146 |

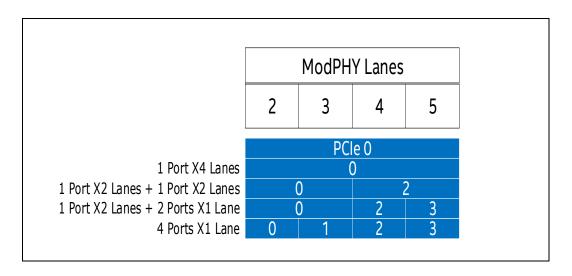

| Figure 9-1HSIO Controller Port Configuration                        |     |

| Figure 9-2HSIO Controller Lanes to x12 ModPHY Lane Multiplexing     |     |

| Figure 9-3Configuration SATA + SGMII GbE                            | 152 |

| Figure 11-1USB 3.1/PCIe*/SATA Port Mapping                                                                             |     |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 12-1PCIE Controller Port Configuration                                                                          |     |

| Figure 12-2Single Virtual Channel PCIe* Controller                                                                     |     |

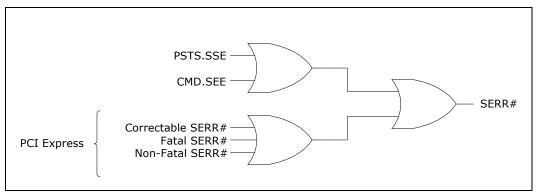

| Figure 12-1Generation of SERR# to Platform                                                                             | 172 |

| Figure 12-3PCI Express* Controller Lane Reversal                                                                       |     |

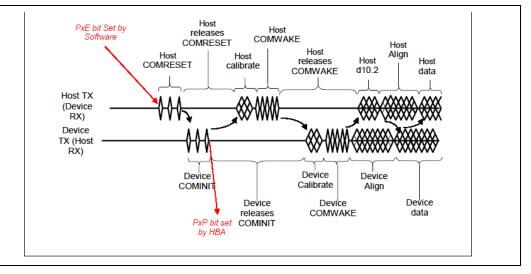

| Figure 13-1Flow for Port Enable/Device Present Bits                                                                    |     |

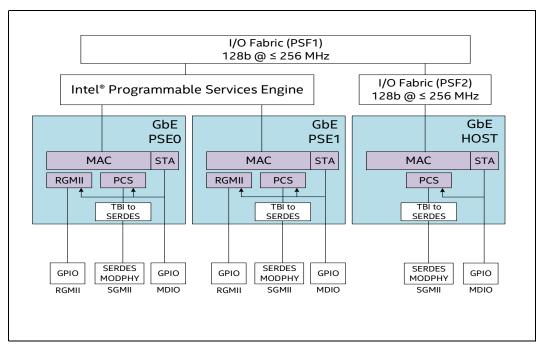

| Figure 15-1GbE-TSN MAC Placement                                                                                       |     |

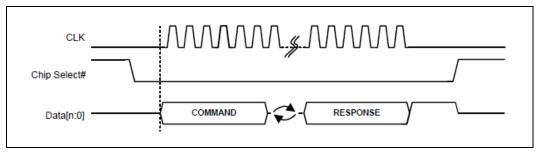

| Figure 16-1Basic eSPI Protocol                                                                                         |     |

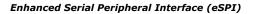

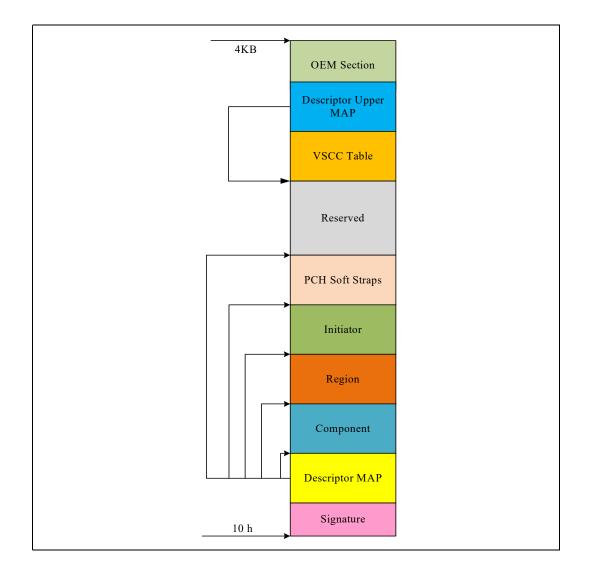

| Figure 17-1Flash Descriptor Regions<br>Figure 18-1UART Serial Protocol                                                 |     |

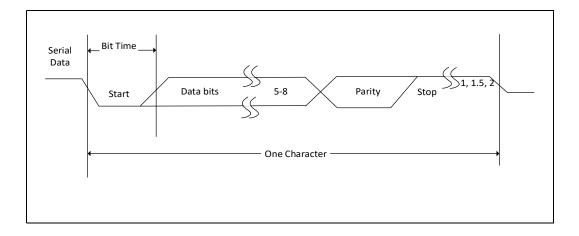

| Figure 18-2UART Receiver Serial Data Sample Points                                                                     | 22/ |

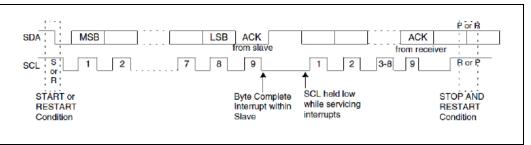

| Figure 18-3Data Transfer on the I2C Bus                                                                                | 220 |

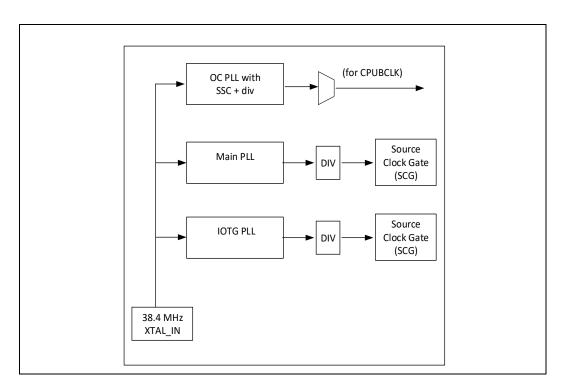

| Figure 20-1Internal Clock Diagram - "iSCLK"                                                                            |     |

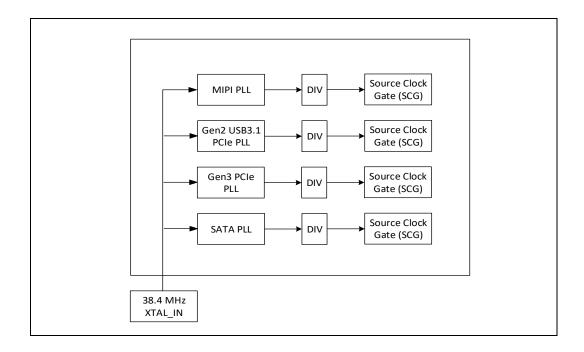

| Figure 20-2Internal Clock Diagram - "modPHY"                                                                           |     |

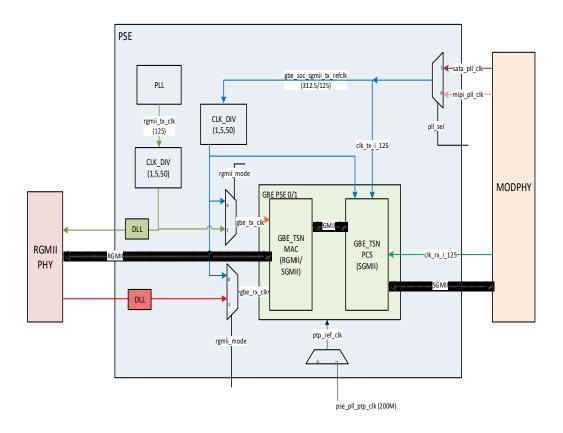

| Figure 20-3PSE_Clocking                                                                                                |     |

| Figure 20-4PSE_GBe Clocking                                                                                            |     |

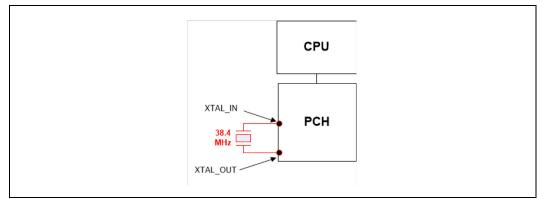

| Figure 20-5PCH ICC XTAL Input Configuration                                                                            |     |

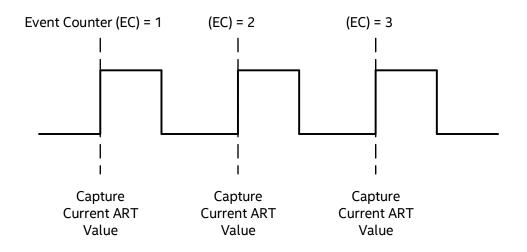

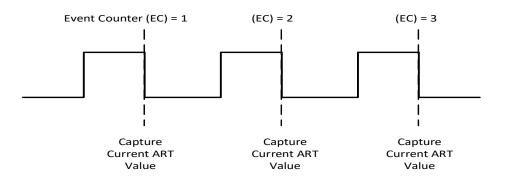

| Figure 21-1Input Capture Rising Edge                                                                                   | 256 |

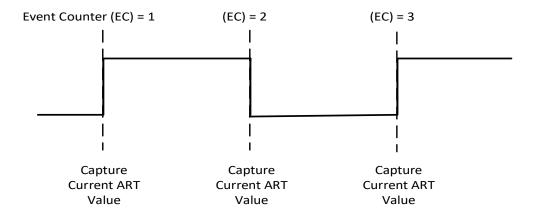

| Figure 21-2Input Capture Falling Edge                                                                                  |     |

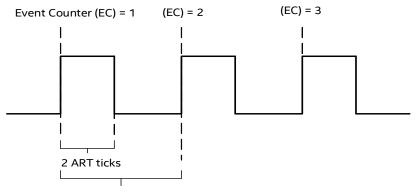

| Figure 21-3Input Capture Both (Toggle) Edge(s)                                                                         |     |

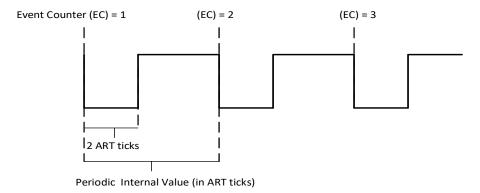

| Figure 21-4Output Generation Rising Pulse                                                                              |     |

| Figure 21-5Output Generation Falling Pulse                                                                             | 258 |

| Figure 21-6Output Generation Toggle Edge                                                                               |     |

| Figure 22-1Intel® PSE Block Diagram                                                                                    |     |

| Figure 22-2Bus monitoring mode                                                                                         |     |

| Figure 22-3Internal Loop Back Mode                                                                                     |     |

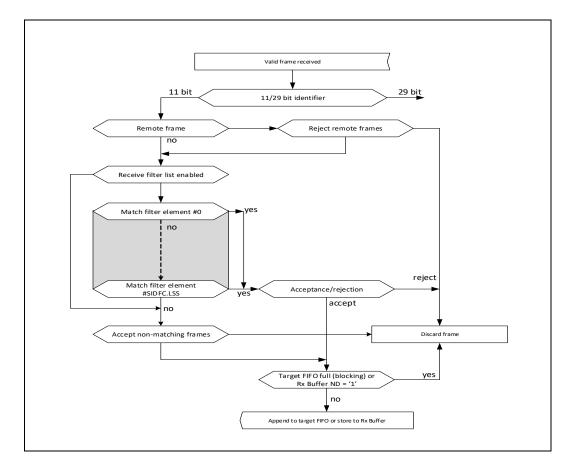

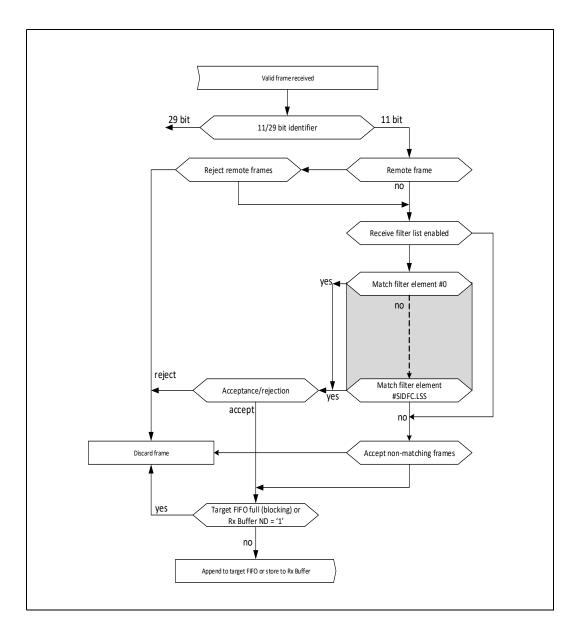

| Figure 22-4Standard Message ID Filter Path                                                                             | 326 |

| Figure 22-5Extended Message ID Filtering                                                                               | 327 |

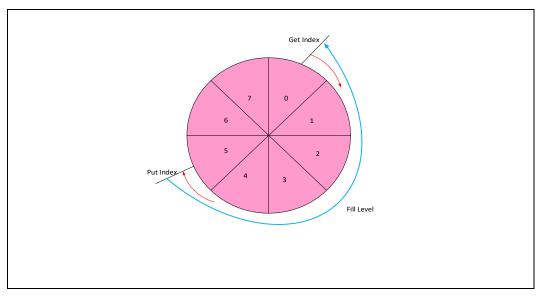

| Figure 22-6Rx FIFO Status.                                                                                             | 328 |

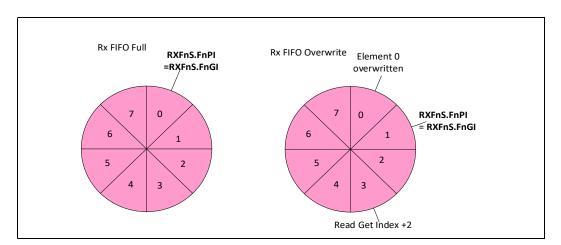

| Figure 22-7Rx FIFO Overflow Handling                                                                                   |     |

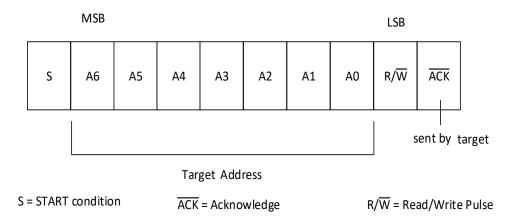

| Figure 22-87-bit Address Format                                                                                        | 338 |

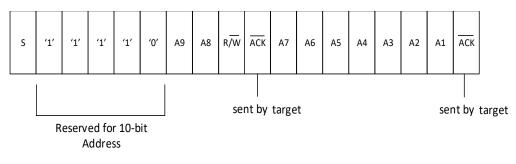

| Figure 22-910-bit address format                                                                                       |     |

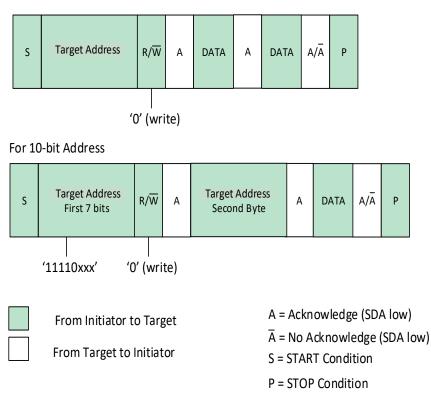

| Figure 22-10 Initiator-Transmitter Protocol                                                                            |     |

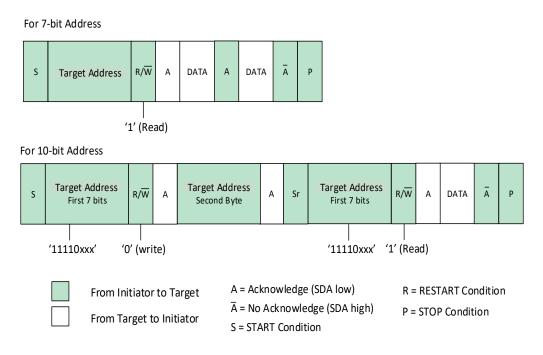

| Figure 22-11Initiator-Receiver Protocol                                                                                |     |

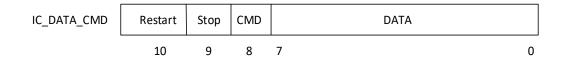

| Figure 22-12IC_DATA_CMD register if IC_EMPTYFIFO_HOLD_MASTER_EN= 1                                                     |     |

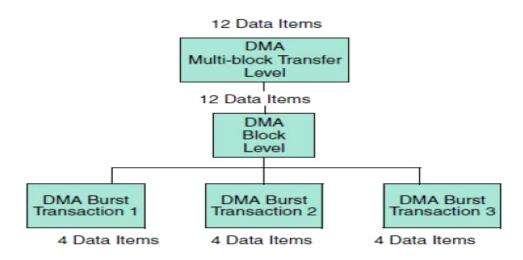

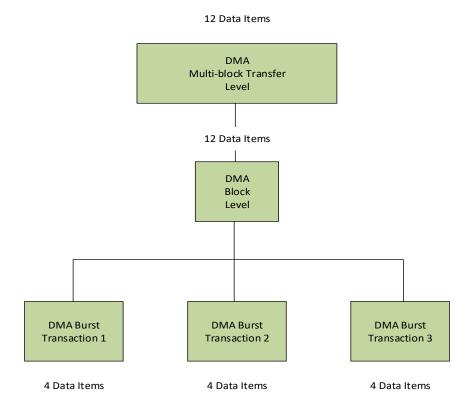

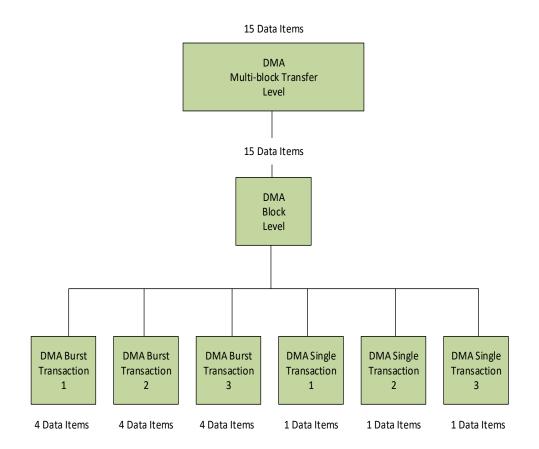

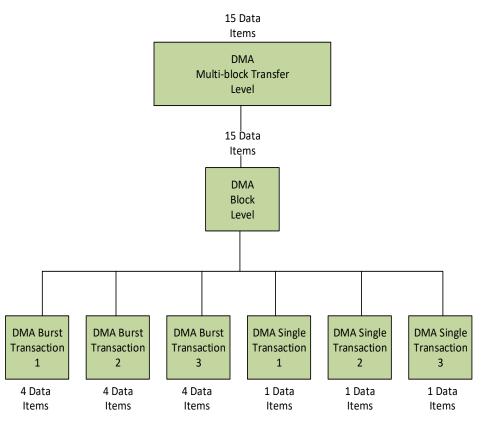

| Figure 22-13Breakdown of DMA Transfer into Burst Transactions                                                          |     |

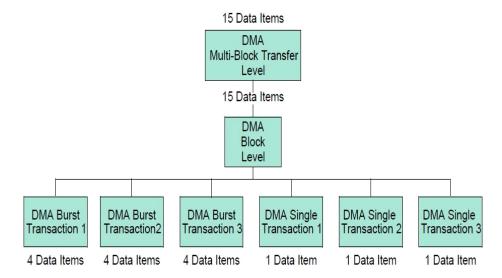

| Figure 22-14Breakdown of DMA Transfer into Single and Burst Transactions                                               |     |

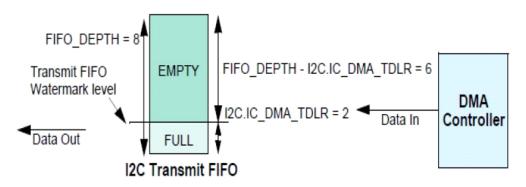

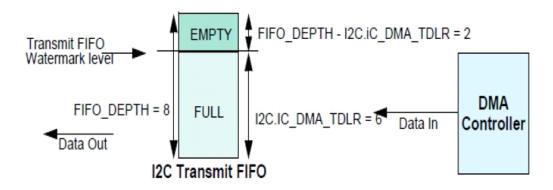

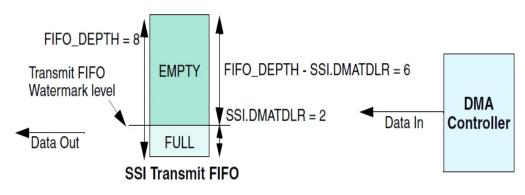

| Figure 22-15Case 1 Watermark Levels                                                                                    |     |

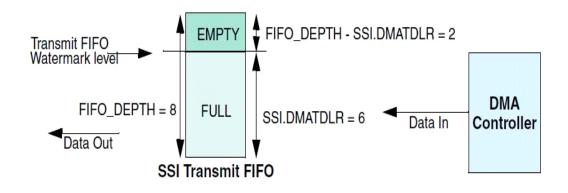

| Figure 22-16Case 2 Watermark Levels                                                                                    |     |

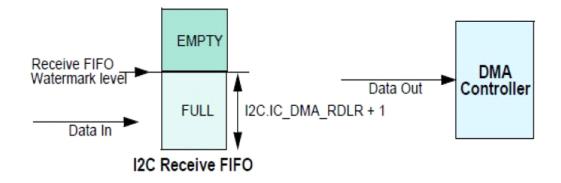

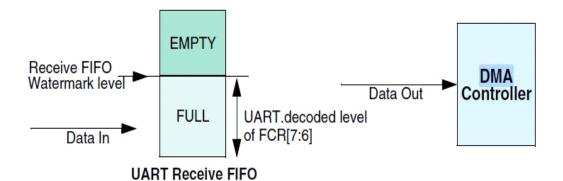

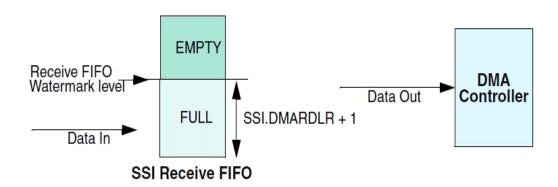

| Figure 22-17I2C Receive FIFO                                                                                           |     |

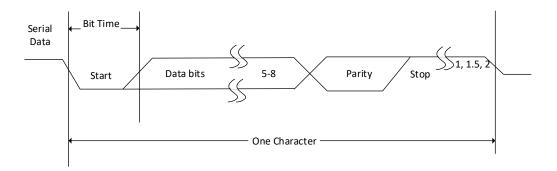

| Figure 22-18Serial Data Format                                                                                         |     |

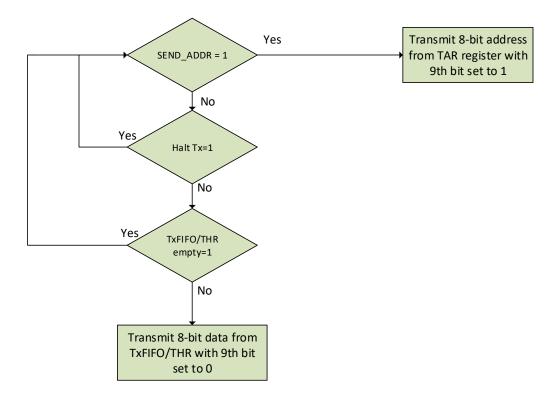

| Figure 22-19Auto Address Transmit Flow Chart                                                                           |     |

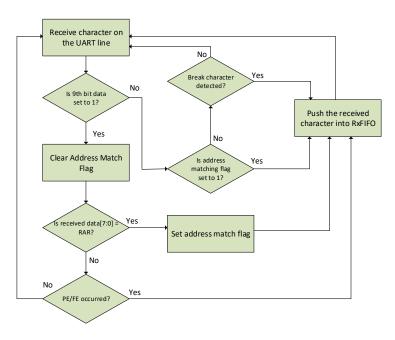

| Figure 22-20Hardware Address Match Receive Mode                                                                        |     |

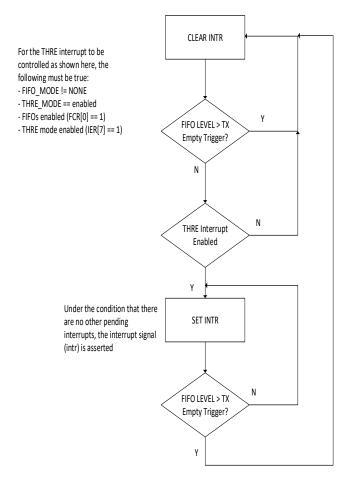

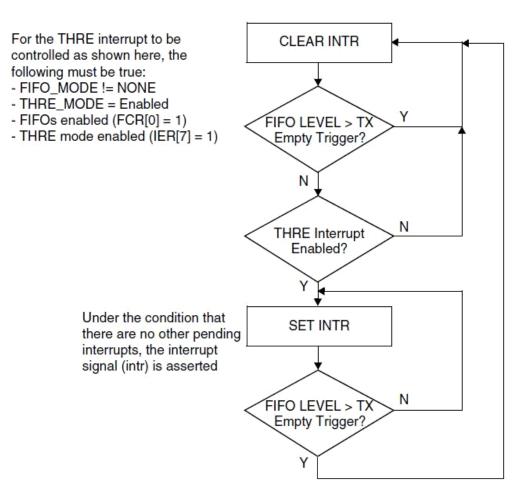

| Figure 22-21Flowchart of Interrupt Generation for Programmable THRE Interrupt Mode                                     |     |

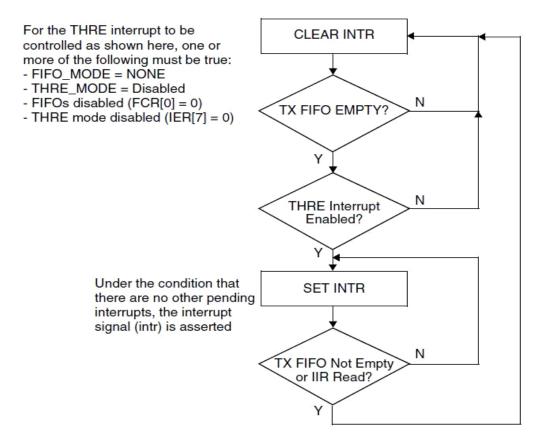

| Figure 22-22Flowchart of Interrupt generation when not in Programmable THRE Interrupt Mod                              | e   |

| 369<br>Figure 22 22Breekdeurs of DMA Transfer inte Burst Transportion                                                  | 271 |

| Figure 22-23Breakdown of DMA Transfer into Burst Transaction                                                           |     |

| Figure 22-24Breakdown of DMA Transfer into Single and Burst Transactions                                               |     |

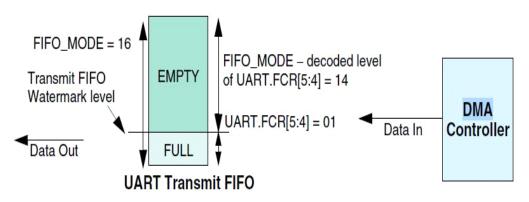

| Figure 22-25Case 1 Watermark Levels                                                                                    |     |

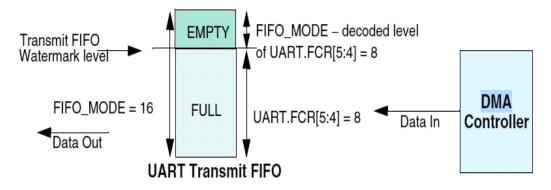

| Figure 22-26Case 2 Watermark Levels<br>Figure 22-27UART Receive FIFO                                                   |     |

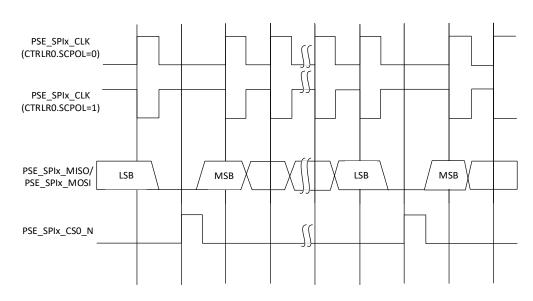

| Figure 22-270ART Receive FIFO<br>Figure 22-28Serial Format Continuous Transfers (SCPH = 0) when SSI_SCPH0_SSTOGGLE = 1 |     |

| 379                                                                                                                    | L   |

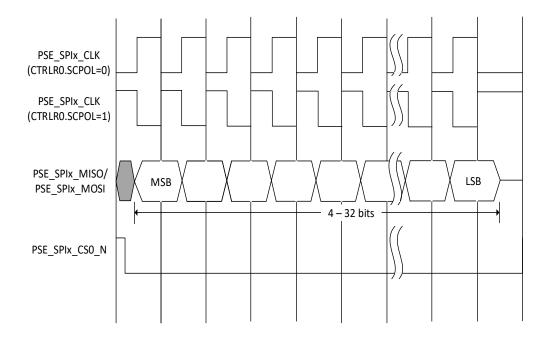

| Figure 22-29SPI Serial Format (SCPH=1)                                                                                 | 380 |

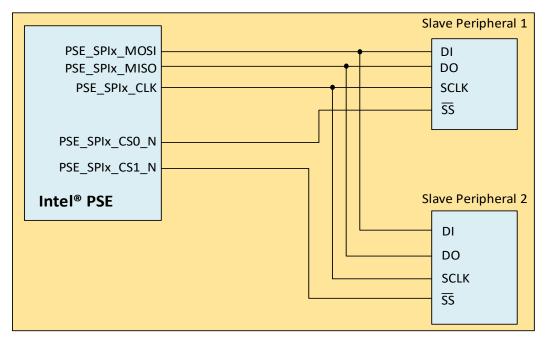

| Figure 22-30SPI controller Configured as Initiator Device                                                              |     |

|                                                                                                                        |     |

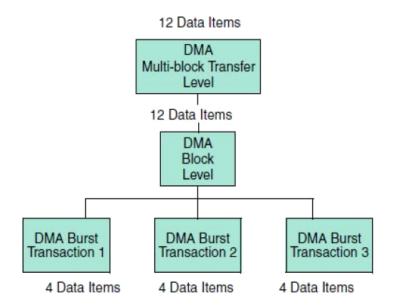

| Figure 22-31Breakdown of DMA Transfer into Burst Transactions              |     |

|----------------------------------------------------------------------------|-----|

| Figure 22-32Breakdown of DMA Transfer into Single and Burst Transactions   |     |

| Figure 22-33Case 1 Watermark Levels                                        |     |

| Figure 22-34Case 2 Watermark Levels                                        |     |

| Figure 22-35SPI Controller Receive FIFO                                    |     |

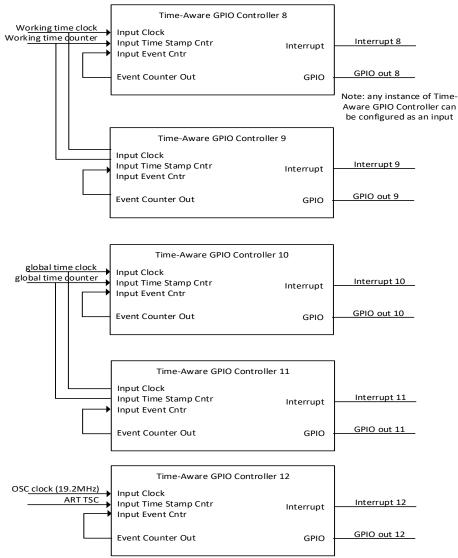

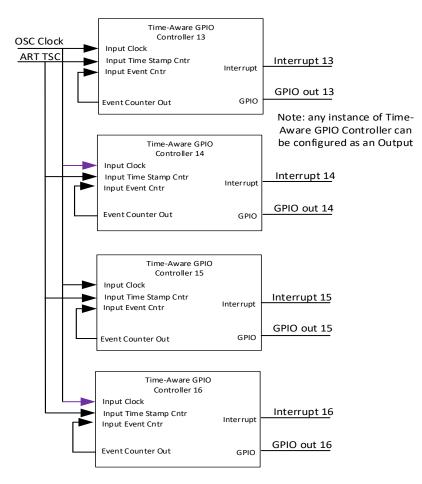

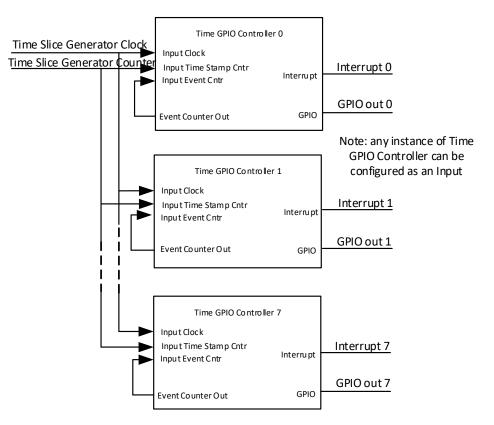

| Figure 22-36Sync out configuration                                         |     |

| Figure 22-37Sync In Configuration                                          |     |

| Figure 22-38Time Slice Generator controller                                |     |

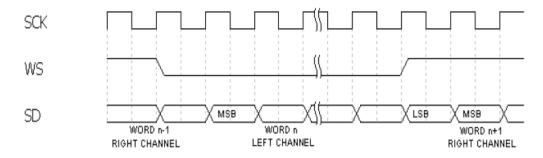

| Figure 22-39Example of basic transmission for I2S bus                      | 401 |

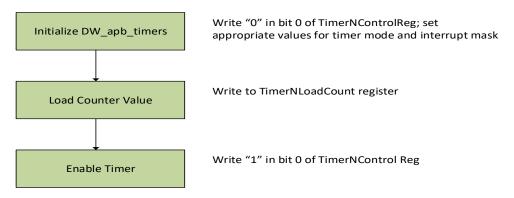

| Figure 22-40Timers Usage Flow Diagram                                      |     |

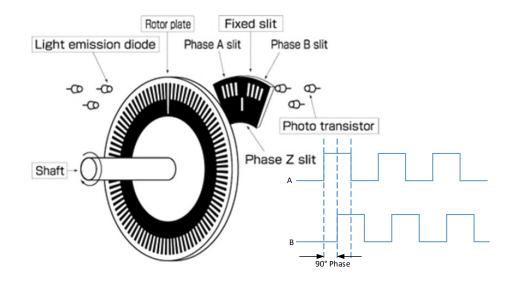

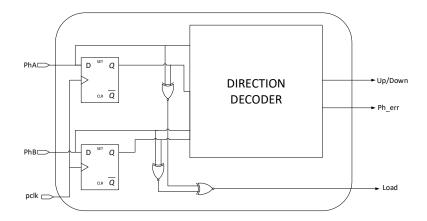

| Figure 22-41Block Diagram of QEP                                           | 411 |

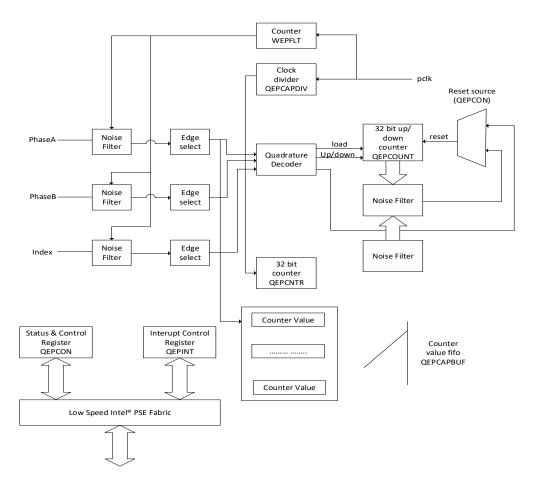

| Figure 22-42Controller Block Diagram                                       |     |

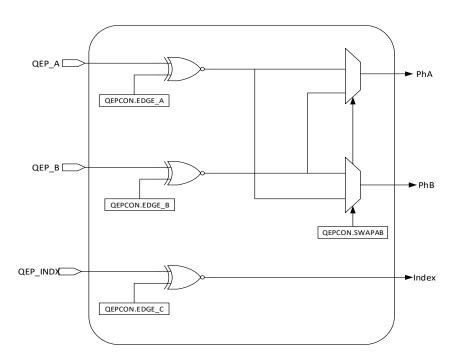

| Figure 22-43Edge Selection and Phase Swapping Block Diagram                |     |

| Figure 22-44Quadrature Decoder Block Diagram                               |     |

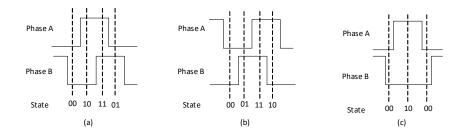

| Figure 22-45Phase relationship example between PhA and PhB signals         |     |

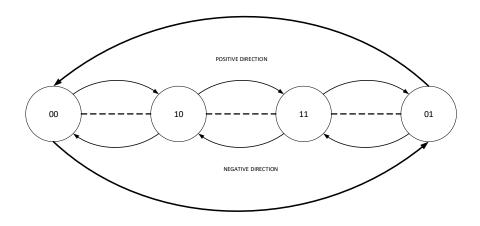

| Figure 22-46State diagram for direction decoding                           | 416 |

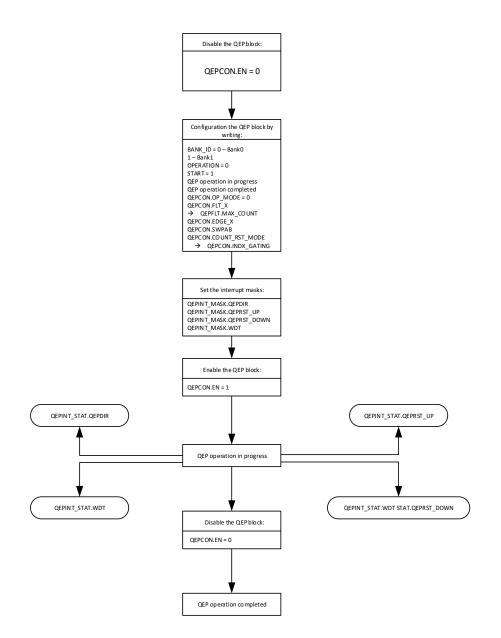

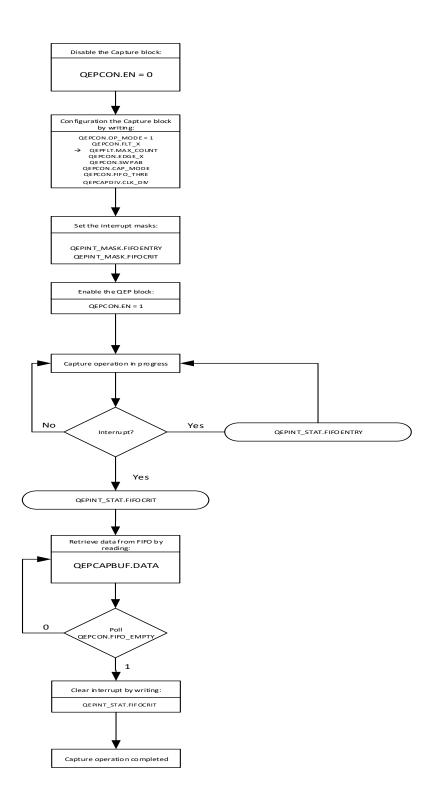

| Figure 22-47Software Flow Diagram for QEP Functionality                    | 421 |

| Figure 22-48Software flow diagram for Capture Compare Functionality        |     |

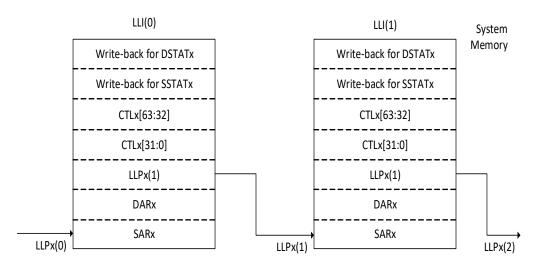

| Figure 22-49DMA Multi-Block and Update Flowchart                           |     |

| Figure 22-50Multi-Block Transfer Setup using Linked Lists                  |     |

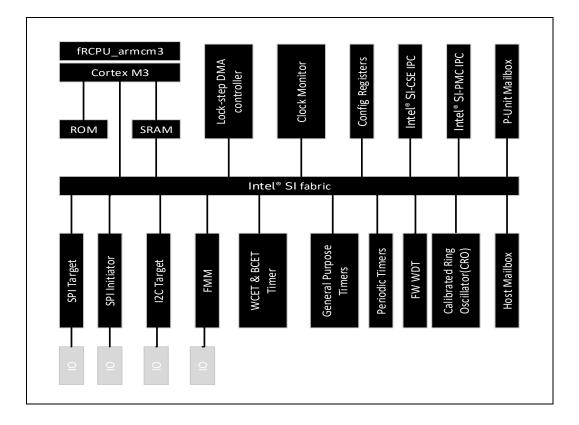

| Figure 23-1Intel® SI Block Diagram                                         |     |

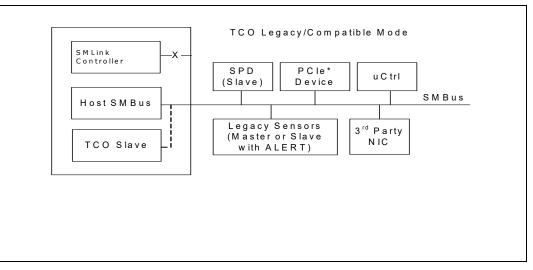

| Figure 26-1TCO Compatible Mode SMBus Configuration                         |     |

| Figure 28-10verall Debug Capability                                        |     |

| Figure 28-2Switching Flows Between JTAG and SWD                            |     |

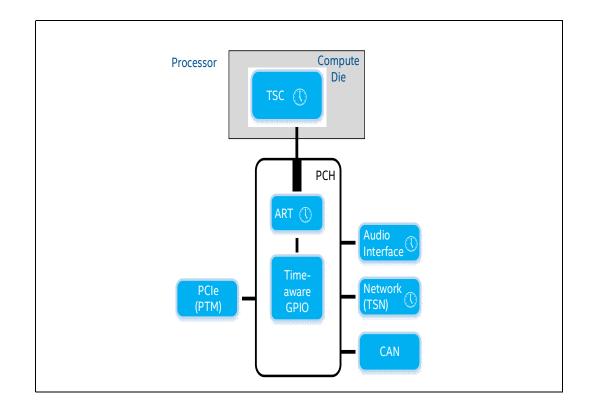

| Figure 29-1Intel® TCC Features within System and TSN between Systems       |     |

| Figure 29-2Platform Time Synchronization                                   |     |

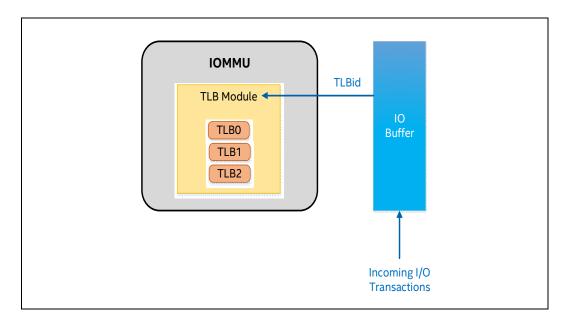

| Figure 29-3IOTLB Usage                                                     |     |

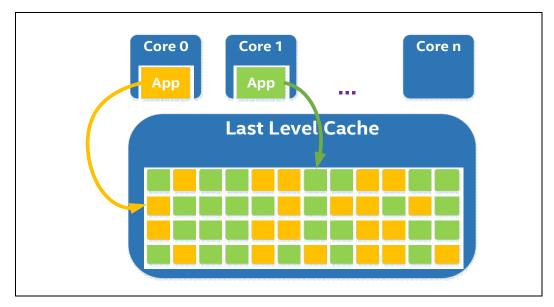

| Figure 29-4LLC without Cache QoS                                           |     |

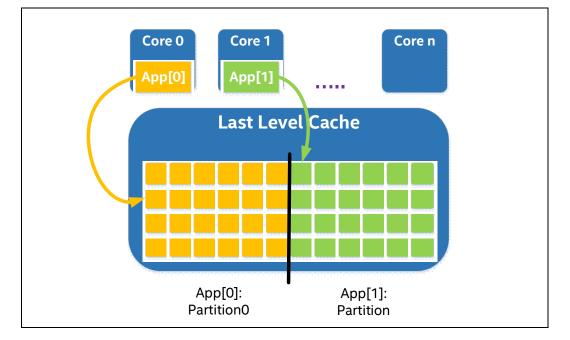

| Figure 29-5LLC with Cache QoS                                              |     |

| Figure 32-1Package Mechanical drawing - Part 1 of 2                        |     |

| Figure 32-2Package Mechanical drawing - Part 2 of 2                        |     |

| Figure 32-3Package Mechanical Drawing                                      |     |

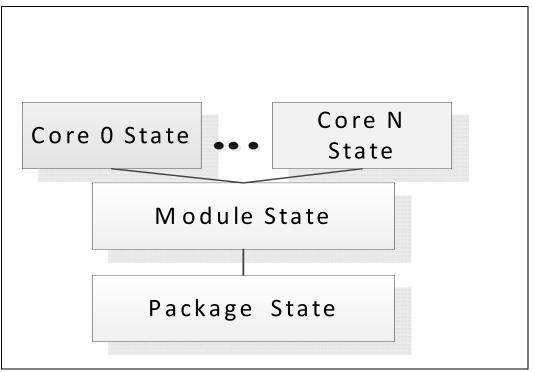

| Figure 34-1Processor Core, Module, and Compute Die Machine Check Registers |     |

#### **List of Tables**

| Table 1-1Processor Features                                                            | 19 |

|----------------------------------------------------------------------------------------|----|

| Table 1-2Processor SKU MAP (High Level)                                                | 26 |

| Table 3-1System States                                                                 | 41 |

| Table 3-2Integrated Memory Controller (IMC) States                                     | 41 |

| Table 3-3G, S, and C Interface State Combinations                                      | 41 |

| Table 3-4State Transition Rules for the PCH                                            |    |

| Table 3-5System Power Plane                                                            | 42 |

| Table 3-6Core C-States                                                                 | 45 |

| Table 3-7Module C-States                                                               | 46 |

| Table 3-8Package C-States                                                              | 47 |

| Table 3-9Intel Atom® x6000E Series processors, Intel® Pentium® and Celeron® N and J Se |    |

| processors S0ix Power Sub-States                                                       | 49 |

| Table 3-10Signal Descriptions                                                          | 49 |

| Table 3-11Platform Voltage Rails                                                       | 52 |

| Table 3-12Additional Voltage Rail Signals                                              | 53 |

| Table 3-13Processor VccIN Active and Idle Mode DC Voltage and Current Specifications   | 55 |

| Table 3-14Processor VCC_1P8A Supply DC Voltage and Current Specifications              | 57 |

| Table 3-15VccIN_AUX Supply DC Voltage and Current Specifications                   | . 57 |

|------------------------------------------------------------------------------------|------|

| Table 3-16Memory Controller (VDDQ) Supply DC Voltage and Current Specifications    | . 59 |

| Table 3-17VCCIO Supply DC Voltage and Current Specifications                       | . 59 |

| Table 3-18Additional Rails Estimated Icc3                                          | . 59 |

| Table 3-19PSE D0ix states                                                          |      |

| Table 3-20Causes of SMI and SCI                                                    | . 64 |

| Table 3-21Sleep Types                                                              | . 67 |

| Table 3-22Causes of Wake Events                                                    | . 67 |

| Table 3-23 Transitions Due to Power Failure                                        | . 69 |

| Table 3-24Transitions Due to Power Button                                          |      |

| Table 3-25Causes of Host and Global Resets                                         | . 73 |

| Table 4-1Processor Specifications                                                  |      |

| Table 4-2Thermal Trip Points and Response (Typical)                                | . 88 |

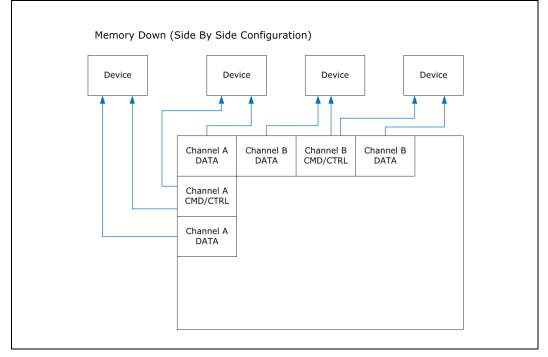

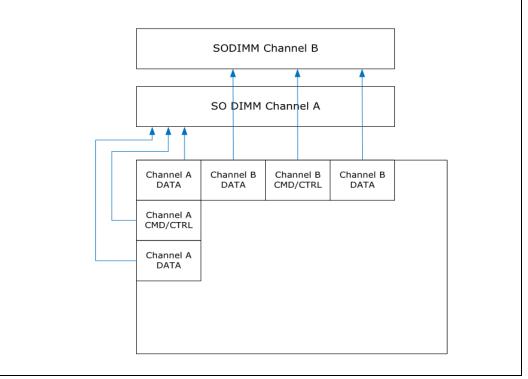

| Table 5-1DDR Support Matrix Table                                                  |      |

| Table 5-2LPDDR4/4x Sub-Channels Population Rules                                   | . 91 |

| Table 5-3DDR4 Channel Population Rules                                             | . 91 |

| Table 5-4Supported SA Speed Enhanced Speed steps (SA-GV) and Gear Mode Frequencies | . 91 |

| Table 5-5Supported DDR4 SODIMM Module Configurations                               | . 92 |

| Table 5-6Supported DDR4 DRAMs (Memory Down) Configurations                         |      |

| Table 5-7Supported LPDDR4/4x x32 DRAMs Configurations                              |      |

| Table 5-8System Memory Interface Signals Terminology                               | . 93 |

| Table 5-9Firmware/Software Initiated Memory Access                                 |      |

| Table 6-1SMM Regions                                                               | 119  |

| Table 6-2Processor Graphics Frame Buffer Accesses                                  | 120  |

| Table 6-3Processor Graphics VGA I/O Mapping                                        | 121  |

| Table 6-4MDA IO Transaction Mapping                                                | 121  |

| Table 6-5MDA Resources                                                             |      |

| Table 6-6Fixed I/O Ranges Decoded by PCH                                           |      |

| Table 6-7Variable I/O Decode Ranges                                                | 126  |

| Table 6-8PCH Memory Decode Ranges (Compute Die Perspective)                        | 129  |

| Table 6-9Addressing Swapping                                                       | 131  |

| Table 7-1Hardware Accelerated Video Decode and Encode                              |      |

| Table 8-1Display Features                                                          |      |

| Table 8-2Ports Availability                                                        | 137  |

| Table 8-3Digital Display Signals                                                   | 139  |

| Table 8-4Pin Mapping for PCH Die                                                   | 140  |

| Table 8-5Panel Control Signals                                                     |      |

| Table 8-6Embedded DisplayPort Signals                                              | 147  |

| Table 8-7MIPI DSI Signals                                                          |      |

| Table 8-8Display Interface Signals                                                 |      |

| Table 10-1Legacy Audio Signals         Table 10-1Legacy Audio Signals              |      |

| Table 11-1USB Bandwidth Information                                                |      |

| Table 11-2Processor USB Specification                                              |      |

| Table 11-3Signal Description                                                       | 162  |

| Table 14-1I2C* Multi-Byte Read                                                     | 184  |

| Table 14-2Enable for SMB_ALERT_N                                                   |      |

| Table 14-3Enables for SMBus Target Write and SMBus Host Events                     |      |

| Table 14-4Enables for the Host Notify Command                                      |      |

| Table 14-5Target Write Registers                                                   |      |

| Table 14-6Command Types                                                            |      |

| Table 14-7Target Read Cycle Format         Cycle Format                            | 189  |

| Table 14-8Data Values for Target Read Registers                                    | 190  |

| Table 14-9Host Notify Format                                                       | 192  |

| Table 15-1TSN IEEE Standards                                                       |      |

| Table 15-2SGMII GbE LAN Signals         Signals                                    | 200  |

| Table 15-3RGMII Signals                                                                                              |            |

|----------------------------------------------------------------------------------------------------------------------|------------|

| Table 15-4MDIO Signals                                                                                               | 201        |