# Streaming Fabric Interface (SFI)

**Specification**

**July 2022**

**Revision 1.0**

Reference Number: 644200

Intel Corporation and its subsidiaries (collectively, "Intel") would like to receive input, comments, suggestions, and other feedback (collectively, "Feedback") on this specification. To be considered for incorporation into the specification, Feedback must be submitted by e-mail to: fabricspecification@intel.com. To the extent that You provide Intel with Feedback, You grant to Intel a worldwide, non exclusive, perpetual, irrevocable, royalty-free, fully paid, transferable license, with the right to sub-license, under Your Intellectual Property Rights, to make, use, sell, offer for sale, import, disclose, reproduce, make derivative works, distribute, or otherwise exploit Your Feedback without any accounting. As used in this paragraph, "Intellectual Property Rights" means, all worldwide copyrights, patents, trade secrets, and any other intellectual or industrial property rights, but excluding any trademarks or similar rights. By submitting Feedback, you represent that you are authorized to submit Feedback on behalf of your employer, if any, and that the Feedback is not confidential .Intel does not control or audit third-party data. You should review this content, consult other sources, and confirm whether referenced data are accurate.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2022, Intel Corporation. All Rights Reserved.

# **Contents**

| L   | Intro           | duction                                                                    | 5    |

|-----|-----------------|----------------------------------------------------------------------------|------|

| 2   | Over            | view                                                                       | 7    |

| 3   | SFT T           | nterface                                                                   | a    |

|     |                 |                                                                            |      |

| 1   |                 | Physical Channel Description                                               |      |

| 5   | Conn            | ect and Disconnect                                                         | . 30 |

| 5   | Mode            | Configuration                                                              | . 36 |

| Fia | ures            |                                                                            |      |

| ııg | uies            |                                                                            |      |

|     | 2-1             | Example Topology and Interface Instantiations                              | 7    |

|     | 3-1             | SFI Physical Channels Showing the HDR and DATA Channels                    |      |

|     | 4-1             | Format for hdr_info_byte                                                   | . 13 |

|     | 4-2             | Example of Header Transfers                                                |      |

|     | 4-3             | Example 1: Two 64-bit Memory Write Headers in one Clock Cycle              |      |

|     | 4-4             | Example 2: Two 32-bit Memory Read Headers in One Clock Cycle               |      |

|     | 4-5             | Example 3: Header Transfer when Header Size Exceeds 6 DWORDs               |      |

|     | 4-6             | Vendor Defined Prefix Used to Send BCM Field                               |      |

|     | 4-7             | Format for data_info_byte                                                  |      |

|     | 4-8             | Example Data Transfer                                                      |      |

|     | 4-9             | Example of Data Interleaving                                               |      |

|     | 4-10            | Example Signal Transitions on HDR Channel for Clock Gating Entry and Exit  |      |

|     | 4-11            | Example Flow for Shared Credit Allocation and De-Allocation                |      |

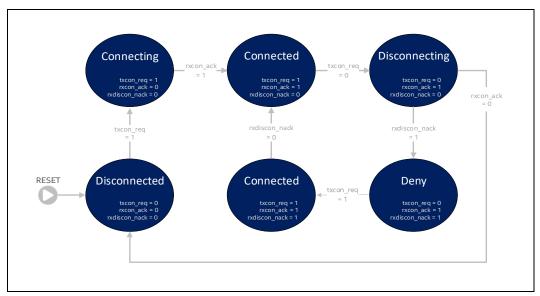

|     | 5-1             | Initialization State Machine                                               |      |

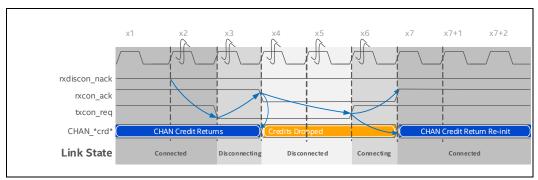

|     | 5-2<br>5-3      | Reset to Connected Timing Diagram  Connect to Disconnect to Connected Flow |      |

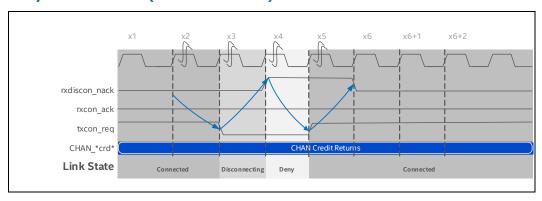

|     | 5-4             | Deny for Disconnect (Disconnect NAck)                                      |      |

|     | J- <del>4</del> | Delly for Disconnect (Disconnect NACK)                                     | . ၁၁ |

| Tal | oles            |                                                                            |      |

|     | 1-1             | Terms and Definitions                                                      | 5    |

|     | 1-2             | Reference Documents                                                        |      |

|     | 4-1             | Signals of the Global Layer                                                |      |

|     | 4-2             | Fields of the HDR Layer                                                    |      |

|     | 4-3             | Fields of DATA Layer                                                       |      |

|     | 4-4             | Shared Pool to SFI VC and FC Mapping                                       |      |

|     | 5-1             | Initialization State Actions                                               |      |

|     | 5-2             | Reset Time Marker Description                                              | . 33 |

|     | 6-1             | Parameters Supported                                                       |      |

|     | 6-2             | Example Parameter Assignments for PCIe* 6.0                                | . 37 |

# intel

# **Revision History**

| Revision<br>Number | Description                                                                                                                                                                                                                                                            | Date        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.0                | <ul> <li>Examples and clarifications on packet formats, data interleaving and shared credits</li> <li>Addition of data parity, viral and fatal signals</li> <li>Updates and additions to Parameters</li> </ul>                                                         | July 2022   |

| 0.9                | <ul> <li>Update data_ecrc to data_trailer and allow the different PCIe* trailer sizes</li> <li>Add data_suffix to support future PCIe* placeholders of suffix</li> <li>End Bad (EDB) support</li> <li>Implementation notes and clarifications on parameters</li> </ul> | August 2021 |

| 0.7                | Initial Release                                                                                                                                                                                                                                                        | March 2020  |

Reference Number: 644200, Revision: 1.0

# 1 Introduction

# 1.1 Terminology

#### Table 1-1. Terms and Definitions

| Title            | Definition                                                                                   |

|------------------|----------------------------------------------------------------------------------------------|

| Ack              | Acknowledge                                                                                  |

| Agent            | Agent refers to the System on Chip (SoC) IP that connects to the fabric                      |

| ECRC             | End-to-End Cyclic Redundancy Check. Defined in the PCI Express* (PCIe*) Base Specification   |

| endpoint         | As defined in the PCI Express* (PCIe*) Base Specification                                    |

| FC               | Flow Control                                                                                 |

| FC ID            | Flow Control Identifier                                                                      |

| HDR              | Header                                                                                       |

| packet<br>header | Protocol packet that is sent on the HDR channel. Used interchangeably with "protocol header" |

| IDE              | Integrity and Data Encryption                                                                |

| LSB              | Least Significant Bit                                                                        |

| MAC              | Message Authentication Code                                                                  |

| MSB              | Most Significant Bit                                                                         |

| NAck             | Negatively Acknowledge                                                                       |

| NP               | Non-Posted                                                                                   |

| PCIe*            | Peripheral Component Interconnect Express*                                                   |

| REQ              | Request                                                                                      |

| Root<br>Complex  | As defined in the PCI Express* (PCIe*) Base Specification                                    |

| Root Port        | As defined in the PCI Express* (PCIe*) Base Specification                                    |

| RSP              | Response                                                                                     |

| RTL              | Register-Transfer Level. A design abstraction which models synchronous digital circuits      |

| RX               | Receiver                                                                                     |

| SFI              | Streaming Fabric Interface                                                                   |

| TLP              | Transaction Layer Packet. As defined in the PCI Express (PCIe*) Base Specification           |

| TX               | Transmitter                                                                                  |

| VC               | Virtual Channel                                                                              |

| VC ID            | Virtual Channel Identifier                                                                   |

| VN               | Virtual Network                                                                              |

Reference Number: 644200, Revision: 1.0

# 1.2 Reference Documents

#### **Table 1-2.** Reference Documents

| Document                                | <b>Document Location</b> |  |

|-----------------------------------------|--------------------------|--|

| PCI Express* (PCIe*) Base Specification | https://pcisig.com       |  |

# 2 Overview

This specification describes the Streaming Fabric Interface (SFI) specification, which has been developed to map Load and Store protocols (such as PCIe\*) between an agent and a fabric. The primary motivation is to provide a scalable streaming interface that can sustain the high bandwidth requirements of Load and Store protocols, such as PCIe\*. The goal is to enable ease of implementation on both the transmit and receive side when transmitting such high data rates. Certain rules, when enforced, greatly simplify storage overhead in the context of read or write ports on the RX.

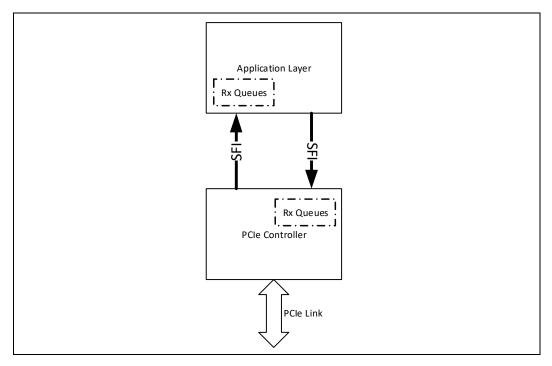

The SFI is applicable both in the context of a Host CPU (root complex) or in the context of a device endpoint. In both cases, the SFI serves to carry protocol layer (transaction layer) specific information between different processing entities. As an example on the device side, the SFI can be used to interface between the PCIe\* controller and the application layer. Similarly, on the host side, the SFI can be used to interface between the PCIe\* root port and the CPU fabric. The SFI can be parametrized to be wide enough and carry multiple packets in a single transfer. Data transfer is unidirectional, so the expectation is to have a pair of SFI instances between communicating blocks. Most of the description in this specification only references a TX and RX pair.

Different configurations can be enabled using the SFI as the intermediate interface. The SFI makes no assumptions around protocol and application specific responsibilities between the TX and the RX. It simply provides a mechanism and rules for high bandwidth packet transfer. Figure 2-1 shows an example interface instantiation in a PCIe\* device.

Figure 2-1. Example Topology and Interface Instantiations

The SFI does not contain any new protocol definition. In fact, SFI semantics can be used to support different protocols as long as they can be mapped to the Flow Control (FC) and Virtual Channel (VC) semantics that SFI provides. For PCIe\* protocol, the Header (HDR) formats follow the description outlined in the *PCI Express\* (PCIe\*) Base Specification 6.0* for FLIT mode headers.

The SFI supports advertisement of zero or more shared credit pools for the RX queues. The specification describes two different ways in which shared credits can be advertised or implemented.

# 3 SFI Interface

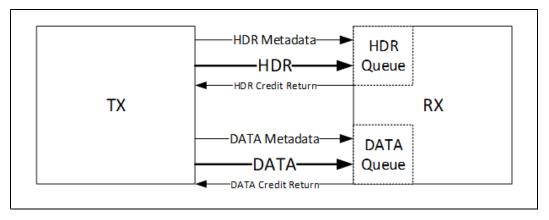

### 3.1 SFI Physical Channels

For each instance, besides certain global signals, the SFI defines two physical channels from TX to RX. The HDR and DATA channels carry packet transfers from TX to RX. Credit returns for each of the physical channels are from RX to TX and are considered part of that physical channel description. Figure 3-1 shows the different physical channels of the SFI.

Global Layer carries signals that apply across all physical channels. It carries the signals that are also used for initialization and shutdown of the interface. See Section 5 for initialization and shutdown flow.

Each of the HDR and DATA channels can carry multiple packets on the same cycle of transfer. Since most Load and Store protocols rely on ordering semantics, SFI assumes implicit ordering when multiple packets are sent on the same cycle. Packets are ordered from the least significant position to the most significant position. For example, if the Transaction Layer Packet (TLP) 0 begins from byte 0 of the header and TLP 1 begins from byte 16 of the header, then the RX must consider TLP 1 ordered behind TLP 0 whenever ordering rules apply. For transfers across different clock cycles, the ordering rules of the relevant protocol are followed (as an example, the SFI carries over all of the PCIe\* ordering rules when used for PCIe\*).

The VC assignment and decoding is implementation-specific but must be consistent between TX and RX to satisfy all the system level and protocol requirements. For example, in cases of link subdivision, it is permitted for the different ports from the controller perspective to map to different VCs on the SFI.

Multiple SFI interface instances could be needed to service a protocol (for example, a request going on one instance and the corresponding response coming back on a different instance).

Depending on the parameters used to configure the interface, each of the physical channels carries metadata to convey information about the position of different packets within a single transfer. This will be covered in more detail in a subsequent section.

Packet headers with data associated with them send the packet header on the HDR channel and the data on the DATA channel. It is assumed that the RX keeps track of the associated data length for each received header and only processing the relevant data size for that header. The data size is sent with the packet header information. As an example in PCIe\*, the length field in the TLP header indicates how many four-byte (DWORD) chunks of data are associated with that header.

Figure 3-1. SFI Physical Channels Showing the HDR and DATA Channels

# 3.2 SFI Protocols Supported

The protocols are not defined as part of the SFI, but are defined in other documents. The present specification uses an example of PCIe\* to illustrate recommended parameters and applications, but other streaming protocols can use similar semantics.

# 4 SFI Physical Channel Description

# 4.1 Global Layer

Global Layer carries signals that apply across all physical channels. It carries the signals that are also used for initialization and shutdown of the interface. See Section 5 for initialization and shutdown flows.

Table 4-1. Signals of the Global Layer

| Signal Class   | Signal Name     | Width   | Direction           | Description                                                                                                                                                                                                                                                                                                                           |

|----------------|-----------------|---------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | txcon_req       | 1 bit   | $TX \rightarrow RX$ | Connection request from TX $(0 \rightarrow 1 \text{ connection request,} 1 \rightarrow 0 \text{ disconnection request)}$                                                                                                                                                                                                              |

| Init           | rxcon_ack       | 1 bit   | $RX \to TX$         | Connection acknowledge from RX $(0 \to 1 \text{ connection acknowledge,} 1 \to 0 \text{ disconnection acknowledge})$                                                                                                                                                                                                                  |

|                | rxdiscon_nack   | 1 bit   | $RX \rightarrow TX$ | Disconnection Negatively Acknowledge (NAck) from RX                                                                                                                                                                                                                                                                                   |

|                | rx_empty        | 1 bit   | $RX \rightarrow TX$ | RX queues are empty for all channels, and all credits have been returned.                                                                                                                                                                                                                                                             |

| RAS            | tx_viral        | 1 bit   | $TX \rightarrow RX$ | Optional signal to indicate viral status from TX to RX. It is a level signal, once asserted it remains asserted until error handling is complete.                                                                                                                                                                                     |

| RAS            | tx_fatal        | 1 bit   | $TX \rightarrow RX$ | Optional signal to indicate fatal status from TX to RX. It is a level signal, once asserted it remains asserted until error handling is complete.                                                                                                                                                                                     |

| Vendor Defined | tx_vendor_field | VT bits | $TX \rightarrow RX$ | Optional signal to send static or global vendor-<br>defined information from TX to RX.<br>For PCIe* protocol, it is permitted to carry<br>additional global information for power or<br>performance optimizations (for example, Link<br>speed, width), but the SFI interface<br>interoperability must not depend on these<br>signals. |

| render berried | rx_vendor_field | VR bits | $RX \rightarrow TX$ | Optional signal to send static or global vendor-<br>defined information from RX to TX.<br>For PCIe* protocol, it is permitted to carry<br>additional global information for power or<br>performance optimizations (for example, Link<br>speed, width), but the SFI interface<br>interoperability must not depend on these<br>signals. |

# 4.2 HDR Layer

The HDR Layer carries requests from TX to RX. The address and the protocol level command information are encapsulated in the **header** field.

Table 4-2. Fields of the HDR Layer

| Signal Class | Signal Name       | Width      | Direction           | Description                                                                                                                                                                                                                                                                           |

|--------------|-------------------|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | hdr_valid         | M bits     | $TX \rightarrow RX$ | Indicates the start of a new packet on the corresponding header byte. It is required to have a fixed association between the individual bits of hdr_valid and the bytes of header.                                                                                                    |

| VALID        | hdr_block         | 1 bit      | $RX \to TX$         | This is an optional signal. It is an indication from RX to TX for a temporary stall to header transfers.  See Section 4.4.1 for rules related to this signal.  Applications of temporary stalling include dynamic clock gating and/or temporary stalls due to clock crossing FIFOs.   |

|              | hdr_early_valid   | 1 bit      | TX → RX             | This is an optional signal. It is an early valid indication from TX to RX indicating that TX has packets to send on the HDR channel. See Section 4.4.1 for rules related to this signal.  In conjunction with the hdr block signal, it is used to enable dynamic clock gating for RX. |

| HDR          | header            | H bytes    | TX → RX             | Header information. It can contain multiple packets transferred in the same cycle. FC and VC information is additionally embedded in hdr_info_bytes. H must be a multiple of M, and hdr_valid[i] corresponds to header byte (i×H/M).                                                  |

|              | hdr_info_bytes    | 2×M bytes  | $TX \rightarrow RX$ | Indicates packet headersize, flow control, VC, and parity information. Information is valid whenever the corresponding hdr_valid is asserted.                                                                                                                                         |

|              | hdr_crd_rtn_valid | 1 bit      | $RX \rightarrow TX$ | Credit return valid.                                                                                                                                                                                                                                                                  |

|              | hdr_crd_rtn_ded   | 1 bit      | $RX \to TX$         | Indicates the credit returns are to the dedicated pool of credits. If this is 0 on a valid credit return, the credits should be returned to the corresponding shared pool of credits. It must be set to 0 if hdr_ord_rtn_vc_id is 5'd30 or 5'd31. Refer to Section 4.5.1 for details. |

|              | hdr_crd_rtn_fc_id | 2 bits     | $RX \rightarrow TX$ | Identifies the flow control class for this credit return.                                                                                                                                                                                                                             |

| CREDIT       | hdr_crd_rtn_vc_id | 5 bits     | $RX \rightarrow TX$ | Identifies the VC for this credit return.                                                                                                                                                                                                                                             |

|              | hdr_crd_rtn_value | NHCRD bits | $RX \rightarrow TX$ | Indicates how many credits are returned in this cycle                                                                                                                                                                                                                                 |

|              | hdr_crd_rtn_block | 1 bit      | TX → RX             | This is an optional signal. It is an indication from TX to RX for a temporary stall to credit returns.  See Section 4.4.1 for rules related to this signal.  Applications of temporary stalls include dynamic clock gating and/or stalls due to clock crossing FIFOs.                 |

The width of **header** field "H" is a predetermined parameter based on the peak sustained bandwidth requirements. Rules for the HDR channel are outlined as follows:

- 1. A packet header must begin and end on the same cycle of transfer. Multiple packet headers can be sent on the same cycle.

- 2. The first packet header on a valid **header** transfer must start on byte 0 of the header field. Subsequent packets, if available for transfer in the same clock cycle, must begin at the next available header start location (i.e. if the prior packet header was at byte location "i×H/M", and had less than or equal to H/M bytes, the next packet header must start at "(i+1)×H/M" if being sent on the same clock cycle. If prior packet header took more than H/M bytes, then the next packet header must begin at the next available multiple of H/M byte, if being sent on the same clock cycle).

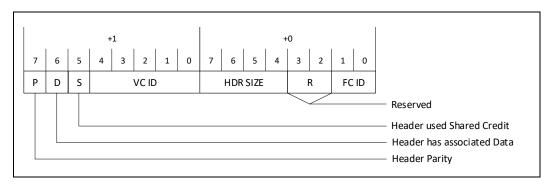

- 3. When hdr\_valid corresponding to a header byte is asserted, the hdr\_info\_bytes field describes key attributes that can be used by the RX to decode the packet header. These are shown in Figure 4-1 (least significant byte is shown to the right).

- a. P is the Parity bit. Support for parity bit is optional. When supported, it is the XOR of all bits of a packet header and the non-parity bits of the corresponding hdr info bytes. Parity errors on the HDR channel are fatal to interface operation and must be reported as fatal errors. When not supported, it must be reserved; TX must drive 0, and RX must not check parity.

- b. D indicates the packet header has corresponding data associated with it.

- c. S indicates that the corresponding packet header used as a shared credit. If this packet header had data associated with it, then the data must also consume credits from the shared pool.

- d. Virtual Channel Identifier (VC ID) is the virtual channel identifier for the packet header it can be in the range of 0 to 29 (VC ID 30 and 31 are reserved for advertising shared credits and not for use as VCs).

- e. Flow Control Identifier (FC ID) is the flow control identifier for the packet header. For PCIe\*, three FC IDs are possible 2′b00 for Posted, 2′b01 for Non-Posted, and 2′b10 for Completions.

- f. All Reserved bits must be driven to 0 by TX and ignored by RX. Switches and fabric routers must propagate the reserved bits as-is without any modifications.

- 4. The HDR SIZE is specified in HGRAN granularity (in other words, the packet header formats must be defined in the granularity determined by the design parameter HGRAN. Typically this parameter is set to four bytes in the context of PCIe\* protocol, and hence, HDR SIZE would indicate the packet header size in the number of DWORDs). The hdr\_info\_bytes bytes are not included in the HDR SIZE computation.

Figure 4-1. Format for hdr\_info\_byte

- 5. There must be a predetermined number of maximum packet headers that can be transmitted in one cycle, which are determined by the headerfield width (H) and the maximum packet header size. The header field width (H) must be chosen so as to allow the common case usage to sustain maximum throughput. Assume the common case application packet header size is 16 bytes (maps to four DWORD headers in PCIe\*), and that we want to sustain two packet headers per cycle. Hence, H = 2×(16) = 32 bytes. M must be 2 with hdr\_valid[0] corresponding to header byte 0, and hdr\_valid[1] corresponding to byte 16. If occasionally the packet header size is more than 16 bytes (as an example, if PCIe\* TLP Prefix was used), then only one packet header can be transferred in that cycle, and hdr\_valid[1] must not assert. For interoperability reasons, all TXs must support a configuration mode where they transfer only one packet header per cycle.

- 6. There must be a predetermined number of maximum FC and VC ID combinations allowed at a given transfer cycle. Both TX and RX must be aware of this at design compile time. A maximum of two implies that all the packet headers transferred on a given cycle can belong to two different FC within the same VC or the same FC for two different VC or all packet headers belong to the same FC and VC. This rule helps minimize the write ports in the storage of RX when buffers are shared between FC and VC. For interoperability reasons, all TXs must support a configuration mode where they transfer only one FC and VC combination per cycle.

- 7. If a packet header has data associated with it, the packet header is sent on the HDR channel and the associated data is sent on the DATA channel.

- a. TX must check for available credits for both header and DATA before scheduling either of the header or data transfers.

- 8. The credit granularity for packet headers is the maximum supported packet header size as well as any potential data\_trailers or data\_suffix. For example, if the maximum packet header size supported is 20 bytes, then 1 credit corresponds to 20 bytes worth of storage at the RX. Even if only a 16-byte packet header is sent, 1 credit is consumed corresponding to the full 20 bytes. For PCIe\*, data\_trailer bit is asserted to indicate the presence of PCIe\* defined TLP trailer DW following the data payload. A couple of examples of this are mentioned next. For PCIe\*, data\_suffix bit is asserted to indicate the presence of TLP suffix following the data payload or trailer DWs.The space for trailer and suffix is accounted for as part of packet header credits.

- a. When End-to-End Cyclic Redundancy Check (ECRC) is supported, even though the ECRC bytes are sent on the DATA channel, the storage space for ECRC is included as part of the packet header credit consumed (similar to TLP digest in PCIe\* protocol).

- b. If Integrity and Data Encryption (IDE) TLPs need to be sent across the interface, IDE prefixes are sent on the HDR channel, and the Message Authentication Code (MAC) bytes are sent on the DATA channel. The storage space for MAC and prefixes are included as part of the packet header credit (similar to PCIe\* protocol rules).

#### 4.2.1 Example Header Transfer

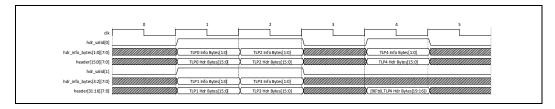

The waveform shown in Figure 4-2 demonstrates packet header transfers. Clock cycles 1 and 2 transfer two packet headers of size 4 (HDR\_SIZE = 4) each, while clock cycle 4 transfers one packet header of size 5. In this example, hdr\_valid[0] is always associated with header byte [0] and hdr\_valid[1] is always associated with HDR byte[16].

Figure 4-2. Example of Header Transfers

#### 4.2.2 PCIe\* and CXL.io\* Packet Format Examples

As mentioned previously, PCIe\* Flit Mode packet formats and byte assignments are followed for PCIe\* protocol. Similarly, CXL.io\* 256B Flit Mode packet formats and byte assignments are followed for CXL.io\* protocol. This section presents examples and any additional rules associated with these formats when transporting over SFI. See the PCI Express\* (PCIe\*) Base Specification and CXL\* Base Specification for the definitions of the individual fields within the headers.

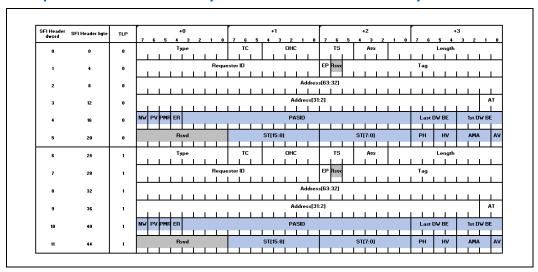

The SFI parameter setting example in Table 6-2 is optimized for memory transactions using 6 DWORD PCIe\* protocol headers (4 DWORDs base, 1 DW OHC-A, 1 DW of OHC-B). Figure 4-3 shows an example of header transfers using these parameter settings. In this example, the SFI transmitter can fit two 64-bit memory write PCIe\* protocol headers with no prefixes and with OHC-A1 and OHC-B into a single SFI header. Because the protocol headers are the optimal size for this configuration, both TLP0 and TLP1 naturally align. hdr valid[1:0] = 11b for Example 1.

Figure 4-3. Example 1: Two 64-bit Memory Write Headers in one Clock Cycle

However, it is possible that not every protocol header will be sized the same as the ideal utilization scenario in the context of the chosen parameter settings. In the example in Figure 4-4, the SFI transmitter is sending two 32-bit memory read PCIe\* protocol headers with no prefixes and no OHC. Because the size of each protocol header is smaller than 6 DWORDs, the SFI transmitter must ensure that any subsequent protocol headers be placed at the interface on increments of 6 DWORDs. Any leftover SFI header space from the previous protocol headers ending location must be treated as reserved (driven to 0 by the transmitter and ignored by the receiver). hdr valid[1:0] = 11b for Example 2.

Figure 4-4. Example 2: Two 32-bit Memory Read Headers in One Clock Cycle

On the other hand, if a protocol header size exceeds 6 DWORDs for this set of parameters, the SFI transmitter must ensure that it does not insert another protocol header in the same clock cycle. In Figure 4-5, the transmitter is sending a 64-bit memory write with a local vendor defined prefix and OHC-A1 and OHC-B for a total size of 7 DWORDs. Since this exceeds the 6 DWORD boundary, the SFI transmitter must only send one protocol header at that clock cycle. hdr\_valid[1:0] = 01b for Example 3.

Figure 4-5. Example 3: Header Transfer when Header Size Exceeds 6 DWORDs

#### 4.2.3 Additional Considerations

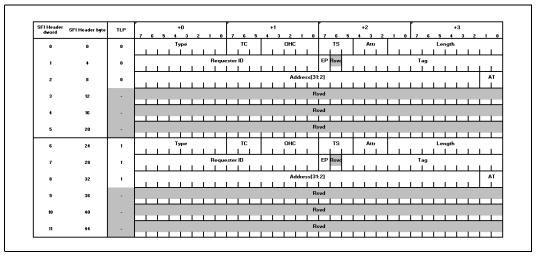

• The Byte Count Modified field does not have an allocated space in the PCIe\* Flit Mode header formats. If this field is required, it must be sent over SFI using a Vendor defined local TLP prefix as shown in Figure 4-6. If this field is required, the parameter BCM\_EN must be set to 1b, and all completion headers must carry this prefix. Additionally, this prefix must be the first DWORD for completion headers (i.e., other vendor defined prefixes and base header should come after this prefix).

Figure 4-6. Vendor Defined Prefix Used to Send BCM Field

The "TLP Uses Dedicated Credits" field in Flit Mode local TLP Prefix from PCI Express\* (PCIe\*) Base Specification is not relevant for SFI, since shared vs dedicated credits is indicated via the "S" bit in hdr\_info\_bytes. Receivers must ignore this field if Flit Mode local TLP Prefix is present in the header. If FLIT\_MODE\_PREFIX\_EN is 0, Transmitters must never send Flit Mode TLP prefix over SFI.

Note:

Currently, Flit Mode TLP prefix is only used to indicate dedicated credits over PCIe\*/

CXL.io\* links and it is strongly recommended to set FLIT\_MODE\_PREFIX\_EN=0. If

PCIe\* or CXL.io\* add additional fields to Flit Mode TLP prefix, then it is permitted to set

FLIT\_MODE\_PREFIX\_EN to 1, but receivers must still ignore the "TLP Uses Dedicated

Credits" field in that prefix and use the "S" bit in hdr\_info\_bytes to determine if the

header used shared vs dedicated credits.

• Even when the PCIe\* or CXL.io\* Link itself trains to non-Flit mode configuration, the header formats on SFI follow the Flit Mode formats. It is the responsibility of the Transaction Layer to perform the necessary conversions before transmitting TLPs over the PCIe\* or CXL.io\* Link. See the PCI Express\* (PCIe\*) Base Specification for information related to how the field mappings change between Flit mode and non-Flit mode formats for PCIe\*.

## 4.3 Data Layer

The DATA physical channel carries data for all requests that have data associated with it. The timing requirement between the HDR channel and the associated data coming on the DATA channel is determined by the parameters described in Section 6. It is required for TX to check both HDR channel and DATA channel credits before scheduling either the HDR or DATA on their respective channels.

Table 4-3. Fields of DATA Layer (Sheet 1 of 3)

| Signal<br>Class | Signal Name      | Width | Direction           | Description                                                                                                                                                                                                                                                                              |

|-----------------|------------------|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | data_valid       | 1 bit | $TX \rightarrow RX$ | Indicates that data corresponding to at least one packet is sent on the DATA signal class fields when asserted. If data associated with multiple packets are sent, they are disambiguated by the using the fields in the class                                                           |

| VALID           | data_block       | 1 bit | $RX \rightarrow TX$ | This is an optional signal. It is an indication from RX to TX for a temporary stall to data transfers.  See Section 4.4.1 for rules related to this signal.  Applications include dynamic clock gating and/or temporary stalls due to clock crossing FIFOs in RX.                        |

|                 | data_early_valid | 1 bit | $TX \rightarrow RX$ | This is an optional signal. It is an early valid indication from TX to RX indicating that TX has packets to send on the DATA channel.  See Section 4.4.1 for rules related to this signal.  In conjunction with the data_block signal, it is used to enable dynamic clock gating for RX. |

Table 4-3. Fields of DATA Layer (Sheet 2 of 3)

| Signal<br>Class | Signal Name     | Width     | Direction           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------|-----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | data            | D bytes   | $TX \rightarrow RX$ | Carries the raw data for associated packets. The raw data must be in 4-byte granularity. When DATA layer is present, D must be greater than or equal to 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | data_parity     | D/8 bits  | TX → RX             | If DATA_PARITY_EN = 1, this signal is used to transfer data parity over the interface. Data parity for data transferred over a given clock cycle. It is computed for even parity of 1 parity bit over every 8B of data.  If data_valid = 1b, data_parity[n] is the XOR of all bits of data bytes [8×(n+1)-1: 8×n]; where "n = 0,1D/8". If 8×(n+1) > D, then data is 0 padded in the MSB for the purpose of parity computation. data_parity is computed regardless of data_start or data_end values.  At least one bit of data_parity must always exist if DATA_PARITY_EN = 1. If D <= 8, only one bit of data_parity is present.  Parity error handling/escalation is implementation/SoC specific. For example, it could be mapped to a fatal error, or RX could poison the protocol packets for the corresponding data which had a parity error. When not supported, it must be reserved; i.e., TX must drive 0, and RX must not check parity. |

|                 | data_start      | DS bits   | $TX \rightarrow RX$ | Indicates the start of a new data packet on the corresponding data byte. It is required to have a fixed association between the individual bits of data_start and the bytes of data. The parameter DS is determined by the maximum number of separate packets that need to be sustained per cycle. D must be a multiple of DS, and data_start[i] corresponds to data byte (i×D/DS).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DATA            | data_info_byte  | DS×8 bits | TX → RX             | For every data_start bit, there is a data_info_byte, which indicates the FC ID and the VC ID of the associated data packet. RX must not assume data_info_byte is valid if the corresponding data_start is not asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | data_end        | D/4 bits  | TX → RX             | Indicates the end of a new data packet on the corresponding data 4-byte chunk. It is required to have a fixed association between the individual bits of data_end and the bytes of data. Thus, data_end[i] corresponds to data bytes [(4×(i+1) - 1):4×i].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | data_poison     | D/4 bits  | TX → RX             | Indicates one or more bytes of the associated data packet is poisoned. RX must treat the entire protocol packet payload corresponding to this data as poisoned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | data_edb        | D/4 bits  | TX → RX             | Indicates the packet associated with this data is bad and must be dumped by the RX. TX must have consumed the corresponding credits (both header and data credits), and hence, RX must return the corresponding credits after dumping the packet. This signal can be used to enable cut-through routing in switches and fabric as long as the final RX can guarantee dumping the packet before the commit point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | data_trailer    | D/4 bits  | $TX \rightarrow RX$ | This is optional, only required if TLP trailers are supported. It should be asserted when the corresponding data bytes carry the TLP trailer DWORDs (for example ECRC or IDE MAC, and so on.). See the PCI Express* (PCIe*) Base Specification for details on TLP trailer definitions and support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | data_suffix     | D/4 bits  | $TX \rightarrow RX$ | This is optional, only required if TLP suffixes are supported. When asserted, it indicates that the corresponding DWORD of data is a TLP suffix. See the <i>PCI Express*</i> ( <i>PCIe*</i> ) Base Specification for details on TLP suffix definitions and support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | data_aux_parity | 1 bit     | TX → RX             | Optional signal. Whenever data_valid is 1b, data_aux_parity is the XOR of all the signals in DATA signal class, with the exception of data and data_parity signals. Parity errors on the data_aux_parity are fatal to interface operation and must be reported as fatal errors. When not supported, it must be reserved; i.e., TX must drive 0, and RX must not check parity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 4-3. Fields of DATA Layer (Sheet 3 of 3)

| Signal<br>Class | Signal Name        | Width      | Direction           | Description                                                                                                                                                                                                                                        |

|-----------------|--------------------|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | data_crd_rtn_valid | 1 bit      | $RX \rightarrow TX$ | Credit return valid.                                                                                                                                                                                                                               |

|                 | data_crd_rtn_ded   | 1 bit      | $RX \rightarrow TX$ | Indicates the credit returns are to the dedicated pool of credits. If this is 0 on a valid credit return, the credits should be returned to the corresponding shared pool of credits. It must be set to 0 if data_crd_rtn_vc_id is 5'd30 or 5'd31. |

|                 | data_crd_rtn_fc_id | 2 bits     | $RX \rightarrow TX$ | Identifies the flow control class for which data credits are being returned. For shared pool credit returns, it indicates the flow control of the transaction deallocated from RX buffers.                                                         |

| CREDIT          | data_crd_rtn_vc_id | 5 bits     | $RX \rightarrow TX$ | Identifies the VC for which data credits are being returned. For shared pool credit returns, it indicates the VC of the transaction deallocated from RX buffers.                                                                                   |

|                 | data_crd_rtn_value | NDCRD bits | RX → TX             | Indicates how many credits are being returned. Each credit corresponds to the chosen data granularity of storage in RX.                                                                                                                            |

|                 | data_crd_rtn_block | 1 bit      | TX → RX             | This is an optional signal. It is an indication from TX to RX for a temporary stall to credit returns.  See Section 4.4.1 for rules related to this signal.  Applications include dynamic clock gating and/or stalls due to clock crossing FIFOs.  |

#### Rules for the DATA channel are outlined as follows:

- 1. The Data is always transferred in 4-byte granularity. The end positions of data are hence determined in 4-byte chunks. Thus, if D = 64 (raw data is 64B), D/4 = 16, with data\_end[0] corresponding to data bytes[3:0], data\_end[1] corresponding to data bytes[7:4], and so on. data\_end is used by RX to determine when a payload for a packet has finished transfer across SFI.

- 2. It is not required to have the same 4-byte granularity for data\_start. An implementation limits the maximum number of starts in a cycle. For example, consider a 64-byte raw data bus (D = 64), and implementations want to limit the maximum number of starts in a cycle to 2. This means that DS = 2, and data\_start[0] corresponds to data byte[0] and data\_start[1] corresponds to data byte[32]. For interoperability reasons, all transmitters must have a configuration modewhere they only send bytes from at the most one data packet per cycle. When DS > 1, it is not required for transmitter to always start the first data packet at data\_start[0] (since the receiver has to deal with data byte shifting to write into its storage buffers anyway, this allows the TX to streamline data relative to its storage buffer organization when applicable). RX must not consume unused data bytes at a given clock edge (with the exception of data\_parity computation).

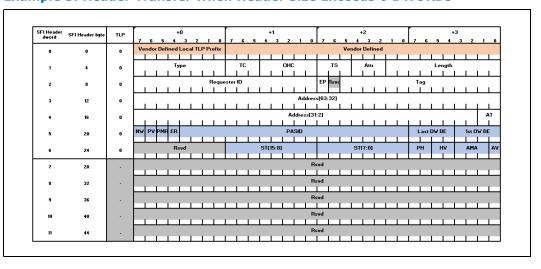

- 3. Every data\_start bit has an associated data\_info\_byte with it that indicates the FC ID and VC ID of the corresponding packet. The format of data\_info\_byte is shown in Figure 4-7. FC ID and VC ID encodings are the same as those on the HDR channel.

Figure 4-7. Format for data\_info\_byte

- 4. Unlike the HDR channel, data chunks from the same packet can be transferred over multiple cycles. For example, the raw data bus could be 64B, and a 128B data packet could be transferred over two clock cycles.

- 5. It is required for TX to maintain the same relative ordering of data packets as the associated headers for a given FC and VC combination.

- 6. RXs can optionally support data interleaving across different FC and VC combinations over different clock cycles. data\_start must assert every time whenever the data stream interleaves different FC or VC; RX will use the data\_info\_byte along with data\_start to assign the data stream to the appropriate VC/FC. This allows for low overhead time division multiplexed data path switching between two TXs that want to send packets to a common RX (with mutually exclusive VCs). This is the only time when multiple data\_starts are permitted before a data\_end. However, interleaving or bubbles in between a data transfer are not allowed at a given clock edge (i.e., it is not permitted to have multiple data\_starts before a data\_end on the same clock cycle for a given FC/VC).

- 7. The data credit granularity must be predetermined at design compile time between the TX and RX. The granularity must be a multiple of 4 bytes (DWORD). For example, if the credit granularity is chosen to be 16 bytes, then even a 4-byte data packet transferred uses one 16-byte worth of credit.

#### 4.3.1 Example Data Transfer

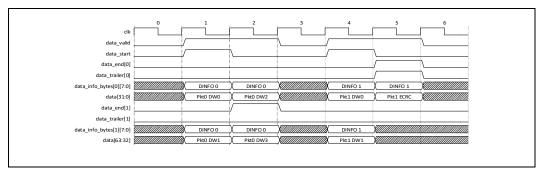

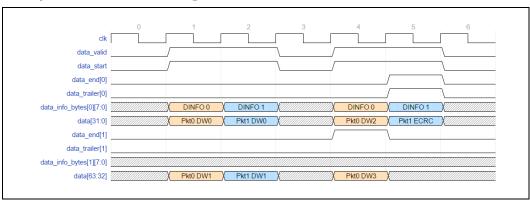

Figure 4-8 shows two examples of data transfer for a 64-bit data bus, and DS = 1. For Pkt0, it has four DWORDs of payload with no ECRC. For Packet 1, it has two DWORDs of payload and one DWORD of ECRC. In this example, TX chooses to drive DINFO along with valid data always.

Figure 4-8. Example Data Transfer

shows an example of data interleaving. The different colors belong to different FC, VC which are interleaved on the same data bus. In this example, TX chooses to only drive DINFO with corresponding data start.

Figure 4-9. Example of Data Interleaving

#### 4.4 Clocks and Resets

It is not required for TX or RX to coordinate reset. The initialization flow defines a separate handshake to ensure TX and RX exchange information about interface reset and flow control before traffic can begin. Power gating optimizations can be implemented by moving to a disconnected state.

SFI is a synchronous interface—both sides of the interface must run on the same clock. RXs of signals are permitted to instantiate clock crossing FIFOs internally, but must do so in a way that the rules of interface operation are not violated. SFI provisions for temporary stalling of packet transfers to enable dynamic clock gating and/or clock crossing related stalls.

### 4.4.1 Block and Early\_valid rules

It is strongly recommended that \*\_block and \*\_early\_valid signals be supported by implementations to ensure wider interoperability. The following rules apply when the early\_valid and block signals are implemented.

Once hdr\_block is asserted, the compile time parameter TBN determines the number of clock cycles after which TX must guarantee a stall (in other words, no more assertion of hdr\_valid).

- 2. Once hdr\_block deasserts, TX is permitted to begin header transfer from the next clock cycle.

- 3. Once data\_block is asserted, the compile-time parameter *TBN* determines the number of clock cycles after which TX must guarantee a stall (in other words, no more assertion of data valid).

- 4. Once data\_block deasserts, TX is permitted to begin data transfer from the next clock cycle.

- 7. Once data\_crd\_rtn\_block is asserted, the compile-time parameter RBN determines the number of clock cycles after which RX must guarantee a stall (in other words, no more assertion of data crd rtn valid).

- 8. Once data\_crd\_rtn\_block deasserts, RX is permitted to begin data credit returns from the next clock cycle.

- 9. TX must assert hdr\_early\_valid at least one cycle before hdr\_valid. TX is permitted to keep hdr\_early\_valid asserted even if it has no immediate packets to transfer, if it wants to keep RX clocks running to achieve the best latency for imminent packet transfers.

- 10. TX must assert hdr\_early\_valid if it has packets to send, even if hdr\_block signal is asserted. If hdr\_block is asserted, TX must keep hdr\_early\_valid asserted until hdr\_block deasserts and TX has transferred the packets. It is possible that hdr\_block asserts and deasserts several times while packets are being transferred (for example, in cases of clock crossing related rate mismatches); TX must follow the rules related to hdr block at all times.

- 11. TX must assert data\_early\_valid at least once cycle before data\_valid. TX is permitted to keep data\_early\_valid asserted even if it has no immediate packets to transfer if it wants to keep RX clocks running to achieve the best latency for imminent packet transfers.

- 12. TX must assert data\_early\_valid if it has packets to send, even if data\_block signal is asserted. If data\_block is asserted, TX must keep data\_early\_valid asserted until data\_block deasserts and TX has transferred the packets. It is possible that data\_block asserts and deasserts several times while packets are being transferred (for example, in cases of clock crossing related rate mismatches); TX must follow the rules related to data block at all times.

### 4.4.2 Dynamic Clock Gating

If dynamic clock gating is desired, implementations must support all of the \*block and \*early\_valid signals.

From the SFI perspective, RX is permitted to transition to a clock gated state if the corresponding interface is in Disconnect state or all of the following conditions are true:

- The interface is in a Connected state, with no pending request from TX to Disconnect that RX has not responded to.

- hdr\_early\_valid and data\_early\_valid are deasserted from TX.

- No packet transfers are in flight (hdr\_valid and data\_valid are deasserted).

RX has returned the minimum header and data credits required for a packet transfer on any of the supported VC and FC. The minimum credits are defined by the underlying protocol. For example, for PCIe\* data credits on posteds, RX should have returned MPS worth data credits on all supported VCs.

RX must take into account any internal requirements for clock gating in addition to the SFI requirements before transitioning to a clock gated state. These internal requirements are implementation-specific and outside the scope of this specification.

Once the requirements are met, RX transitions to a clock gated state *TBN* cycles after asserting the hdr\_block and data\_block signals (if no packet transfers are received during that time, if packet transfers are received during this time, RX must abort the transition to a clock gated state and it is permitted to re-attempt at a later point if all the requirements for entry are met.)

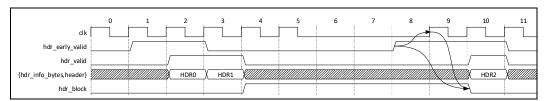

Once in a clock gated state, RX must treat any transition on hdr\_early\_valid, data\_early\_valid, or txcon\_req as an asynchronous trigger to exit the clock gated state. Once it has exited the clock gated state, it must revert to the regular protocol of accepting packets from TX. Figure 4-10 shows an example of entry and exit flow for the HDR channel. Similar handshakes would occur on the DATA channel as well.

Figure 4-10. Example Signal Transitions on HDR Channel for Clock Gating Entry and Exit

From SFI perspective, TX is permitted to transition to a clock gated state if the corresponding interface is in Disconnect state or all of the following conditions are true:

- The interface is in a Connected state, with no pending request from TX to Disconnect that RX has not responded to.

- TX has no packet transfers pending.

- TX has accumulated the minimum header and data credits required for a packet transfer on any supported VC and FC. The underlying protocol defines the minimum credits.

TX must take into account any internal requirements for clock gating in addition to the SFI requirements before transitioning to clock gated state. These internal requirements are implementation specific and outside the scope of this specification.

Once the requirements are met, TX transitions to a clock gated state *RBN* cycles after asserting the hdr\_crd\_rtn\_block and data\_crd\_rtn\_block signals.

Exiting from a clock gated state for a TX is implementation-specific and outside the scope of this specification.

#### Note:

Implementation modules can have multiple SFI interfaces connected to them, where they may be RX or TX for different interfaces. Coarse level clock gating (shutting off global clock for example) for a module, should consider the corresponding RX or TX requirements of all SFI interfaces instantiated on that module.

## 4.5 Channel Flow Control

Each VC and FC must use credits on TX for sending any message and collect credit returns from the RX. The source should consume the full credits required for a message to complete. As mentioned earlier, TX must check for both HDR channel and DATA channel credits before sending either of them to the RX.

Each physical channel has dedicated credit return wires. During operation, the RX returns credits during initialization and whenever it has processed the message (in other words, guaranteed a buffer position for the next transaction).

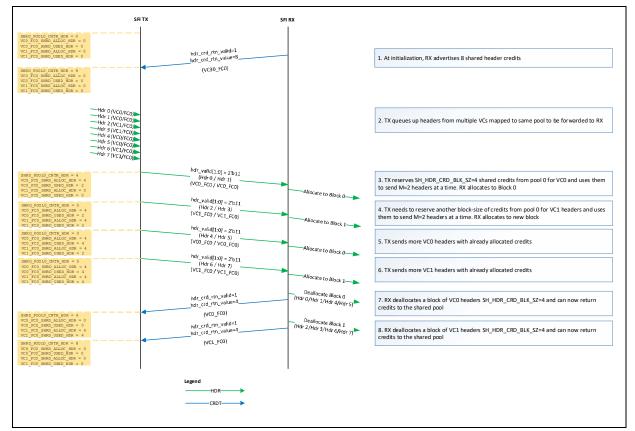

To allow for batch processing at the RX, it is recommended to set the shared credit block size corresponding to the batch processing size at the RX. If credit sharing is enabled, shared credits must be allocated to an FC and VC in block granularity. For example, if  $SH_DATA_CRD_BLK_SZ = 4$ , if acquiring shared credits for a given FC and VC, it must be done in blocks of 4.

RX can advertise infinite credits by setting the \*crd\_rtn\_value = 0 for the corresponding VC and FC credit return. Typically, this is done after initialization if the RX can guarantee a spot to sink traffic from a given VC and FC (for example, if completions were preallocated). Once infinite credits are advertised for a VC and FC, there should be no credit returns for that VC and FC until the next disconnect or connect flow.

#### 4.5.1 Sharing Credits

The SFI allows two schemes for supporting sharing of buffers between different FC and VC IDs. In both schemes, it is required for the RX to advertise the minimum number of dedicated resources needed for a forward progress guarantee. For large packet transfers, this means that the maximum payload size must be considered for dedicated credit advertisement. If  $SHARED\_CRD\_EN=1$ , it implies Type 1 scheme is used. For Type 2, from TX perspective, it looks the same as if shared crediting is disabled since the RX internally manages the shared resources.  $SHARED\_CRD\_EN=0$  is used for both the dedicated and Type 2 shared crediting schemes.

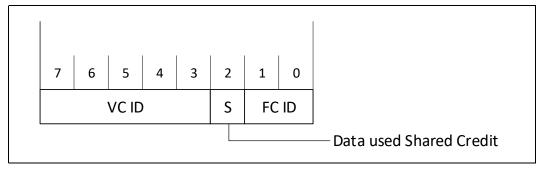

#### **4.5.1.1** Type 1: TX-Managed

In this scheme, the TX is responsible for managing shared buffers in the RX. RX advertises shared credits using SFI VC ID 30 and/or 31. Since up to 4 FC ID encodings are possible for each SFI VC, a total maximum of 8 shared pools can be supported as shown in Table 4-4.

Table 4-4. Shared Pool to SFI VC and FC Mapping

| Shared Pool | SFI FC ID | SFI VC ID |

|-------------|-----------|-----------|

| 0           | 0         |           |

| 1           | 1         | 30        |

| 2           | 2         | 30        |

| 3           | 3         |           |

| 4           | 0         |           |

| 5           | 1         | 31        |

| 6           | 2         | 31        |

| 7           | 3         |           |

#### Note:

RX is permitted to only advertise credits for a subset of these. See Table 6-1 for parameters that determine the mapping.

It is permitted for RX to support fewer shared credit pools. Transactions on a given VC and FC can only use credits from one shared pool. When shared crediting using the Type 1 scheme is enabled, every SFI instance (a TX and RX pair) must define a mapping from each SFI VC and FC sharing credits to a shared pool of credits at design time. It is also permitted for an SFI VC and FC not to be mapped to any shared pool, in which case it is only going to use dedicated credits for that VC and FC.

#### Rules for TX:

- It must maintain a credit counter for dedicated credits for every VC and FC supported (VCi\_FCj\_DED\_CNTR\_HDR, VCi\_FCj\_DED\_CNTR\_DAT for VC "i" and FC "j"). Separate counters are maintained for header and data. The width of these counters must be sufficient to hold all the dedicated credits that can be advertised by the RX for the corresponding SFI VC and FC.

- It must maintain a credit counter for shared credits corresponding to the number of shared pools determined at design time (SHRD\_POOLx\_CNTR\_HDR, SHRD\_POOLx\_CNTR\_DAT for shared pool "x"). Separate counters are maintained for header and data. The width of these counters must be sufficient to hold all the shared credits that can be advertised by the RX for the corresponding shared pool. These counters track the shared pool credits available, and different VC and FC that share these credits have to arbitrate for these credits.

- It must maintain a counter for the number of **consumed** shared credits for every VC and FC sharing credits (*VCi\_FCj\_SHRD\_USED\_HDR*, *VCi\_FCj\_SHRD\_USED\_DAT* for VC "i" and FC "j"). Separate counters are maintained for header and data. The width of these counters must be sufficient to hold the maximum shared credits that can be used by a given SFI VC and FC. These set of counters effectively track the occupancy in the RX shared buffer for the corresponding VC and FC.

- It must maintain a counter for the number of shared credits acquired for every VC and FC sharing credits (VCi\_FCj\_SHRD\_ALLOC\_HDR, VCi\_FCj\_SHRD\_ALLOC\_DAT for VC "i" and FC "j"). Separate counters are maintained for header and data. The width of these counters must be sufficient to hold the maximum shared credits that can be acquired by a given SFI VC and FC. These are only incremented or decremented in block sizes and track how many shared credits have been allocated for a particular VC and FC, but not necessarily used to send traffic yet.

#### Note:

By requiring both the Transmitter and Receiver to explicitly recognize credit blocks, the Receiver's buffer management logic is considerably simplified, while maintaining the efficient use of Receiver resources. Shared resource tracking at the receiver typically requires linked-list structures, and by organizing them in blocks, it gives a much easier way to scale bandwidth to process multiple TLPs per cycle per VC/FC. In addition, the linked-list management logic can be implemented at a block level - reducing the storage requirements of the linked-list (for example, for 1024 entries with a block size of 4, only 256 block pointers are needed from the point of view of linked-list tracking, a 4x reduction).

• It must instantiate a configuration register (VCi\_FCj\_MAX\_HDR, VCi\_FCj\_MAX\_DAT) for every SFI VC and FC mapped to a shared pool of credits. Separate registers are needed for header and data. The value programmed in this register determines the maximum outstanding shared credits acquired by the corresponding SFI VC and FC. Software can use this mechanism to limit the maximum occupancy of the shared pool by a given SFI VC/FC for Quality of Service (QoS) guarantees.

- If an SFI VC and FC are mapped to a shared pool, TX must first check for shared credit availability. Any given transaction will need one header credit and "y" data credits (where the number of data DWORDs associated with the transaction is greater than (y-1)\*DATA\_CRED\_GRAN, but less than y\*DATA\_CRED\_GRAN). "y" will be 0 for transactions that do not have data associated with them. Shared credits are available and used in one of the following two scenarios:

- a. Case 1: Credits acquired, but not used yet.

```

(VCi\_FCj\_SHRD\_ALLOC\_HDR - VCi\_FCj\_SHRD\_USED\_HDR) >= 1, AND (VCi\_FCj\_SHRD\_ALLOC\_DAT - VCi\_FCj\_SHRD\_USED\_DAT) >= y, AND VCi\_FCj\_SHRD\_USED\_HDR + 1 <= VCi\_FCj\_MAX\_HDR, AND VCi\_FCj\_SHRD\_USED\_DAT + y <= VCi\_FCj\_MAX\_DAT.

```

TX can schedule the transaction after incrementing VCi\_FCj\_SHRD\_USED\_DAT by "y" and VCi\_FCj\_SHRD\_USED\_HDR by 1.

b. Case 2: Acquiring credits from Shared Pool "x" for VC "i" and FC "j" In this case, the transmitter is arbitrating for acquiring a block of shared credits. If (VCi\_FCj\_SHRD\_ALLOC\_DAT - VCi\_FCj\_SHRD\_USED\_DAT) is less than "y", TX would need to acquire data shared credits. If (VCi\_FCj\_SHRD\_ALLOC\_HDR - VCi\_FCj\_SHRD\_USED\_HDR) is less than "1" TX would need to acquire header shared credits. Thus, TX might attempt to acquire data shared credits, or header shared credits, or both header and data shared credits.

For acquiring header shared credits:

```

(VCi\_FCj\_SHRD\_ALLOC\_HDR - VCi\_FCj\_SHRD\_USED\_HDR) < 1, AND VCi\_FCj\_SHRD\_USED\_HDR + 1 <= VCi\_FCj\_MAX\_HDR, AND SHRD\_POOLx\_CNTR\_HDR >= SH\_HDR\_CRD\_BLK\_SZ, AND

```

VC "i" and FC "j" can arbitrate for shared credits, once it wins arbitration, TX can schedule transaction after the following actions:

- a. Increment VCi\_FCj\_SHRD\_USED\_HDR by 1

- b. Increment VCi\_FCj\_SHRD\_ALLOC\_HDR by SH\_HDR\_CRD\_BLK\_SZ

- c. Decrement SHRD\_POOLx\_CNTR\_HDR by SH\_HDR\_CRD\_BLK\_SZ

For acquiring data shared credits:

```

(VCi\_FCj\_SHRD\_ALLOC\_DAT - VCi\_FCj\_SHRD\_USED\_DAT) < y, AND VCi\_FCj\_SHRD\_USED\_DAT + y <= VCi\_FCj\_MAX\_DAT, AND SHRD\_POOLx\_CNTR\_DAT >= (ceiling(y/SH\_DATA\_CRD\_BLK\_SZ) \times SH\_DATA\_CRD\_BLK\_SZ).

```

VC "i" and FC "j" can arbitrate for shared credits, once it wins arbitration, TX can schedule transaction after the following actions:

- a. increment VCi FCi SHRD USED DAT by "y"

- b. increment  $VCi\_FCj\_SHRD\_ALLOC\_DAT$  by  $(ceiling(y/SH\_DATA\_CRD\_BLK\_SZ) \times SH\_DATA\_CRD\_BLK\_SZ)$

- c. decrement SHRD\_POOLx\_CNTR\_DAT by (ceiling(y/ SH\_DATA\_CRD\_BLK\_SZ)×SH\_DATA\_CRD\_BLK\_SZ)

Arbitration scheme for shared credits is implementation-specific, but TX must ensure fairness.

- When the TX consumes the shared pool credit for a transaction, it must do so for both header and data credits, and it indicates this on the "S" bit in the metadata for both header and data channels (by setting it to 1b)

- If TX is not able to use shared credits for a sustained time period (this mechanism is implementation-specific), it must use dedicated credits under the following conditions:

VCi\_FCj\_DED\_CNTR\_HDR >= 1, AND VCi\_FCj\_DED\_CNTR\_DAT >= y

TX can schedule the transaction after decrementing VCi\_FCj\_DED\_CNTR\_HDR by 1 and VCi\_FCj\_DED\_CNTR\_DAT by "y".

- When TX consumes a dedicated pool credit, it must do so for both header and data credits, and it indicates this to the RX by setting the "S" bit to 0 in the metadata for both header and data channels.

- The following rules apply for credit returns after a successful connection:

- a. If hdr\_crd\_rtn\_valid = 1 and hdr\_crd\_rtn\_vc\_id = 5'd30 or 5'd31, TX must increment the corresponding SHRD\_POOLx\_CNTR\_HDR ("x" is determined from the mapping given in Table 4-4) by hdr\_crd\_rtn\_value.

- b. else, if hdr\_crd\_rtn\_valid = 1, hdr\_crd\_rtn\_ded = 1, hdr\_crd\_rtn\_vc\_id = i, and hdr\_crd\_rtn\_fc\_id = j, TX must increment the corresponding VCi\_FCj\_DED\_CNTR\_HDR counter by hdr\_crd\_rtn\_value.

- c. else, if hdr\_crd\_rtn\_valid = 1, hdr\_crd\_rtn\_ded = 0, hdr\_crd\_rtn\_vc\_id = i, and hdr\_crd\_rtn\_fc\_id = j, TX must increment the corresponding SHRD\_POOLx\_CNTR\_HDR ("x" is determined based on which shared pool VC "i" and FC "j" are mapped to) by hdr\_crd\_rtn\_value. It must also decrement VCi\_FCj\_SHRD\_USED\_HDR and VCi\_FCj\_SHRD\_ALLOC\_HDR by hdr\_crd\_rtn\_value.

- d. If data crd rtn valid = 1 and data crd rtn vc id = 5'd30 or 5'd31, TX must increment the corresponding SHRD\_POOLx\_CNTR\_DAT ("x" is determined from the mapping given in Table 4-4) by data crd rtn value.

- e. else, if data crd rtn valid = 1, data crd rtn ded = 1, data crd rtn vc id = i, and data crd rtn fc id = j, TX must increment the corresponding VCi\_FCj\_DED\_CNTR\_DAT counter by data crd rtn value.

- f. else, if data crd rtn valid = 1, data crd rtn ded = 0, data crd rtn vc id = i, and data crd rtn fc id = j, TX must increment the corresponding SHRD\_POOLx\_CNTR\_DAT ("x" is determined based on which shared pool VC "i" and FC "j" are mapped to) by data crd rtn value. It must also decrement VCi\_FCj\_SHRD\_USED\_DAT and VCi\_FCj\_SHRD\_ALLOC\_DAT by data\_crd\_rtn\_value.

- After disconnect/reset, TX must assign all the counters (\*CNTR\*, \*ALLOC\*, \*USED\*) to 0 before initiating a connect by asserting txcon\_req.

#### Rules for the RX: