# 9. Using User Flash Memory in MAX II Devices

MII51010-1.8

# Introduction

MAX<sup>®</sup> II devices feature a user flash memory (UFM) block that can be used similar to a serial EEPROM for storing non-volatile information up to 8 Kbits. The UFM provides an ideal storage solution supporting any possible protocol for interfacing (SPI, parallel, and other protocols) through bridging logic designed into the MAX II logic array.

This chapter provides guidelines for UFM applications by describing the features and functionality of the MAX II UFM block and the Quartus<sup>®</sup> II altufm megafunction.

This chapter contains the following sections:

- "UFM Array Description" on page 9–1

- "UFM Functional Description" on page 9–3

- "UFM Operating Modes" on page 9–9

- "Programming and Reading the UFM with JTAG" on page 9–12

- "Software Support for UFM Block" on page 9–13

- "Creating Memory Content File" on page 9–40

- "Simulation Parameters" on page 9–46

# **UFM Array Description**

Each UFM array is organized as two separate sectors with 4,096 bits per sector. Each sector can be erased independently. Table 9–1 shows the dimension of the UFM array.

| Table | 9–1. | UFM Array | Size |

|-------|------|-----------|------|

|-------|------|-----------|------|

| Device  | Total Bits | Sectors                   | Address Bits | Data Width |

|---------|------------|---------------------------|--------------|------------|

| EPM240  | 8,192      | 2 (4,096 bits per sector) | 9            | 16         |

| EPM570  |            |                           |              |            |

| EPM1270 |            |                           |              |            |

| EPM2210 |            |                           |              |            |

## **Memory Organization Map**

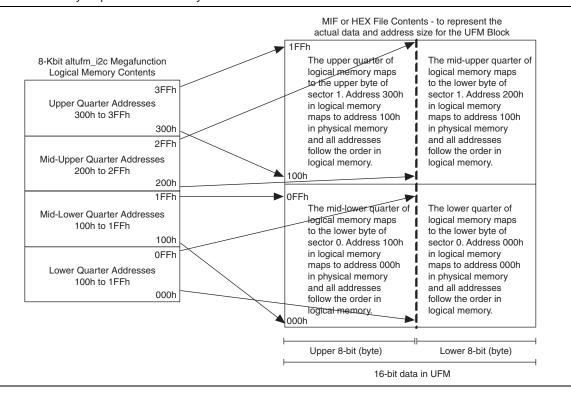

Table 9–2 shows the memory organization for the MAX II UFM block. There are 512 locations with 9 bits addressing a range of 000h to 1FFh. Each location stores 16-bit wide data. The most significant bit (MSB) of the address register indicates the sector in operation.

0FFh

| Table 9–2.         Memory Organization |         |         |  |  |

|----------------------------------------|---------|---------|--|--|

| Sector                                 | Address | s Range |  |  |

| 1                                      | 100h    | 1FFh    |  |  |

000h

## **Using and Accessing UFM Storage**

0

You can use the UFM to store data of different memory sizes and data widths. Even though the UFM storage width is 16 bits, you can implement different data widths or a serial interface with the altufm megafunction. Table 9–3 shows the different data widths available for the three types of interfaces supported in the Quartus II software.

Table 9–3. Data Widths for Logic Array Interfaces

| Logic Array Interface | Data Width (Bits)  | Interface Type |

|-----------------------|--------------------|----------------|

| l²C                   | 8                  | Serial         |

| SPI                   | 8 or 16            | Serial         |

| Parallel              | Options of 3 to 16 | Parallel       |

| None                  | 16                 | Serial         |

For more details about the logic array interface options in the altufm megafunction, refer to "Software Support for UFM Block" on page 9–13.

The UFM block is accessible through the logic array interface as well as the JTAG interface. However, the UFM logic array interface does not have access to the CFM block.

# **UFM Functional Description**

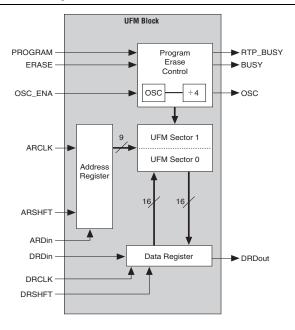

Figure 9–1 is the block diagram of the MAX II UFM block and the interface signals.

#### Figure 9–1. UFM Block and Interface Signals

Table 9-4 summarizes the MAX II UFM block input and output interface signals.

Table 9-4. UFM Interface Signals (Part 1 of 2)

| Port Name | Port Type | Description                                                                                                                                                                                                                                                                                                       |  |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DRDin     | Input     | Serial input to the data register. It is used to enter a data word when writing to the UFM. The data register is 16 bits wide and data is shifted serially from the least significant bit (LSB) to the MSB with each DRCLK. This port is required for writing, but unused if the UFM is in read-only mode.        |  |

| DRCLK     | Input     | Clock input that controls the data register. It is required and takes<br>control when data is shifted from DRDin to DRDout or loaded in<br>parallel from the flash memory. The maximum frequency for DRCLK<br>10 MHz.                                                                                             |  |

| DRSHFT    | Input     | Signal that determines whether to shift the data register or load it on a DRCLK edge. A high value shifts the data from DRDin into the LSB of the data register and from the MSB of the data register out to DRDout. A low value loads the value of the current address in the flash memory to the data register. |  |

| ARDin     | Input     | Serial input to the address register. It is used to enter the address of a memory location to read, program, or erase. The address register is 9 bits wide for the UFM size (8,192 bits).                                                                                                                         |  |

| Port Name | Port Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ARCLK     | Input     | Clock input that controls the address register. It is required when<br>shifting the address data from ARDin into the address register or<br>during the increment stage. The maximum frequency for ARCLK is 10<br>MHz.                                                                                                                                                                                                                                                                                   |  |

| ARSHFT    | Input     | Signal that determines whether to shift the address register or<br>increment it on an ARCLK edge. A high value shifts the data from<br>ARDin serially into the address register. A low value increments the<br>current address by 1. The address register rolls over to 0 when the<br>address space is at the maximum.                                                                                                                                                                                  |  |

| PROGRAM   | Input     | Signal that initiates a program sequence. On the rising edge, the data in the data register is written to the address pointed to by the address register. The $BUSY$ signal asserts until the program sequence is completed.                                                                                                                                                                                                                                                                            |  |

| ERASE     | Input     | Signal that initiates an erase sequence. On a rising edge, the memory sector indicated by the MSB of the address register will be erased. The BUSY signal asserts until the erase sequence is completed.                                                                                                                                                                                                                                                                                                |  |

| OSC_ENA   | Input     | This signal turns on the internal oscillator in the UFM block, and is optional but required when the OSC output is used. If OSC_ENA is driven high, the internal oscillator is enabled and the OSC output will toggle. If OSC_ENA is driven low, the internal oscillator is disabled ar the OSC output drives constant low.                                                                                                                                                                             |  |

| DRDout    | Output    | Serial output of the data register. Each time the DRCLK signal is<br>applied, a new value is available. The DRDout data depends on the<br>DRSHFT signal. When the DRSHFT signal is high, DRDout value is<br>the new value that is shifted into the MSB of the data register. If the<br>DRSHFT is low, DRDout would contain the MSB of the memory<br>location read into the data register.                                                                                                               |  |

| BUSY      | Output    | Signal that indicates when the memory is BUSY performing a<br>PROGRAM or ERASE instruction. When it is high, the address and data<br>register should not be clocked. The new PROGRAM or ERASE<br>instruction will not be executed until the BUSY signal is deasserted.                                                                                                                                                                                                                                  |  |

| OSC       | Output    | Output of the internal oscillator. It can be used to generate a clock to control user logic with the UFM. It requires an OSC enable input to produce an output.                                                                                                                                                                                                                                                                                                                                         |  |

| RTP_BUSY  | Output    | This output signal is optional and only needed if the real-time ISP feature is used. The signal is asserted high during real-time ISP and stays in the RUN_STATE for 500 ms before initiating real-time ISP to allow for the final read/erase/write operation. No read, write, erase, or address and data shift operations are allowed to be issued once the RTP_BUSY signal goes high. The data and address registers do not retain the contents of the last read or write operation for the UFM block |  |

during real-time ISP.

Table 9-4. UFM Interface Signals (Part 2 of 2)

To see the interaction between the UFM block and the logic array of MAX II devices, refer to the *MAX II Architecture* chapter in the *MAX II Device Handbook* (Figure 2–16 for EPM240 devices and Figure 2–17 for EPM570, EPM1270, and EPM2210 devices).

## **UFM Address Register**

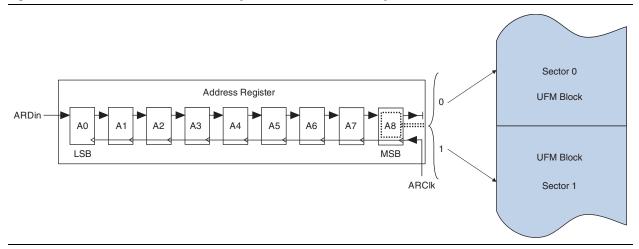

The MAX II UFM block is organized as a  $512 \times 16$  memory. Since the UFM block is organized into two separate sectors, the MSB of the address indicates the sector that will be in action; 0 is for sector 0 (UFM0) while 1 is for sector 1 (UFM1). An ERASE instruction erases the content of the specific sector that is indicated by the MSB of the address register. Figure 9–2 shows the selection of the UFM sector in action using the MSB of the address register.

Refer to "Erase" on page 9-11 for more information about ERASE mode.

Three control signals exist for the address register: ARSHFT, ARCLK, and ARDin. ARSHFT is used as both a shift-enable control signal and an auto-increment signal. If the ARSHFT signal is high, a rising edge on ARCLK will load address data serially from the ARDin port and move data serially through the register. A clock edge with the ARSHFT signal low increments the address register by 1. This implements an autoincrement of the address to allow data streaming. When a program, read, or an erase sequence is executing, the address that is in the address register becomes the active UFM location.

## **UFM Data Register**

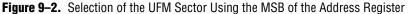

The UFM data register is 16 bits wide with four control signals: DRSHFT, DRCLK, DRDin, and DRDout. DRSHFT distinguishes between clock edges that move data serially from DRDin or to DRDout and clock edges that latch parallel data from the UFM sectors. If the DRSHFT signal is high, a clock edge moves data serially through the registers from DRDin to DRDout. If the DRSHFT signal is low, a clock edge captures data from the UFM sector pointed by the address register in parallel. The MSB is the first bit that will be seen at DRDout. The data register DRSHFT signal will also be used to enable the UFM for reading data. When the DRSHFT signal is low, the UFM latches data into the data register. Figure 9–3 shows the UFM data register.

#### Figure 9-3. UFM Data Register

## **UFM Program/Erase Control Block**

The UFM program/erase control block is used to generate all the control signals necessary to program and erase the UFM block independently. This reduces the number of LEs necessary to implement a UFM controller in the logic array. It also guarantees correct timing of the control signals to the UFM. A rising edge on either PROGRAM or ERASE causes this control signal block to activate and begin sequencing through the program or erase cycle. At this point, for a program instruction, whatever data is in the data register will be written to the address pointed to by the address register.

Only sector erase is supported by the UFM. Once an ERASE command is executed, this control block will erase the sector whose address is stored in the address register. When the PROGRAM or ERASE command first activates the program/erase control block, the BUSY signal will be driven high to indicate an operation in progress in the UFM. Once the program or erase algorithm is completed, the BUSY signal will be forced low.

## **Oscillator**

OSC\_ENA, one of the input signals in the UFM block, is used to enable the oscillator signal to output through the OSC output port. You can use this OSC output port to connect with the interface logic in the logic array. It can be routed through the logic array and fed back as an input clock for the address register (ARCLK) and the data register (DRCLK). The output frequency of the OSC port is one-fourth that of the oscillator frequency. As a result, the frequency range of the OSC port is 3.3 to 5.5 MHz. The maximum clock frequency accepted by ARCLK and DRCLK is 10 MHz and the duty cycle accepted by the DRCLK and ARCLK input ports is approximately 45% to 50%.

When the OSC\_ENA input signal is asserted, the oscillator is enabled and the output is routed to the logic array through the OSC output. When the OSC\_ENA is set low, the OSC output drives constant low. The routing delay from the OSC port of the UFM block to OSC output pin depends on placement. You can analyze this delay using the Quartus II timing analyzer.

The undivided internal oscillator, which is not accessible, operates in a frequency range from 13.33 to 22.22 MHz. The internal oscillator is enabled during power-up, insystem programming, and real-time ISP. At all other times, the oscillator is not running unless the UFM is instantiated in the design and the OSC\_ENA port is asserted. To see how specific operating modes of ALTUFM handle OSC\_ENA and the oscillator, refer to "Software Support for UFM Block" on page 9–13. For user generated logic interfacing to the UFM, the oscillator must be enabled during PROGRAM or ERASE operations, but not during READ operations. OSC\_ENA can be tied low if you are not issuing any PROGRAM or ERASE commands.

- During real-time ISP operation, the internal oscillator automatically enables and outputs through the OSC output port (if this port is instantiated) even though the OSC\_ENA signal is tied low. You can use the RTP\_BUSY signal to detect the beginning and ending of the real-time ISP operation for gated control of this self-enabled OSC output condition.

- The internal oscillator is not enabled all the time. The internal oscillator for the program/erase operation is only activated when the flash memory block is being programmed or erased. During the READ operation, the internal oscillator is activated whenever the flash memory block is reading data.

## Instantiating the Oscillator without the UFM

You can use the IO/MAX II oscillator megafunction selection in the MegaWizard<sup>®</sup> Plug-In Manager to instantiate the UFM oscillator if you intend to use this signal without using the UFM memory block. Figure 9–4 shows the altufm\_osc megafunction instantiation in the Quartus II software.

#### Figure 9-4. The Quartus II altufm\_osc Megafunction

This megafunction is in the I/O folder on page 2a of the MegaWizard<sup>®</sup> Plug-In Manager, as shown in Figure 9–5. You can start the MegaWizard Plug-In Manager on the Tools menu.

| Which megafunction would you like to customize?<br>Select a megafunction from the list below                                                                                                                                                 | Which device family will you be MAX II                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                              | Which type of output file do you want to create?         AHDL         VHDL         Verilog HDL         What name do you want for the output file?         Browse         jles\Projects\MAXII HB\extract\RT_ISP_Download\QII_Design\c                                                                                                                                                                     |

| ALTDDIO_BIDIR<br>ALTDDIO_IN<br>ALTDDIO_UT<br>ALTDQ<br>ALTDQ<br>ALTDQ<br>ALTQS<br>ALTGXB<br>ALTIGNUF<br>ALTIVDS<br>ALTNEMPHY<br>ALTOCT<br>ALTPLL<br>ALTPLL<br>ALTPLL<br>ALTPLL<br>ALTPLL<br>ALTPLMATE<br>ALTREMOTE_UPDATE<br>MAXII ossillator | Return to this page for another create operation Note: To compile a project successfully in the Quartus II software, your design files must be in the project directory, in the global user libraries specified in the Options dialog box (Tools menu), or a user library specified in the User Libraries page of the Settings dialog box (Assignments menu). Your current user library directories are: |

Figure 9–5. Selecting the altufm\_osc Megafunction in the MegaWizard Plug-In Manager

Figure 9–6 shows page 3 of the IO/MAX II oscillator megafunction. You have an option to choose to simulate the OSC output port at its maximum or minimum frequency during the design simulation. The frequency chosen is only used as a timing parameter simulation and does not affect the real MAX II device OSC output frequency.

Figure 9-6. Page 3 of the OSC Megafunction MegaWizard Plug-In Manager

| IO/MAX II Osc                 | About Documentation                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter<br>Settings         | Currently selected gevice family: MAX II MAX II<br>Match project/default<br>Match project/default<br>Match project/default<br>Memory When the oscillator function is used, the User<br>Flash Memory feature is not available.<br>What is the oscillator frequency for the 'osc' <u>5.56 MHz</u><br>output?<br>Note : The frequency setting is for simulation<br>only and has no impact on the on-chip<br>oscillator frequency |

| Resource Usage<br>1 maxii_ufm | Cancel < Back Next > Einish                                                                                                                                                                                                                                                                                                                                                                                                   |

# **UFM Operating Modes**

There are three different modes for the UFM block:

- Read/Stream Read

- Program (Write)

- Erase

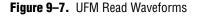

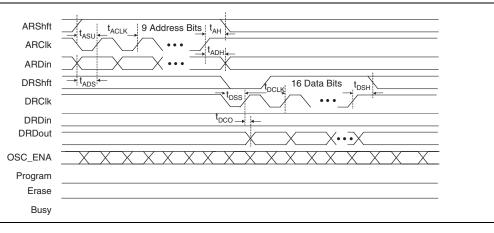

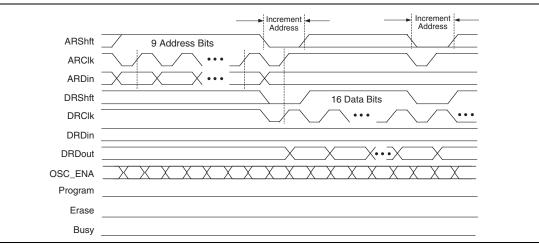

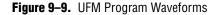

During program, address and data can be loaded concurrently. You can manipulate the UFM interface controls as necessary to implement the specific protocol provided the UFM timing specifications are met. Figure 9–7 through Figure 9–10 show the control waveforms for accessing UFM in three different modes. For PROGRAM mode (Figure 9–9) and ERASE mode (Figure 9–10), the PROGRAM and ERASE signals are not obligated to assert immediately after loading the address and data. They can be asserted anytime after the address register and data register have been loaded. Do not assert the READ, PROGRAM, and ERASE signals or shift data and address into the UFM after entering the real-time ISP mode. You can use the RTP\_BUSY signal to detect the beginning and end of real-time ISP operation and generate control logic to stop all UFM port operations. This user-generated control logic is only necessary for the altufm\_none megafunction, which provides no auto-generated logic. The other interfaces for the altufm megafunction (altufm\_parallel, altufm\_spi, altufm\_i2c) contain control logic to automatically monitor the RTP\_BUSY signal and will cease operations to the UFM when a real-time ISP operation is in progress.

- You can program the UFM and CFM blocks independently without overwriting the other block which is not programmed. The Quartus II programmer provides the options to program the UFM and CFM blocks individually or together (the entire MAX II Device).

- Refer to the *In-System Programmability Guidelines for MAX II Devices* chapter in the *MAX II Device Handbook* for guidelines about using ISP and real-time ISP while utilizing the UFM block within your design.

Refer to the MAX II Architecture chapter in the MAX II Device Handbook for a complete description of the device architecture, and for the specific values of the timing parameters listed in this chapter.

## **Read/Stream Read**

The three control signals, PROGRAM, ERASE, and BUSY are not required during read or stream read operation. To perform a read operation, the address register has to be loaded with the reference address where the data is or is going to be located in the UFM. The address register can be stopped from incrementing or shifting addresses from ARDin by stopping the ARCLK clock pulse. DRSHFT must be asserted low at the next rising edge of DRCLK to load the data from the UFM to the data register. To shift the bits from the register, 16 clock pulses have to be provided to read 16-bit wide data. You can use DRCLK to control the read time or disable the data register by discontinuing the DRCLK clock pulse. Figure 9–7 shows the UFM control waveforms during read mode.

The UFM block can also perform stream read operation, reading continuously from the UFM using the address increment feature. Stream read mode is started by loading the base address into the address register. DRSHFT must then be asserted low at the first rising edge of DRCLK to load data into the data register from the address pointed to by the address register. DRSHFT will then assert high to shift out the 16-bit wide data with the MSB out first. Figure 9–8 shows the UFM control waveforms during stream read mode.

## Program

To program or write to the UFM, you must first perform a sequence to load the reference address into the address register. DRSHFT must then be asserted high to load the data serially into the data register starting with the MSB. Loading an address into the address register and loading data into the data register can be done concurrently. After the 16 bits of data have been successfully shifted into the data register, the PROGRAM signal must be asserted high to start writing to the UFM. On the rising edge, the data currently in the data register is written to the location currently in the address register. The BUSY signal is asserted until the program sequence is completed. The

data and address register should not be modified until the BUSY signal is de-asserted, or the flash content will be corrupted. The PROGRAM signal is ignored if the BUSY signal is asserted. When the PROGRAM signal is applied at exactly the same time as the ERASE signal, the behavior is undefined and the contents of flash is corrupted. Figure 9–9 shows the UFM waveforms during program mode.

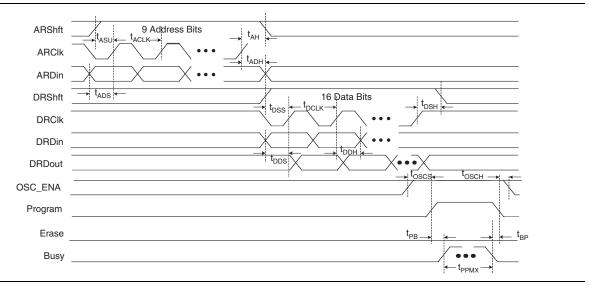

## Erase

The ERASE signal initiates an erase sequence to erase one sector of the UFM. The data register is not needed to perform an erase sequence. To indicate the sector of the UFM to be erased, the MSB of the address register should be loaded with 0 to erase the UFM sector 0, or 1 to erase the UFM sector 1 (Figure 9–2 on page 9–5). On a rising edge of the ERASE signal, the memory sector indicated by the MSB of the address register will be erased. The BUSY signal is asserted until the erase sequence is completed. The address register should not be modified until the BUSY signal is deasserted to prevent the content of the flash from being corrupted. This ERASE signal will be ignored when the BUSY signal is asserted. Figure 9–10 illustrates the UFM waveforms during erase mode.

When the UFM sector is erased, it has 16-bit locations all filled with FFFF. Each UFM storage bit can be programmed no more than once between erase sequences. You can write to any word up to two times as long as the second programming attempt at that location only adds 0s. 1s are mask bits for your input word that cannot overwrite 0s in the flash array. New 1s in the location can only be achieved by an erase. Therefore, it is possible for you to perform byte writes since the UFM array is 16 bits for each location.

#### Figure 9–10. UFM Erase Waveforms

# Programming and Reading the UFM with JTAG

In Altera MAX II devices, you can write or read data to/from the UFM using the IEEE Std. 1149.1 JTAG interface. You can use a PC or UNIX workstation, the Quartus II Programmer, and the ByteBlaster<sup>™</sup> MV or ByteBlaster<sup>™</sup> II parallel port download cable to download Programmer Object File (**.pof**), Jam<sup>™</sup> Standard Test and Programming Language (STAPL) Files (**.jam**), or Jam Byte-Code Files (**.jbc**) from the Quartus II software targeting the MAX II device UFM block.

The POF, Jam File, or JBC File can be generated using the Quartus II software.

### **Jam Files**

Both Jam STAPL and JBC files support programming for the UFM block.

### **Jam Players**

Jam Players read the descriptive information in Jam files and translate them into data that programs the target device. Jam Players do not program a particular device architecture or vendor; they only read and understand the syntax defined by the Jam file specification. In-field changes are confined to the Jam file, not the Jam Player. As a result, you do not need to modify the Jam Player source code for each in-field upgrade.

There are two types of Jam Players to accommodate the two types of Jam files: an ASCII Jam STAPL Player and a Jam STAPL Byte-Code Player. Both ASCII Jam STAPL Player and Jam STAPL Byte-Code Player are coded in the C programming language for 16-bit and 32-bit processors.

For guidelines on UFM operation during ISP, refer to the *In-System Programmability Guidelines for MAX II Devices* chapter in the *MAX II Device Handbook*.

# **Software Support for UFM Block**

The Altera Quartus II software includes sophisticated tools that fully utilize the advantages of UFM block in MAX II device, while maintaining simple, easy-to-use procedures that accelerate the design process. The following section describes how the altufm megafunction supports a simple design methodology for instantiating standard interface protocols for the UFM block, such as:

- I<sup>2</sup>C

- SPI

- Parallel

- None (Altera Serial Interface)

This section includes the megafunction symbol, the input and output ports, a description of the MegaWizard Plug-In Manager options, and example MegaWizard screen shots. Refer to Quartus II Help for the altufm megafunction AHDL functional prototypes (applicable to Verilog HDL), VHDL component declaration, and parameter descriptions. Figure 9–11 shows altufm megafunction selection (Flash Memory) in the MegaWizard Plug-In Manager. This megafunction is in the **memory compiler** directory on page 2a of the MegaWizard Plug-In Manager. You can start the MegaWizard Plug-In Manager on the Tools menu.

Figure 9-11. altufm Megafunction Selection in the MegaWizard Plug-In Manager

| Which megafunction would you like to customize?<br>Select a megafunction from the list below                                                                                                                                      | Which device family will you be MAX II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Matalled Plug-Ins     Altera SOPC Builder     Arithmetic     Gar Communications         | Which type of output file do you want to create? C AHDL C VHDL C Verilog HDL What name do you want for the output file? Browse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Interfaces     JTAG-accessible Extensions     Additional Compiler     CAM     FIFO partitioner     RAM: 1-PORT     RAM: 2-PORT     RAM: 2-PORT     RAM: 2-PORT     Shift register (RAM-based)     Shift register     IP MegaStore | iles       Projects       MAX II HB       HB |

The altufm MegaWizard Plug-In Manager has separate pages that apply to the MAX II UFM block. During compilation, the Quartus II Compiler verifies the altufm parameters selected against the available logic array interface options, and any specific assignments.

## **Inter-Integrated Circuit**

Inter-Integrated Circuit (I<sup>2</sup>C) is a bidirectional two-wire interface protocol, requiring only two bus lines; a serial data/address line (SDA), and a serial clock line (SCL). Each device connected to the I<sup>2</sup>C bus is software addressable by a unique address. The I<sup>2</sup>C bus is a multi-master bus where more than one integrated circuit (IC) capable of initiating a data transfer can be connected to it, which allows masters to function as transmitters or receivers.

The altufm\_i2c megafunction features a serial, 8-bit bidirectional data transfer up to 100 Kbits per second. With the altufm\_i2c megafunction, the MAX II UFM and logic can be configured as a slave device for the I<sup>2</sup>C bus. The altufm megafunction's I<sup>2</sup>C interface is designed to function similar to I<sup>2</sup>C serial EEPROMs.

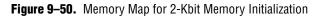

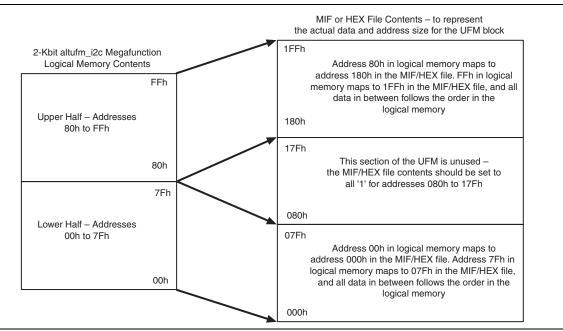

The Quartus II software supports three different memory sizes:

- (128 × 8) 1 Kbits

- (256 × 8) 2 Kbits

- (512 × 8) 4 Kbits

- (1,024 × 8) 8 Kbits

## I<sup>2</sup>C Protocol

The following defines the characteristics of the I<sup>2</sup>C bus protocol:

- Only two bus lines are required: SDA and SCL. Both SDA and SCL are bidirectional lines which remain high when the bus is free.

- Data transfer can be initiated only when the bus is free.

- The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change when the clock signal on the SCL line is low.

- Any transition on the SDA line while the SCL is high is one such unique case which indicates a start or stop condition.

Table 9–5 summarizes the altufm\_i2c megafunction input and output interface signals.

| Pin                                              | Description              | Function                                                                                                                                                                                                       |

|--------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA                                              | Serial Data/Address Line | The bidirectional SDA port is used to transmit and receive serial data from the UFM. The output stage of the SDA port is configured as an open drain pin to perform the wired-AND function.                    |

| SCL                                              | Serial Clock Line        | The bidirectional SCL port is used to synchronize the serial data transfer to and from the UFM. The output stage of the SCL port is configured as an open drain pin to perform a wired-AND function.           |

| WP                                               | Write Protect            | Optional active high signal that disables the erase and write function for read/write mode. The altufm_i2c megafunction gives you an option to protect the entire UFM memory or only the upper half of memory. |

| A <sub>2</sub> , A <sub>1</sub> , A <sub>0</sub> | Slave Address Input      | These inputs set the UFM slave address. The $A_6$ , $A_5$ , $A_4$ , $A_3$ slave address bits are programmable, set internally to 1010 by default.                                                              |

Table 9–5. altufm\_i2c Interface Signals

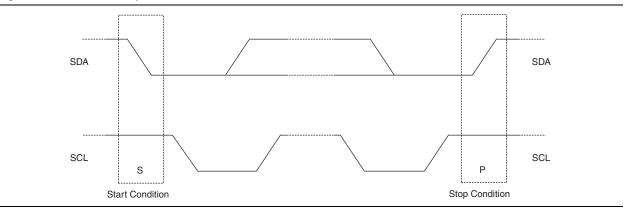

#### **START and STOP Condition**

The master always generates start (S) and stop (P) conditions. After the start condition, the bus is considered busy. Only a stop (P) condition frees the bus. The bus stays busy if the repeated start (Sr) condition is executed instead of a stop condition. In this occurrence, the start (S) and repeated start (Sr) conditions are functionally identical.

A high-to-low transition on the SDA line while the SCL is high indicates a start condition. A low-to-high transition on the SDA line while the SCL is high indicates a stop condition. Figure 9–12 shows the start and stop conditions.

Figure 9–12. Start and Stop Conditions

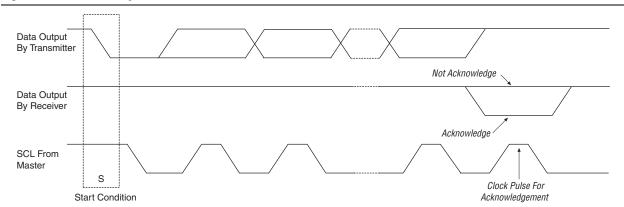

#### Acknowledge

Acknowledged data transfer is a requirement of I<sup>2</sup>C. The master must generate a clock pulse to signify the acknowledge bit. The transmitter releases the SDA line (high) during the acknowledge clock pulse.

The receiver (slave) must pull the SDA line low during the acknowledge clock pulse so that SDA remains a stable low during the clock high period, indicating positive acknowledgement from the receiver. If the receiver pulls the SDA line high during the acknowledge clock pulse, the receiver sends a not-acknowledge condition indicating that it is unable to process the last byte of data. If the receiver is busy (for example, executing an internally-timed erase or write operation), it will not acknowledge any new data transfer. Figure 9–13 shows the acknowledge condition on the I<sup>2</sup>C bus.

Figure 9–13. Acknowledge on the I<sup>2</sup>C Bus

## **Device Addressing**

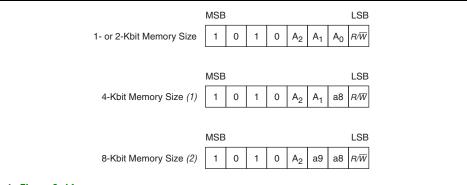

After the start condition, the master sends the address of the particular slave device it is requesting. The four most significant bits (MSBs) of the 8-bit slave address are usually fixed while the next three significant bits  $(A_2, A_1, A_0)$  are device address bits and define which device the master is accessing. The last bit of the slave address specifies whether a read or write operation is to be performed. When this bit is set to 1, a read operation is selected. When this bit is set to 0, a write operation is selected.

The four MSBs of the slave address ( $A_6$ ,  $A_5$ ,  $A_4$ ,  $A_3$ ) are programmable and can be defined on page 3 of the altufm MegaWizard Plug-In Manager. The default value for these four MSBs is 1010. The next three significant bits are defined using the three  $A_2$ ,  $A_1$ ,  $A_0$  input ports of the altufm\_i2c megafunction. You can connect these ports to input pins in the design file and connect them to switches on the board. The other option is to connect them to  $V_{CC}$  and GND primitives in the design file, which conserves pins. Figure 9–14 shows the slave address bits.

#### Figure 9–14. Slave Address Bits

## Notes to Figure 9–14:

(1) For the 4-Kbit memory size, the A<sub>0</sub> location in the slave address becomes the MSB (a8) of the memory byte address.

(2) For the 8-Kbit memory size, the A<sub>0</sub> location in the slave address becomes a8 of the memory byte address, while the A<sub>1</sub> location in the slave address becomes the MSB (a9) of the memory byte address.

After the master sends a start condition and the slave address byte, the altufm\_i2c logic monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slave address. The altufm\_i2c megafunction then performs a read or write operation to/from the UFM, depending on the state of the bit.

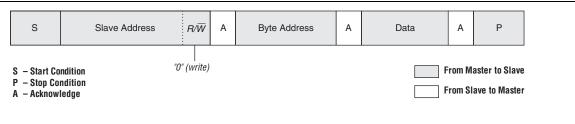

#### **Byte Write Operation**

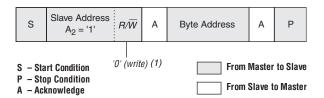

The master initiates a transfer by generating a start condition, then sending the correct slave address (with the  $R/\overline{W}$  bit set to 0) to the slave. If the slave address matches, the altufm\_i2c slave acknowledges on the ninth clock pulse. The master then transfers an 8-bit byte address to the UFM, which acknowledges the reception of the address. The master transfers the 8-bit data to be written to the UFM. Once the altufm\_i2c logic acknowledges the reception of the 8-bit data, the master generates a stop condition. The internal write from the MAX II logic array to the UFM begins only after the master generates a stop condition. While the UFM internal write cycle is in progress, the altufm\_i2c logic ignores any attempt made by the master to initiate a new transfer. Figure 9–15 shows the Byte Write sequence.

#### Figure 9-15. Byte Write Sequence

## **Page Write Operation**

Page write operation has a similar sequence as the byte write operation, except that a number of bytes of data are transmitted in sequence before the master issues a stop condition. The internal write from the MAX II logic array to the UFM begins only after the master generates a stop condition. While the UFM internal write cycle is in progress, the altufm\_i2c logic ignores any attempt made by the master to initiate a new transfer. The altufm\_i2c megafunction allows you to choose the page size of 8 bytes, 16 bytes, or 32 bytes for the page write operation, as shown in Figure 9–24 on page 9–24.

A write operation is only possible on an erased UFM block or word location. The UFM block differs from serial EEPROMs, requiring an erase operation prior to writing new data in the UFM block. A special erase sequence is required, as discussed in "Erase Operation" on page 9–18.

## **Acknowledge Polling**

The master can detect whether the internal write cycle is completed by polling for an acknowledgement from the slave. The master can resend the start condition together with the slave address as soon as the byte write sequence is finished. The slave does not acknowledge if the internal write cycle is still in progress. The master can repeat the acknowledge polling and can proceed with the next instruction after the slave acknowledges.

## Write Protection

The altufm\_i2c megafunction includes an optional Write Protection (WP) port available on page 4 of the altufm MegaWizard Plug-In Manager (see Figure 9–24 on page 9–24). In the MegaWizard Plug-In Manager, you can choose the WP port to protect either the full or upper half memory.

When WP is set to 1, the upper half or the entire memory array (depending on the write protection level selected) is protected, and the write and erase operation is not allowed. In this case the altufm\_i2c megafunction acknowledges the slave address and memory address. After the master transfers the first data byte, the altufm\_i2c megafunction sends a not-acknowledge condition to the master to indicate that the instruction will not execute. When WP is set to 0, the write and erase operations are allowed.

## **Erase Operation**

Commercial serial EEPROMs automatically erase each byte of memory before writing into that particular memory location during a write operation. However, the MAX II UFM block is flash based and only supports sector erase operations and not byte erase operations. When using read/write mode, a sector or full memory erase operation is required before writing new data into any location that previously contained data. The block cannot be erased when the altufm\_i2c megafunction is in read-only mode.

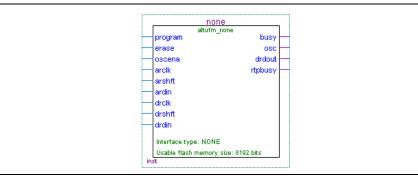

Data can be initialized into memory for read/write and read-only modes by including a memory initialization file (**.mif**) or hexidecimal file (**.hex**) in the altufm MegaWizard Plug-In Manager. This data is automatically written into the UFM during device programming by the Quartus II software or third-party programming tool.

The altufm\_i2c megafunction supports four different erase operation methods shown on page 4 of the altufm MegaWizard Plug-In Manager:

- Full Erase (Device Slave Address Triggered)

- Sector Erase (Byte Address Triggered)

- Sector Erase (A<sub>2</sub> Triggered)

- No Erase

These erase options only work as described if that particular option is selected in the MegaWizard Plug-In Manager before compiling the design files and programming the device. Only one option is possible for the altufm\_i2c megafunction.

Erase options are discussed in more detail in the following sections.

#### Full Erase (Device Slave Address Erase)

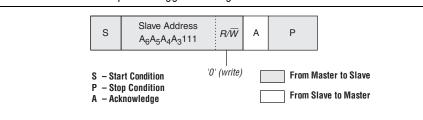

The full erase option uses the  $A_2$ ,  $A_1$ ,  $A_0$  bits of the slave address to distinguish between an erase or read/write operation. This slave operation decoding occurs when the master transfers the slave address to the slave after generating the start condition. If the  $A_2$ ,  $A_1$ , and  $A_0$  slave address bits transmitted to the UFM slave equals 111 and the four remaining MSBs match the rest of the slave addresses, then the Full Erase operation is selected. If the  $A_6$ ,  $A_5$ ,  $A_4$ ,  $A_3$   $A_2$ ,  $A_1$ , and  $A_0$  slave address bits transmitted to the UFM match its unique slave address setting, the read/write operation is selected and functions as expected. As a result, this erase option utilizes two slave addresses on the bus reserving  $A_6$ ,  $A_5$ ,  $A_4$ ,  $A_3$ , 1, 1, 1 as the erase trigger. Both sectors of the UFM block will be erased when the Full Erase operation is executed. This operation requires acknowledge polling. The internal UFM erase function only begins after the master generates a stop condition. Figure 9–16 shows the full erase sequence triggered by using the slave address.

If the memory is write-protected (WP = 1), the slave does not acknowledge the erase trigger slave address ( $A_6$ ,  $A_5$ ,  $A_4$ ,  $A_3$ , 1, 1, 1) sent by the master. The master should then send a stop condition to terminate the transfer. The full erase operation will not be executed.

#### Sector Erase (Byte Address Triggered)

This sector erase operation is triggered by defining a 7- to 10-bit byte address for each sector depending on the memory size. The trigger address for each sector is entered on page 4 of the altufm MegaWizard Plug-In Manager, as shown in Figure 9–24 on page 9–24. When a write operation is executed targeting this special byte address location, the UFM sector that contains that byte address location is erased. This sector erase operation is automatically followed by a write of the intended write byte to that address. The default byte address location for UFM Sector 0 erase is address 0x00. The default byte address location for UFM Sector 1 erase is [(selected memory size)/2]. You can specify another byte location as the trigger-erase addresses for each sector.

This sector erase operation supports up to eight UFM blocks or serial EEPROMs on the I<sup>2</sup>C bus. This sector erase operation requires acknowledge polling.

#### Sector Erase (A<sub>2</sub> Triggered)

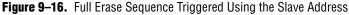

This sector erase operation uses the received  $A_2$  slave address bit to distinguish between an erase or read/write operation. This slave operation decoding occurs when the master transmits the slave address after generating the start condition. If the  $A_2$  bit received by the UFM slave is 1, the sector erase operation is selected. If the  $A_2$  bit received is 0, the read/write operation is selected. While this reserves the  $A_2$  bit as an erase or read/write operation bit, the  $A_0$  and  $A_1$  bits still act as slave address bits to address the UFM. With this erase option, there can be up to four UFM slaves cascaded on the bus for 1-Kbit and 2-Kbit memory sizes. Only two UFM slaves can be cascaded on the bus for 4-Kbit memory size, since  $A_0$  of the slave address becomes the ninth bit (MSB) of the byte address. After the slave acknowledges the slave address and its erase or read/write operation bit, the master can transfer any byte address within the sector that must be erased. The internal UFM sector erase operation only begins after the master generates a stop condition. Figure 9–17 shows the sector erase sequence using the  $A_2$  bit of the slave address.

Figure 9–17. Sector Erase Sequence Indicated Using the A<sub>2</sub> Bit of the Slave Address

#### Note to Figure 9-17:

(1)  $A_2 = 0$  indicates a read/write operation is executed in place of an erase. In this case, the R/W bit determines whether it is a read or write operation.

If the altufm\_i2c megafunction is write-protected (WP=1), the slave does not acknowledge the byte address (which indicates the UFM sector to be erased) sent in by the master. The master should then send a stop condition to terminate the transfer and the sector erase operation will not be executed.

## No Erase

The no erase operation never erases the UFM contents. This method is recommended when UFM does not require constant re-writing after its initial write of data. For example, if the UFM data is to be initialized with data during manufacturing using I<sup>2</sup>C, you may not require writing to the UFM again. In that case, you should use the no erase option and save logic element (LE) resources from being used to create erase logic.

## **Read Operation**

The read operation is initiated in the same manner as the write operation except that the R/W bit must be set to 1. Three different read operations are supported:

- Current Address Read (Single Byte)

- Random Address Read (Single byte)

- Sequential Read (Multi-Byte)

After each UFM data has been read and transferred to the master, the UFM address register is incremented for all single and multi-byte read operations.

#### **Current Address Read**

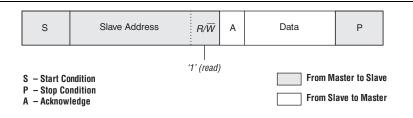

This read operation targets the current byte location pointed to by the UFM address register. Figure 9–18 shows the current address read sequence.

Figure 9–18. Current Address Read Sequence

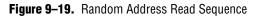

#### **Random Address Read**

Random address read operation allows the master to select any byte location for a read operation. The master first performs a "dummy" write operation by sending the start condition, slave address, and byte address of the location it wishes to read. After the altufm\_i2c megafunction acknowledges the slave and byte address, the master generates a repeated start condition, the slave address, and the R/W bit is set to 1. The altufm\_i2c megafunction then responds with acknowledge and sends the 8-bit data requested. The master then generates a stop condition. Figure 9–19 shows the random address read sequence.

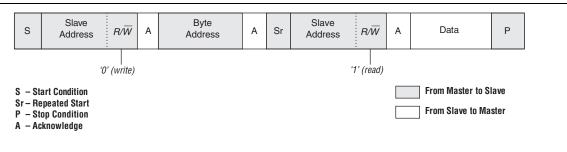

#### **Sequential Read**

Sequential read operation can be initiated by either the current address read operation or the random address read operation. Instead of sending a stop condition after the Slave has transmitted one byte of data to the master, the master acknowledges that byte and sends additional clock pulses (on SCL line) for the slave to transmit data bytes from consecutive byte addresses. The operation is terminated when the master generates a stop condition instead of responding with an acknowledge. Figure 9–20 shows the sequential read sequence.

Figure 9–20. Sequential Read Sequence

## **ALTUFM I<sup>2</sup>C Interface Timing Specification**

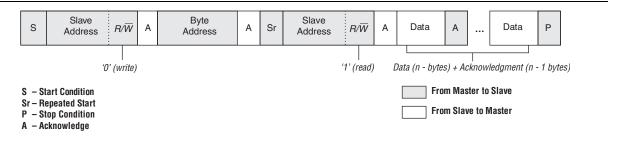

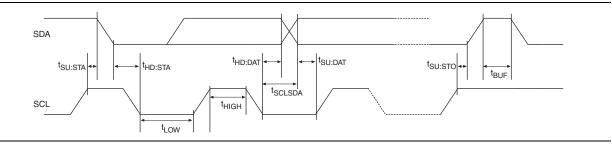

Figure 9–21 shows the timing waveform for the altufm\_i2c megafunction read/write mode.

Table 9–6 through Table 9–8 list the timing specification needed for the altufm\_i2c megafunction read/write mode.

Table 9–6. I2C Interface Timing Specification

| Symbol               | Parameter                                        | Min | Max | Unit |

|----------------------|--------------------------------------------------|-----|-----|------|

| F <sub>SCL</sub>     | SCL clock frequency                              | —   | 100 | kHz  |

| t <sub>scl:sda</sub> | SCL going low to SDA data out                    | —   | 15  | ns   |

| t <sub>BUF</sub>     | Bus free time between a stop and start condition | 4.7 | —   | μs   |

| t <sub>hd:sta</sub>  | (Repeated) start condition hold time             | 4   |     | μs   |

| t <sub>su:sta</sub>  | (Repeated) start condition setup time            | 4.7 |     | μs   |

| t <sub>LOW</sub>     | SCL clock low period                             | 4.7 | —   | μs   |

| t <sub>HIGH</sub>    | SCL clock high period                            | 4   |     | μs   |

| t <sub>hd:dat</sub>  | SDA data in hold time                            | 0   |     | ns   |

| t <sub>su:dat</sub>  | SDA data in setup time                           | 20  | —   | ns   |

| t <sub>su:sto</sub>  | STOP condition setup time                        | 4   |     | ns   |

| Parameter        | Min | Max | Unit |

|------------------|-----|-----|------|

| Write Cycle Time |     | 110 | μs   |

#### Table 9–8. UFM Erase Cycle Time

| Parameter                  | Min | Max   | Unit |

|----------------------------|-----|-------|------|

| Sector Erase<br>Cycle Time | —   | 501   | ms   |

| Full Erase Cycle<br>Time   | _   | 1,002 | ms   |

### Instantiating the I2C Interface Using the Quartus II altufm Megafunction

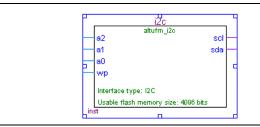

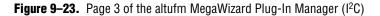

Figure 9–22 shows the altufm megafunction symbol for a I<sup>2</sup>C interface instantiation in the Quartus II software.

**Figure 9–22.** altufm Megafunction Symbol For the I<sup>2</sup>C Interface Instantiation in the Quartus II Software

Figure 9–23 shows page 3 of the altufm MegaWizard Plug-In Manager when selecting I<sup>2</sup>C as the interface. On this page, you can choose whether to implement the read/write mode or read-only mode for the UFM. You also have an option to choose the memory size for the altufm\_i2c megafunction as well as defining the four MSBs of the slave address (default 1010).

The UFM block's internal oscillator is always running when the altufm\_i2c megafunction is instantiated for both read-only and read/write interfaces.

Figure 9–24 shows page 4 of the altufm MegaWizard Plug-In Manager. You can select the optional write protection and erase operation methods on this page.

| address (MSB is always '0')                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Flash Memory                                                   | About Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i2c         aturm_j2c         sci         a1         sda         wp         Interface type: I2C         What is the write protect         Write protect         Write protect applies to the full memory         Write protect applies only to the upper half of the memory         What erase method should be used in I2C protocol?         Device Slave Address Full Erase (3 LSBs are 111)         Sector Erase Triggered by Byte Address         Sector 1: Trigger erase when writing to binary address (MSB is always '1')         100000000 | ings                                                           | os >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Resource Usage  O No Erase 3 lpm compare + 111 lut + 2 maxii io +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | i2c<br>atufm_22c<br>sci<br>a1 sda<br>wp<br>interface type: I2C | What is the write configuration for the I2C protocol?            • Single byte write             • Page write             • Write protect             • Write protect applies to the full memory             • Write protect applies only to the upper half of the memory             • Write protect applies only to the upper half of the memory             • Write protect applies only to the upper half of the memory             • What erase method should be used in I2C protocol?             • Device Slave Address Full Erase (3 LSBs are 111)             • Sector Erase Trigger erase when writing to binary         address (MSB is always 10)             • Sector I: Trigger erase when writing to binary         address (MSB is always 11)             • Sector Erase Triggered by 'a2' bit |

| Figure 9–24.   | Page 4 of the altufm   | MegaWizard Plug-In  | Manager ( | (1 <sup>2</sup> C) |

|----------------|------------------------|---------------------|-----------|--------------------|

| i iguio o III. | r ago r or tho altainn | inoganizara riag in | managor   |                    |

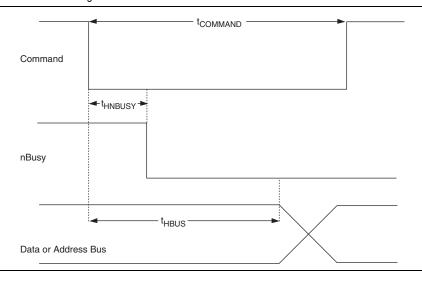

## **Serial Peripheral Interface**

Serial peripheral interface (SPI) is a four-pin serial communication subsystem included on the Motorola 6805 and 68HC11 series microcontrollers. It allows the microcontroller unit to communicate with peripheral devices, and is also capable of inter-processor communications in a multiple-master system.

The SPI bus consists of masters and slaves. The master device initiates and controls the data transfers and provides the clock signal for synchronization. The slave device responds to the data transfer request from the master device. The master device in an SPI bus initiates a service request with the slave devices responding to the service request.

With the altufm megafunction, the UFM and MAX II logic can be configured as a slave device for the SPI bus. The OSC\_ENA is always asserted to enable the internal oscillator when the SPI megafunction is instantiated for both read only and read/write interfaces.

The Quartus II software supports both the Base mode (which uses 8-bit address and data) and the Extended mode (which uses 16-bit address and data). Base mode uses only UFM sector 0 (2,048 bits), whereas Extended mode uses both UFM sector 0 and sector 1 (8,192 bits). There are only four pins in SPI: SI, SO, SCK, and nCS. Table 9–9 describes the SPI pins and functions.

| Pin | Description        | Function                                                                                            |

|-----|--------------------|-----------------------------------------------------------------------------------------------------|

| SI  | Serial Data Input  | Receive data serially.                                                                              |

| SO  | Serial Data Output | Transmit data serially.                                                                             |

| SCK | Serial Data Clock  | The clock signal produced from the master device to synchronize the data transfer.                  |

| nCS | Chip Select        | Active low signal that enables the slave device to receive or transfer data from the master device. |

**Table 9–9.** SPI Interface Signals

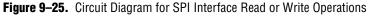

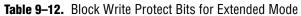

Data transmitted to the SI port of the slave device is sampled by the slave device at the positive SCK clock. Data transmits from the slave device through SO at the negative SCK clock edge. When nCS is asserted, it means the current device is being selected by the master device from the other end of the SPI bus for service. When nCS is not asserted, the SI and SCK ports should be blocked from receiving signals from the master device, and SO should be in High Impedance state to avoid causing contention on the shared SPI bus. All instructions, addresses, and data are transferred with the MSB first and start with high-to-low nCS transition. The circuit diagram is shown in Figure 9–25.

### **Opcodes**

The 8-bit instruction opcode is shown in Table 9–10. After nCS is pulled low, the indicated opcode must be provided. Otherwise, the interface assumes that the master device has internal logic errors and ignores the rest of the incoming signals. Once nCS is pulled back to high, the interface is back to normal. nCS should be pulled low again for a new service request.

| Name         | Opcode   | Operation                                 |

|--------------|----------|-------------------------------------------|

| WREN         | 00000110 | Enable Write to UFM                       |

| WRDI         | 00000100 | Disable Write to UFM                      |

| RDSR         | 00000101 | Read Status Register                      |

| WRSR         | 0000001  | Write Status Register                     |

| READ         | 00000011 | Read data from UFM                        |

| WRITE        | 00000010 | Write data to UFM                         |

| SECTOR-ERASE | 00100000 | Sector erase                              |

| UFM-ERASE    | 01100000 | Erase the entire UFM block (both sectors) |

The READ and WRITE opcodes are instructions for transmission, which means the data will be read from or written to the UFM.

WREN, WRDI, RDSR, and WRSR are instructions for the status register, where they do not have any direct interaction with UFM, but read or set the status register within the interface logic. The status register provides status on whether the UFM block is available for any READ or WRITE operation, whether the interface is WRITE enabled, and the state of the UFM WRITE protection. The status register format is shown in Table 9–11. For the read only implementation of ALTUFM SPI (Base or Extended mode), the status register does not exist, saving LE resources.

Table 9–11.

Status Register Format

| Position | Status | Default at Power-Up | Description                                              |

|----------|--------|---------------------|----------------------------------------------------------|

| Bit 7    | Х      | 0                   | -                                                        |

| Bit 6    | Х      | 0                   | -                                                        |

| Bit 5    | Х      | 0                   | —                                                        |

| Bit 4    | Х      | 0                   | -                                                        |

| Bit 3    | BP1    | 0                   | Indicate the current level of block write protection (1) |

| Bit 2    | BP0    | 0                   | Indicate the current level of block write protection (1) |

| Bit 1    | WEN    | 0                   | 1= SPI WRITE enabled state                               |

|          |        |                     | 0= SPI wRITE disabled state                              |

| Bit 0    | nRDY   | 0                   | 1 = Busy, UFM WRITE or ERASE cycle in progress           |

|          |        |                     | 0 = No UFM write or erase cycle in progress              |

#### Note to Table 9–11:

(1) Refer to Table 9–12 and Table 9–13 for more information about status register bits BPI and BPO.

The following paragraphs describe the instructions for SPI.

#### READ

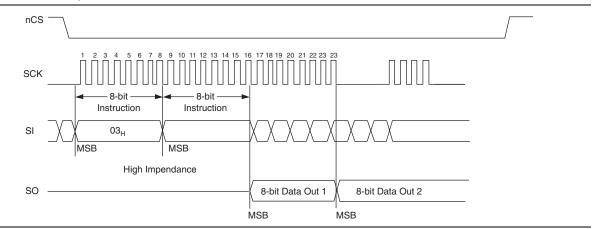

READ is the instruction for data transmission, where the data is read from the UFM block. When data transfer is taking place, the MSB is always the first bit to be transmitted or received. The data output stream is continuous through all addresses until it is terminated by a low-to-high transition at the nCS port. The READ operation is always performed through the following sequence in SPI, as shown in Figure 9–26:

- 1. nCS is pulled low to indicate the start of transmission.

- 2. An 8-bit READ opcode (0000011) is received from the master device. (If internal programming is in progress, READ is ignored and not accepted).

- 3. A 16-bit address is received from the master device. The LSB of the address is received last. As the UFM block can take only nine bits of address maximum, the first seven address bits received are discarded.

- 4. Data is transmitted for as many words as needed by the slave device through SO for READ operation. When the end of the UFM storage array is reached, the address counter rolls over to the start of the UFM to continue the READ operation.

- 5. nCS is pulled back to high to indicate the end of transmission.

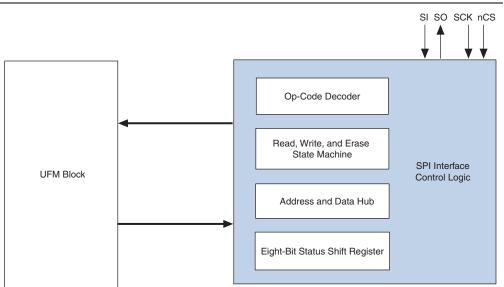

For SPI Base mode, the READ operation is always performed through the following sequence in SPI:

- 1. nCS is pulled low to indicate the start of transmission.

- 2. An 8-bit READ opcode (0000011) is received from the master device, followed by an 8-bit address. If internal programming is in progress, the READ operation is ignored and not accepted.

- 3. Data is transmitted for as many words as needed by the slave device through SO for READ operation. The internal address pointer automatically increments until the highest memory address is reached (address 255 only since the UFM sector 0 is used). The address counter will not roll over once address 255 is reached. The SO output is set to high-impedance (Z) once all the eight data bits from address 255 has been shifted out through the SO port.

- 4. nCS is pulled back to high to indicate the end of transmission.

Figure 9–26. READ Operation Sequence for Extended Mode

Figure 9–27 shows the READ operation sequence for Base mode.

### WRITE

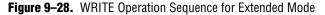

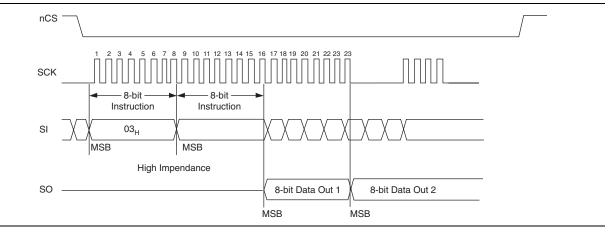

WRITE is the instruction for data transmission, where the data is written to the UFM block. The targeted location in the UFM block that will be written must be in the erased state ( $FFFF_H$ ) before initiating a WRITE operation. When data transfer is taking place, the MSB is always the first bit to be transmitted or received. nCS must be driven high before the instruction is executed internally. You may poll the nRDY bit in the software status register for the completion of the internal self-timed WRITE cycle. For SPI Extended mode, the WRITE operation is always done through the following sequence, as shown in Figure 9–28:

- 1. nCS is pulled low to indicate the start of transmission.

- 2. An 8-bit WRITE opcode (00000010) is received from the master device. If internal programming is in progress, the WRITE operation is ignored and not accepted.

- 3. A 16-bit address is received from the master device. The LSB of the address will be received last. As the UFM block can take only nine bits of address maximum, the first seven address bits received are discarded.

- 4. A check is carried out on the status register (see Table 9–11) to determine if the WRITE operation has been enabled, and the address is outside of the protected region; otherwise, Step 5 is bypassed.

- 5. One word (16 bits) of data is transmitted to the slave device through SI.

- 6. nCS is pulled back to high to indicate the end of transmission.

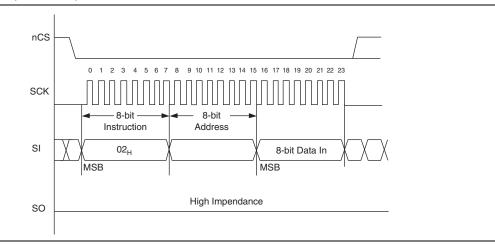

For SPI Base mode, the WRITE operation is always performed through the following sequence in SPI:

- 1. nCS is pulled low to indicate the start of transmission.

- 2. An 8-bit WRITE opcode (0000010) is received. If the internal programming is in progress, the WRITE operation is ignored and not accepted.

- 3. An 8-bit address is received. A check is carried out on the status register (see Table 9–11) to determine if the WRITE operation has been enabled, and the address is outside of the protected region; otherwise, Step 4 is skipped.

- 4. An 8-bit data is transmitted through SI.

- 5. nCS is pulled back to high to indicate the end of transmission.

Figure 9–29 shows the WRITE operation sequence for Base mode.

Figure 9–29. WRITE Operation Sequence for Base Mode

### SECTOR-ERASE

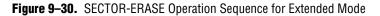

SECTOR-ERASE is the instruction of erasing one sector of the UFM block. Each sector contains 256 words. WEN bit and the sector must not be protected for SE operation to be successful. nCS must be driven high before the instruction is executed internally. You may poll the nRDY bit in the software status register for the completion of the internal self-timed SECTOR-ERASE cycle. For SPI Extended mode, the SE operation is performed in the following sequence, as shown in Figure 9–30:

- 1. nCS is pulled low.

- 2. Opcode 00100000 is transmitted into the interface.

- 3. The 16-bit address is sent. The eighth bit (the first seven bits will be discarded) of the address indicates which sector is erased; a 0 means sector 0 (UFM0) is erased, and a 1 means sector 1 (UFM1) is erased.

4. nCS is pulled back to high.

For SPI Base mode, the SE instruction erases UFM sector 0. As there are no choices of UFM sectors to be erased, there is no address component to this instruction. The SE operation is always done through the following sequence in SPI Base mode:

- 1. nCS is pulled low.

- 2. Opcode 00100000 is transmitted into the interface.

- 3. nCS is pulled back to high.

### **UFM-ERASE**

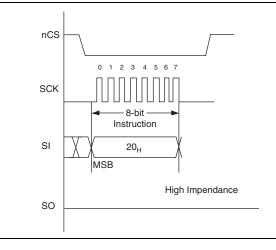

The UFM-ERASE (CE) instruction erases both UFM sector 0 and sector 1 for SPI Extended Mode. While for SPI Base mode, the CE instruction has the same functionality as the SECTOR-ERASE (SE) instruction, which erases UFM sector 0 only. WEN bit and the UFM sectors must not be protected for CE operation to be successful. nCS must be driven high before the instruction is executed internally. You may poll the nRDY bit in the software status register for the completion of the internal selftimed CE cycle. For both SPI Extended mode and Base mode, the UFM-ERASE operation is performed in the following sequence as shown in Figure 9–32:

- 1. nCS is pulled low.

- 2. Opcode 01100000 is transmitted into the interface.

- 3. nCS is pulled back to high.

Figure 9–32 shows the UFM-ERASE operation sequence.

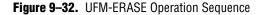

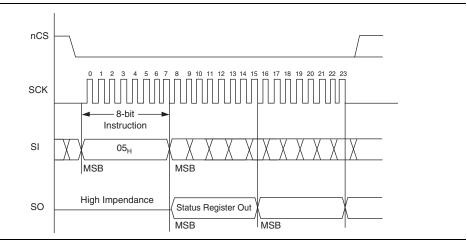

### WREN (Write Enable)

The interface is powered-up in the write disable state. Therefore, WEN in the status register (see Table 9–11) is 0 at power-up. Before any write is allowed to take place, WREN must be issued to set WEN in the status register to 1. If the interface is in readonly mode, WREN does not have any effect on WEN, since the status register does not exist. Once the WEN is set to 1, it can be reset by the WRDI instruction; the WRITE and SECTOR-ERASE instruction will not reset the WEN bit. WREN is issued through the following sequence, as shown in Figure 9–33:

- 1. nCS is pulled low.

- 2. Opcode 00000110 is transmitted into the interface to set WEN to 1 in the status register.

- 3. After the transmission of the eighth bit of WREN, the interface is in wait state (waiting for nCS to be pulled back to high). Any transmission after this is ignored.

- 4. nCS is pulled back to high.

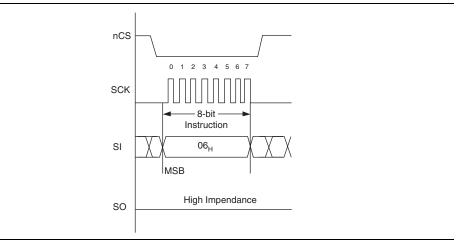

## WRDI (Write Disable)

After the UFM is programmed, WRDI can be issued to set WEN back to 0, disabling WRITE and preventing inadvertent writing to the UFM. WRDI is issued through the following sequence, as shown in Figure 9–34:

- 1. nCS is pulled low.

- 2. Opcode 00000100 is transmitted to set WEN to 0 in the status register.

- 3. After the transmission of the eighth bit of WRDI, the interface is in wait state (waiting for nCS to be pulled back to high). Any transmission after this is ignored.

- 4. nCS is pulled back to high.

#### Figure 9–34. WRDI Operation Sequence

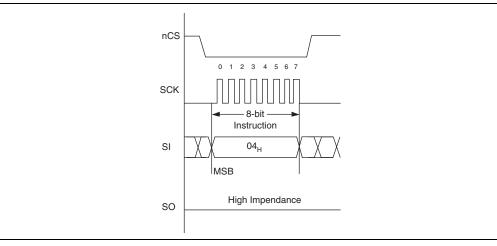

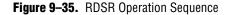

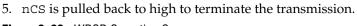

#### **RDSR (Read Status Register)**

The content of the status register can be read by issuing RDSR. Once RDSR is received, the interface outputs the content of the status register through the SO port. Although the most significant four bits (Bit 7 to Bit 4) do not hold valuable information, all eight bits in the status register will output through the SO port. This allows future compatibility when Bit 7 to Bit 4 have new meaning in the status register. During the

internal program cycle in the UFM, RDSR is the only valid opcode recognized by the interface (therefore, the status register can be read at any time), and nRDY is the only valid status bit. Other status bits are frozen and remain unchanged until the internal program cycle is ended. RDSR is issued through the following sequence, as shown in Figure 9–35:

- 1. nCS is pulled low.

- 2. Opcode 00000101 is transmitted into the interface.

- 3. SI ignores incoming signals; SO output the content of the status register, Bit 7 first and Bit 0 last.

- 4. If nCS is kept low, repeat step 3.

- 5. nCS is pulled back to high to terminate the transmission.

### WRSR (Write Status Register)

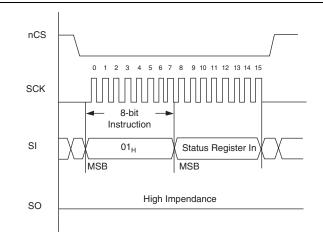

The block protection bits (BP1 and BP0) are the status bits used to protect certain sections of the UFM from inadvertent write. The BP1 and BP0 status are updated by WRSR. During WRSR, only BP1 and BP0 in the status register can be written with valid information. The rest of the bits in the status register are ignored and not updated. When both BP1 and BP0 are 0, there is no protection for the UFM. When both BP1 and BP0 are 1, there is full protection for the UFM. BP0 and BP1 are set to 0 upon power-up. Table 9–12 describe more on the Block Write Protect Bits for Extended mode, while Table 9–13 describes more on the Block Write Protect Bits for Base mode. WRSR is issued through the following sequence, as shown in Figure 9–36:

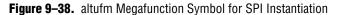

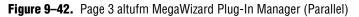

- 1. nCS is pulled low.