## Enhanced Configuration Devices

July 2008, Version 1.3 Errata Sheet

#### Introduction

This errata sheet provides updated information on enhanced configuration devices—EPC4, EPC8, and EPC16—which are used to configure SRAM-based programmable logic devices (PLDs). This document addresses known issues and includes methods to work around the issues.

# Intel-Flash-Based EPC Device Protection

Altera performed a die-sub replacement for the EPC4, EPC8, and EPC16 devices with Intel flash. Intel flash devices do not have the lock bit protection feature to lock the flash for protection during power-up or power-down. The lock bit protection feature is used to prevent unintentional writes and ensure data retention.

For more information about the flash die change in the Altera® enhanced configuration devices, refer to *Process Change Notification PCN0506:*Addition of Intel Flash Memory as Source for EPC4, EPC8 & EPC16 Enhanced Configuration Devices.

In the absence of the lock bit protection feature in the EPC4, EPC8, and EPC16 devices with Intel flash, Altera recommends four methods to protect the Intel flash content in EPC4, EPC8, and EPC16 devices. Any method alone is sufficient to protect the flash. The methods are listed below in the order of descending protection level:

- Using an RP# of less than 0.3 V on power-up and power-down for a minimum of 100 ns to a maximum 25 μs disables all control pins, making it impossible for a write to occur.

- 2. Using  $V_{PP} < V_{PPLK}$ , where the maximum value of  $V_{PPLK}$  is 1 V, disables writes.  $V_{PP} < V_{PPLK}$  means programming or writes cannot occur.  $V_{PP}$  is a programming supply voltage input pin on the Intel flash.  $V_{PP}$  is equivalent to the  $V_{CCW}$  pin on EPC devices (Refer to Figure 1).

- 3. Using a high CE# disables the chip. The requirement for a write is a low CE# and low WE#. A high CE# by itself prevents writes from occurring.

- Using a high WE# prevents writes because a write only occurs when the WE# is low.

Performing all four methods simultaneously is the safest protection for the flash content.

The ideal power-up sequence is as follows:

- 1. Power up  $V_{CC}$ .

- 2. Maintain  $V_{PP} < V_{PPLK}$  until  $V_{CC}$  is fully powered up.

- 3. Power up  $V_{PP}$

- 4. Drive RP# low during the entire power-up process. RP# must be released high within 25  $\mu$ s after  $V_{PP}$  is powered up.

CE# and WE# must be high for the entire power-up sequence.

The ideal power-down sequence is as follows:

- 1. Drive RP# low for 100 ns before power-down.

- 2. Power down  $V_{PP} < V_{PPLK}$ .

- 3. Power down  $V_{CC}$ .

- 4. Drive RP# low during the entire power-down process.

CE# and WE# must be high for the entire power-down sequence.

The RP# pin is not internally connected to the controller. Therefore, an external loop-back connection between C-RP# and F-RP# must be made on the board even when you are not using the external flash interface. When using the external flash interface, connect the external device to the RP# pin with the loop back. Tri-state RP# at all times when the flash is not in use.

If an external power-up monitoring circuit is connected to the RP# pin with the loop-back, use the following guidelines to avoid contention on the RP# line:

- The power-up sequence on the 3.3-V supply should complete within 50 ms of power-up. The 3.3-V  $V_{CC}$  should reach the minimum  $V_{CC}$  before 50 ms and RP# should then be released.

- RP# should be driven low by the power-up monitoring circuit during power-up. After power-up, RP# should be tri-stated externally by the power-up monitoring circuit.

2 Altera Corporation

If the preceding guidelines cannot be completed within 50 ms, then the OE pin must be driven low externally until RP# is ready to be released.

Figure 1 shows an example of configuration schematic using EPC device in FPP mode with the extended flash interface in use.

Enhanced Configuration Device PLD or Processor Stratix Series WE#C WE#F WE# APEX II Device RP#C RP#F RP# DCLK **DCLK** A[20..0] DATA[7..0] DATA[7..0] A[20..0] (2) MSEL nSTATUS OE RY/BY# (5) RY/BY# CONF\_DONE nCS CE# CE# nINIT\_CONF nCONFIG OE# OE# N.C. nCEO DQ[15..0] DQ[15..0] nCE Vcc Vcc (6) WP# **VCCW** GND BYTE# (3) TM1 PORSEL PGM[2..0] TMO **EXCLK**  $\Diamond$ GND C-A0 (3) A0-F C-A1 (3) A1-F C-A15 (3) A15-F C-A16 (3) A16-F

Figure 1. Configuration Example using EPC Device in FPP Mode Note (1)

#### Notes to Figure 1:

- (1) For external flash interface support in EPC8 enhanced configuration device, contact Altera Applications.

- (2) Pin A20 in EPC16 devices, pins A20 and A19 in EPC8 devices, and pins A20, A19, and A18 in EPC4 devices should be left floating. These pins should not be connected to any signal; they are no-connect pins.

- (3) In the 100-pin PQFP package, you must externally connect the following pins: C-A0 to F-A0, C-A1 to F-A1, C-A15 to F-A15, C-A16 to F-A16, and BYTE # to V<sub>CC</sub>. Additionally, you must make the following pin connections in both 100-pin PQFP and 88-pin Ultra FineLine BGA packages: C-RP# to F-RP#, C-WE# to F-WE#, TM1 to V<sub>CC</sub>, TM0 to GND, and WP# to V<sub>CC</sub>.

- (4) For PORSEL, PGM[], and EXCLK pin connections, refer to Enhanced Configuration Devices (EPC4, EPC8, and EPC16) Data Sheet.

- (5) RY/BY# pin is only available for Sharp flash-based EPC8 and EPC16.

- (6) To protect Intel Flash based EPC devices content, you have to isolate the V<sub>CCW</sub> supply from V<sub>CC</sub>.

### Set-Up Time Issue

The set-up time issue described here refers to the revision B silicon of the Altera enhanced configuration devices. The issue described in this errata sheet has now been corrected in the revision C silicon of this device. All revision C devices are fully backward compatible with the revision B devices. As of the date of this errata sheet, the EPC4, EPC8, and EPC16 devices in the 100-pin quad flat pack (QFP) package are shipped with revision C silicon.

The EPC16UC88 device has a special ordering code (EPC16UB88AA) to identify revision C silicon. The EPC16UC88 ordering code is used to deliver revision B silicon at this time. Once the transition from revision B to revision C silicon is complete, the EPC16UC88 ordering code will be used going forward to deliver revision C silicon, and the EPC16UC88AA ordering code will be made obsolete.

For identification purposes, the fourth character of the 11-character date code indicates the die revision. For a revision B component, this character will be a "B", and for a revision C component, this character will be a "C". For more information regarding the device marking, refer to customer advisories 9916 and 9707.

Customers who are using enhanced configuration devices and configuring one or more SRAM-based devices may encounter configuration device failure. This failure may be temperature- or voltage-dependent.

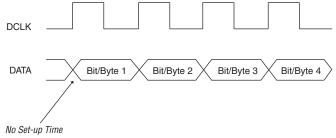

The problem is due to a set-up time violation of the DATA signal. The enhanced configuration device generates the DATA and DCLK signals so that they arrive at the PLD simultaneously.

The PLD requires a set-up time of 10 ns. However, since the DCLK and DATA signals transition simultaneously, the set-up time at the PLD is actually zero. Figure 2 shows the DATA and DCLK signals generated by enhanced configuration devices.

Figure 2. DATA and DCLK Signals Generated by Enhanced Configuration Devices

#### **Design Guidelines**

To achieve a successful configuration, required set-up time must be provided to the DATA signal or signals of SRAM-based devices. Depending on the layout of the board, there may already be sufficient set-up time at the PLD. Measure the DCLK to DATA relationship at the PLD. If the DATA changes prior to the rising edge of the DCLK signal more than the required set-up time (10 ns for all SRAM-based devices), then the board will configure correctly. If the set-up time parameter is not met, then the DATA signal must be delayed so that it changes after the DCLK transition (DATA latches on next rising edge of the clock). A delay of 10 ns is sufficient to provide the required set-up time for the DATA signal or signals. This delay between DCLK and DATA is measured at the PLD.

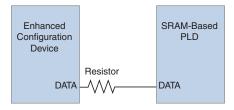

The delay is introduced by adding a resistor to the DATA path from the enhanced configuration devices to the SRAM-based PLDs, as shown in Figure 3.

Figure 3. Adding a Resistor to DATA Path

The delay is created by a resistor-capacitor network. The resistor is added to the circuit and the capacitance is provided by the board trace. The RC combination should be chosen such that the path delay is equal to 10 ns.

A typical combination would use a 100- to  $200-\Omega$  resistor with a trace length of four inches between the DATA pins of the enhanced configuration device and the PLD.

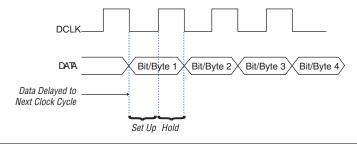

After inserting the delay, the DATA transition would shift to the right so that the first bit or byte of data would be latched on the second rising edge of DCLK, as shown in Figure 4. This shift meets the required set-up time for the DATA signal.

Figure 4. DATA Latches on Second Rising Edge of DCLK after DATA Path Delay

This technique enables existing enhanced configuration devices to configure PLDs. Future updated versions of enhanced configuration devices will be modified so that the DCLK and DATA signals arrive at the PLD to meet the required set-up time.

A board that is laid out with an in-line resistor will work with updated versions of enhanced configuration devices, but the maximum frequency for configuration would be limited to 33 MHz.

## Contact Information

For more information, go to Altera's mySupport website at www.altera.com/mysupport and click Create New Service Request. Choose the Product Related Request form.

#### **Revision History**

Table 1 shows the revision history for this errata sheet.

| Table 1. Enhanced Configuration Devices v1.3 Errata Sheet Revision History |               |                                                                                                                                    |

|----------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| Version                                                                    | Date          | Errata Summary                                                                                                                     |

| 1.3                                                                        | July 2008     | <ul><li>Added Figure 1.</li><li>Updated Figure 1.</li></ul>                                                                        |

| 1.2                                                                        | October 2007  | <ul><li>Added section on "Intel-Flash-Based EPC Device Protection".</li><li>Updated section on "Set-Up Time Issue".</li></ul>      |

| 1.1                                                                        | December 2003 | Addressed known issues and includes methods to work around the<br>issues for enhanced configuration devices EPC4, EPC8, and EPC16. |

101 Innovation Drive San Jose, CA 95134 www.altera.com Technical Support: www.altera.com/support/ Literature Services: literature@altera.com Copyright © 2008 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks or Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.