## 4. Reset Control and Power Down in **Stratix IV Devices**

SIV52004-4.4

Stratix<sup>®</sup> IV devices offer multiple reset signals to control the transceiver channels and clock multiplier unit (CMU) phase-locked loops (PLLs) independently. The ALTGX Transceiver MegaWizard<sup>TM</sup> Plug-In Manager provides individual reset signals for each channel instantiated in your design. It also provides one power-down signal for each transceiver block.

This chapter includes the following sections:

- "User Reset and Power-Down Signals" on page 4–2

- "Transceiver Reset Sequences" on page 4-4

- "PMA Direct Drive Mode Reset Sequences" on page 4-24

- "Dynamic Reconfiguration Reset Sequences" on page 4–36

- "Power Down" on page 4-38

- "Simulation Requirements" on page 4-39

- "Reference Information" on page 4–39

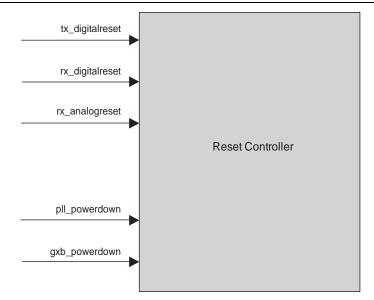

Figure 4–1 shows the reset control and power-down block for a Stratix IV device.

Figure 4-1. Reset Control and Power-Down Block

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **User Reset and Power-Down Signals**

Each transceiver channel in the Stratix IV device has individual reset signals to reset its physical coding sublayer (PCS) and physical medium attachment (PMA) blocks. Each CMU PLL in the transceiver block has a dedicated reset signal. The transceiver block also has a power-down signal that affects all the channels and CMU PLLs in the transceiver block.

All reset and power-down signals are asynchronous.

Table 4–1 lists the reset signals available for each transceiver channel.

Table 4-1. Transceiver Channel Reset Signals

| Signal              | ALTGX MegaWizard Plug-In<br>Manager Configurations | Description                                                                                                         |  |

|---------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| tx digitalreset (1) | Transmitter Only  Description of Transmitter       | Provides asynchronous reset to all digital logic in the transmitter PCS, including the XAUI transmit state machine. |  |

|                     | Receiver and Transmitter                           | The minimum pulse width for this signal is two parallel clock cycles.                                               |  |

|                     |                                                    | Resets all digital logic in the receiver PCS, including:                                                            |  |

|                     | Receiver Only     Receiver and Transmitter         | <ul> <li>XAUI receiver state machines</li> </ul>                                                                    |  |

|                     |                                                    | GIGE receiver state machines                                                                                        |  |

| rx_digitalreset (1) |                                                    | <ul> <li>XAUI channel alignment state machine</li> </ul>                                                            |  |

|                     | neceiver and transmitter                           | <ul><li>BIST-PRBS verifier</li><li>BIST-incremental verifier</li></ul>                                              |  |

|                     |                                                    |                                                                                                                     |  |

|                     |                                                    | The minimum pulse width for this signal is two parallel clock cycles.                                               |  |

|                     | Receiver Only                                      | Resets the receiver CDR present in the receiver channel.                                                            |  |

| rx_analogreset      | Receiver and Transmitter                           | The minimum pulse width is two parallel clock cycles.                                                               |  |

#### Note to Table 4-1:

(1) Assert this signal until the clocks coming out of the transmitter PLL and receiver CDR are stabilized. Stable parallel clocks are essential for proper operation of the transmitter and receiver phase-compensation FIFOs in the PCS.

Table 4–2 lists the power-down signals available for each CMU PLL transceiver block.

Table 4-2. Transceiver Block Power-Down Signals

| Signal                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pll_powerdown <sup>(1)</sup>   | Each transceiver block has two CMU PLLs. Each CMU PLL has this dedicated power-down signal. This signal powers down the CMU PLLs that provide high-speed serial and low-speed parallel clocks to the transceiver channels.                                                                                                                                                                                                                                                                              |

|                                | Powers down the entire transceiver block. When this signal is asserted, it powers down:                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                | the PCS and PMA in all the transceiver channels                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| gxb_powerdown <sup>(1)</sup>   | the CMU PLLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | This signal operates independently from the other reset signals and is common to the transceiver block.                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                | A status signal. Indicates the status of the transmitter PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| pll_locked                     | ■ A high level—the transmitter PLL is locked to the incoming reference clock frequency. When pll_locked is low, tx_digitalreset must always be asserted. To de-assert tx_digitalreset, follow the initialization reset sequence for your specific mode.                                                                                                                                                                                                                                                 |

| rx_pll_locked A status signal. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| rx_pii_iockeu                  | A high level—the receiver CDR is locked to the incoming reference clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                | A status signal. Indicates the status of the receiver CDR lock mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                | ■ A high level—the receiver is in lock-to-data (LTD) mode.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rx_freqlocked                  | ■ A low level—the receiver CDR is in lock-to-reference (LTR) mode. In automatic lock mode, when rx_freqlocked is low, rx_digitalreset must always be asserted. To de-assert rx_digitalreset, follow the initialization reset sequence for your specific mode.                                                                                                                                                                                                                                           |

| busy                           | A status signal. An output from the ALTGX_RECONFIG block indicates the status of the dynamic reconfiguration controller. This signal remains low for the first reconfig_clk clock cycle after power up. It then is asserted from the second reconfig_clk clock cycle. Assertion on this signal indicates that the offset cancellation process is being executed on the receiver buffer as well as the receiver CDR. When this signal is de-asserted, it indicates that offset cancellation is complete. |

#### Note to Table 4-2:

(1) The refclk (refclk0 or refclk1) buffer is not powered down by this signal.

For more information about offset cancellation, refer to the *Dynamic Reconfiguration in* Stratix IV Devices chapter.

If none of the channels is instantiated in a transceiver block, the Quartus<sup>®</sup> II software automatically powers down the entire transceiver block.

## **Blocks Affected by the Reset and Power-Down Signals**

Table 4–3 lists the blocks that are affected by specific reset and power-down signals.

Table 4-3. Blocks Affected by Reset and Power-Down Signals (Part 1 of 2)

| Transceiver Block                      | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_powerdown | gxb_powerdown |

|----------------------------------------|-----------------|----------------|-----------------|---------------|---------------|

| CMU PLLs                               | _               | _              | _               | Y             | Υ             |

| Transmitter Phase<br>Compensation FIFO | _               | _              | Υ               | _             | Υ             |

| Transceiver Block                        | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_powerdown | gxb_powerdown |

|------------------------------------------|-----------------|----------------|-----------------|---------------|---------------|

| Byte Serializer                          | _               | _              | Υ               | _             | Υ             |

| 8B/10B Encoder                           | _               | _              | Y               | _             | Υ             |

| Serializer                               | _               | _              | Y               | _             | Υ             |

| Transmitter Buffer                       | _               | _              | _               | _             | Υ             |

| Transmitter XAUI State<br>Machine        | _               | _              | Y               | _             | Υ             |

| Receiver Buffer                          | _               | _              | _               | _             | Υ             |

| Receiver CDR                             | _               | Υ              | _               | _             | Υ             |

| Receiver Deserializer                    | _               | _              | _               | _             | Υ             |

| Receiver Word Aligner                    | Υ               | _              | _               | _             | Υ             |

| Receiver Deskew FIFO                     | Y               | _              | _               | _             | Υ             |

| Receiver Clock Rate<br>Compensation FIFO | Υ               | _              | _               | _             | Υ             |

| Receiver 8B/10B<br>Decoder               | Υ               | _              | _               | _             | Υ             |

| Receiver Byte<br>Deserializer            | Υ               | _              | _               | _             | Υ             |

| Receiver Byte Ordering                   | Y               | _              | _               | _             | Υ             |

| Receiver Phase<br>Compensation FIFO      | Y               | _              | _               | _             | Υ             |

| Receiver XAUI State<br>Machine           | Υ               | _              | _               | _             | Υ             |

| BIST Verifiers                           | Υ               | _              | _               | _             | Υ             |

Table 4-3. Blocks Affected by Reset and Power-Down Signals (Part 2 of 2)

## **Transceiver Reset Sequences**

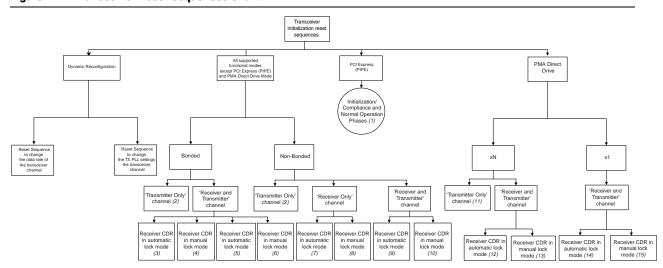

You can configure transceiver channels in Stratix IV devices in various configurations. In all functional modes except XAUI functional mode, transceiver channels can be either bonded or non-bonded. In XAUI functional mode, transceiver channels must be bonded. In PCI Express<sup>®</sup> (PCIe) functional mode, transceiver channels can be either bonded or non-bonded and need to follow a specific reset sequence.

The two categories of reset sequences for Stratix IV devices described in this chapter are:

- "All Supported Functional Modes Except PCIe Functional Mode" on page 4–6—describes the reset sequences in bonded and non-bonded configurations.

- "PCIe Functional Mode" on page 4–22—describes the reset sequence for the initialization/compliance phase and the normal operation phase in PCIe functional modes.

The busy signal remains low for the first reconfig\_clk clock cycle. It then is asserted from the second reconfig\_clk clock cycle. Subsequent de-assertion of the busy signal indicates the completion of the offset cancellation process. This busy signal is required in transceiver reset sequences except for **Transmitter Only** channel configurations. For more information, refer to the reset sequences shown in Figure 4–2 and the associated references listed in the figure notes.

Altera strongly recommends adhering to these reset sequences for proper operation of the Stratix IV transceiver.

Figure 4–2 shows the transceiver reset sequences for Stratix IV devices.

Figure 4-2. Transceiver Reset Sequences Chart

#### Notes to Figure 4-2:

- (1) Refer to the Timing Diagram in Figure 4-12.

- (2) Refer to the Timing Diagram in Figure 4-3.

- (3) Refer to the Timing Diagram in Figure 4-4.

- (4) Refer to the Timing Diagram in Figure 4-5.

- (5) Refer to the Timing Diagram in Figure 4-6.

- (6) Refer to the Timing Diagram in Figure 4–7.

- (7) Refer to the Timing Diagram in Figure 4–8.

- (8) Refer to the Timing Diagram in Figure 4–9.

- (9) Refer to the Timing Diagram in Figure 4–10.

- (10) Refer to the Timing Diagram in Figure 4–11.

- (11) Refer to the Timing Diagram in Figure 4–13.

- (12) Refer to the Timing Diagram in Figure 4–16.

- (13) Refer to the Timing Diagram in Figure 4–17.

- (14) Refer to the Timing Diagram in Figure 4-18.

- (15) Refer to the Timing Diagram in Figure 4-19.

## **All Supported Functional Modes Except PCIe Functional Mode**

This section describes reset sequences for transceiver channels in bonded and non-bonded configurations. Timing diagrams of some typical configurations are shown to facilitate proper reset sequence implementation. In these functional modes, you can set the receiver CDR either in automatic lock or manual lock mode.

In manual lock mode, the receiver CDR locks to the reference clock (lock-to-reference) or the incoming serial data (lock-to-data), depending on the logic levels on the rx\_locktorefclk and rx\_locktodata signals. With the receiver CDR in manual lock mode, you can either configure the transceiver channels in the Stratix IV device in a non-bonded configuration or a bonded configuration. In a bonded configuration, for example in XAUI mode, four channels are bonded together.

Table 4–4 lists the lock-to-reference (LTR) and lock-to-data (LTD) controller lock modes for the rx\_locktorefclk and rx\_locktodata signals.

Table 4–4. Lock-To-Reference and Lock-To-Data Modes

| rx_locktorefclk | rx_locktodata | LTR/LTD Controller Lock Mode |

|-----------------|---------------|------------------------------|

| 1               | 0             | Manual, LTR Mode             |

| _               | 1             | Manual, LTD Mode             |

| 0               | 0             | Automatic Lock Mode          |

#### **Bonded Channel Configuration**

In a bonded channel configuration, you can reset all the bonded channels simultaneously. Examples of bonded channel configurations are XAUI, PCIe, and Basic ×4 functional modes. In Basic ×4 functional mode, you can bond **Transmitter Only** channels together.

In XAUI mode, the receiver and transmitter channels are bonded. Each of the receiver channels in this mode has its own output status signals, rx\_pll\_locked and rx\_freqlocked. You must consider the timing of these signals in the reset sequence.

Table 4–5 lists the reset and power-down sequences for bonded configurations under the stated functional modes.

Table 4–5. Reset and Power-Down Sequences for Bonded Channel Configurations

| Channel Set Up           | Receiver CDR Mode                                | Refer to                                                                               |

|--------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|

| Transmitter Only         | Basic ×4                                         | "Transmitter Only Channel" on page 4–7                                                 |

| Receiver and Transmitter | Automatic lock mode for XAUI functional mode     | "Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode" on page 4–8     |

| Receiver and Transmitter | Manual lock mode for XAUI functional mode        | "Receiver and Transmitter Channel—Receiver<br>CDR in Manual Lock Mode" on page 4–10    |

| Receiver and Transmitter | Automatic lock mode for Basic ×8 functional mode | "Receiver and Transmitter Channel—Receiver<br>CDR in Automatic Lock Mode" on page 4–12 |

| Receiver and Transmitter | Manual lock mode for Basic ×8 functional mode    | "Receiver and Transmitter Channel—Receiver<br>CDR in Manual Lock Mode" on page 4–14    |

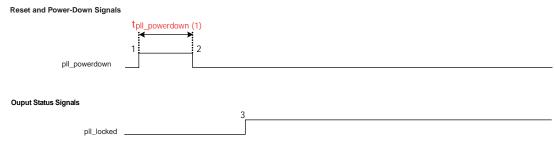

#### **Transmitter Only Channel**

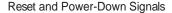

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager in Basic ×4 functional mode, use the reset sequence shown in Figure 4–3.

Figure 4-3. Sample Reset Sequence for Four Transmitter Only Channels

#### Note to Figure 4-3:

(1) For  $t_{\text{pll powerdown}}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–3, for the **Transmitter Only** channel configuration, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- Keep the tx\_digitalreset signal asserted during this time period. After you

de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the

transmitter input reference clock.

- 3. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert the tx\_digitalreset signal (marker 4). At this point, the transmitter is ready for transmitting data.

#### Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

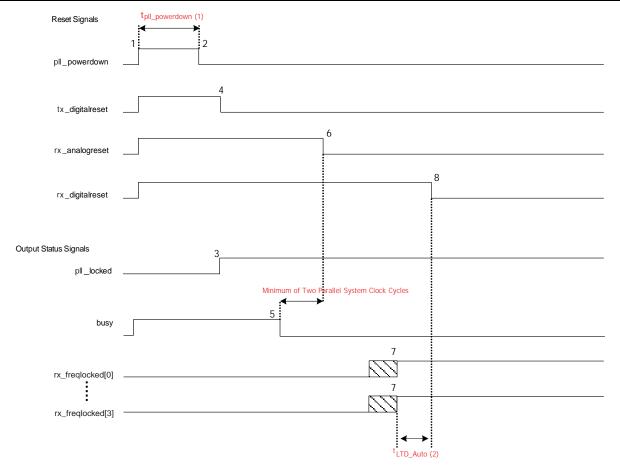

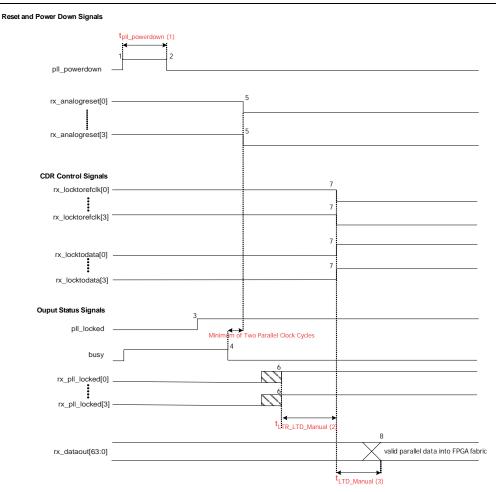

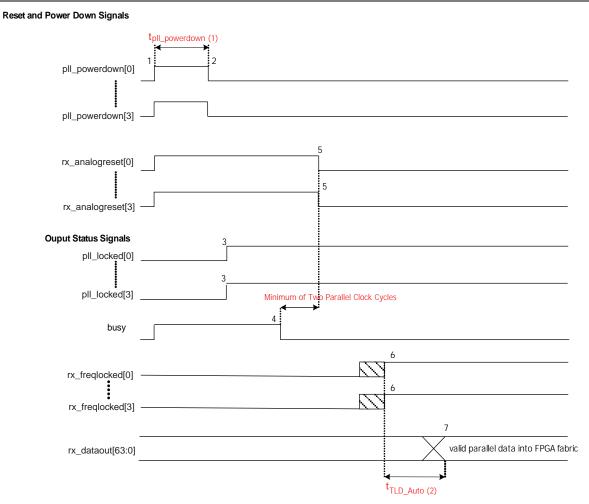

This configuration contains both a transmitter and receiver channel. For XAUI functional mode, with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 4–4.

Figure 4–4. Sample Reset Sequence for Four Receiver and Transmitter Channels—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 4-4:

- (1) For  $t_{pll\_powerdown}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–4, for the receiver CDR in automatic lock mode configuration, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. After the transmitter PLL locks, as indicated by the pll\_locked signal going high, de-assert the tx\_digitalreset signal. At this point, the transmitter is ready for data traffic.

- 4. For the receiver operation, after de-assertion of busy signal, wait for a minimum of two parallel clock cycles to de-assert the rx\_analogreset signal. After rx\_analogreset is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock.

- 5. Wait for the rx\_freqlocked signal from each channel to go high. The rx\_freqlocked signal of each channel may go high at different times (indicated by the slashed pattern at marker 7).

- 6. In a bonded channel group, when the rx\_freqlocked signals of all the channels has gone high, from that point onwards, wait for at least t<sub>LTD\_Auto</sub> for the receiver parallel clock to be stable, then de-assert the rx\_digitalreset signal (marker 8). At this point, all the receivers are ready for data traffic. Note that rx\_digitalreset must not be released if there is no data present at the receiver pins to avoid overflow/underflow of the phase compensation FIFOs.

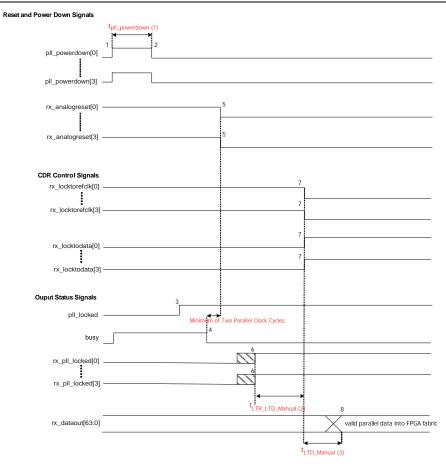

#### Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode

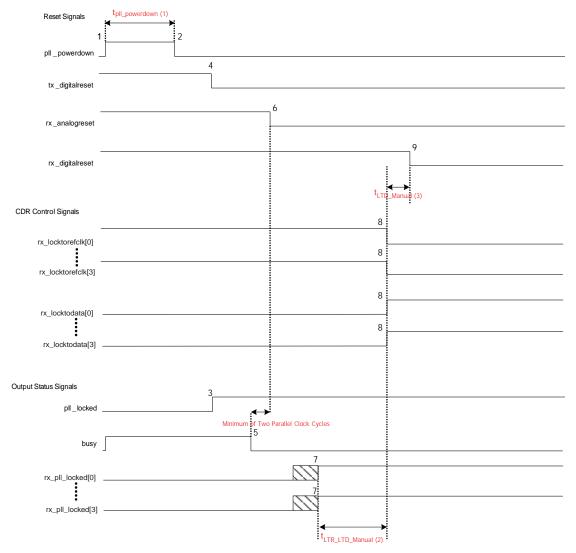

This configuration contains both a transmitter and receiver channel. For XAUI functional mode, with the receiver CDR in manual lock mode, use the reset sequence shown in Figure 4–5.

Figure 4-5. Sample Reset Sequence for Four Receiver and Transmitter Channels—Receiver CDR in Manual Lock Mode

#### Notes to Figure 4-5:

- $(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.}$

- $(2) \quad \text{For } t_{LTR\_LTD\_Manual} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.} \\$

- (3) For  $t_{LTD\ Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–5, for the receiver CDR in manual lock mode configuration, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, rx\_digitalreset, and rx\_locktorefclk signals asserted and the rx\_locktodata signal de-asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. After the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert the tx\_digitalreset signal (marker 4). For the receiver operation, after de-assertion of the busy signal, wait for a minimum of **two parallel clock cycles** to de-assert the rx\_analogreset signal. After the rx\_analogreset signal is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock because rx\_locktorefclk is asserted.

- 4. Wait for the rx\_pll\_locked signal from each channel to go high. The rx\_pll\_locked signal of each channel may go high at different times with respect to each other (indicated by the slashed pattern at marker 7).

- 5. In a bonded channel group, when the rx\_pll\_locked signal of all the channels have gone high, from that point onwards, wait for at least tLTR\_LTD\_Manual, then de-assert rx\_locktorefclk and assert rx\_locktodata (marker 8). At this point, the receiver CDR of all the channels enters into lock-to-data mode and starts locking to the received data.

- 6. After asserting the  $rx\_locktodata$  signal, wait for at least  $t_{LTD\_Manual}$  before de-asserting  $rx\_digitalreset$  (the time between markers 8 and 9).

#### Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

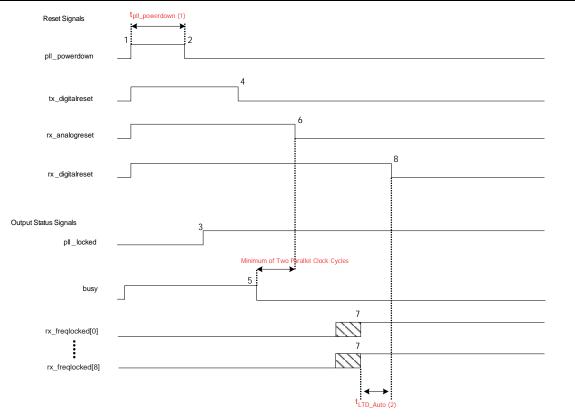

This configuration contains both a transmitter and a receiver channel. For Basic  $\times 8$  functional mode, with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 4–6.

Figure 4–6. Sample Reset Sequence for Eight Receiver and Transmitter Channels—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 4-6:

- $(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.} \\$

- (2) For  $t_{LTD\_Auto}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–6, for the receiver CDR in automatic lock mode, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. After the transmitter PLL locks, as indicated by the pll\_locked signal going high, de-assert the tx\_digitalreset signal. At this point, the transmitter is ready for data traffic.

- 4. For the receiver operation, after de-assertion of the busy signal, wait for a minimum of **two parallel clock cycles** to de-assert the rx\_analogreset signal. After rx\_analogreset is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock.

- 5. Wait for the rx\_freqlocked signal from each channel to go high. The rx\_freqlocked signal of each channel may go high at different times (indicated by the slashed pattern at marker 7).

- 6. In a bonded channel group, when the rx\_freqlocked signals of all the channels have gone high, from that point onwards, wait for at least t<sub>LTD\_Auto</sub> for the receiver parallel clock to stabilize, then de-assert the rx\_digitalreset signal (marker 8). At this point, all the receivers are ready for data traffic. Note that rx\_digitalreset must not be released if there is no data present at the receiver pins to avoid overflow/underflow of the phase compensation FIFOs.

#### Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode

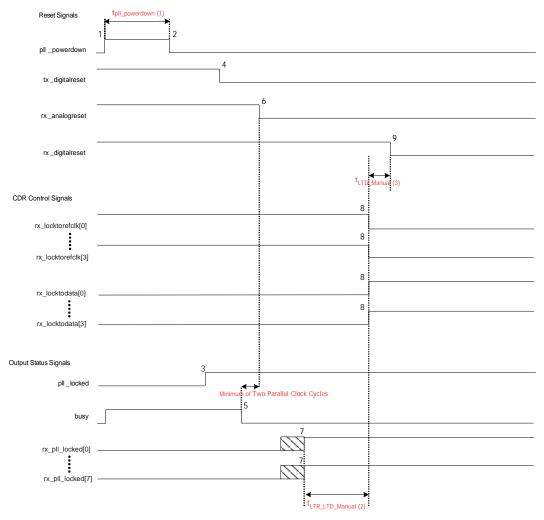

This configuration contains both a transmitter and receiver channel. For Basic  $\times 8$  functional mode, with the receiver CDR in manual lock mode, use the reset sequence shown in Figure 4–7.

Figure 4-7. Sample Reset Sequence for Eight Receiver and Transmitter Channels—Receiver CDR in Manual Lock Mode

#### Notes to Figure 4-7:

- (1) For  $t_{pll\_powerdown}$  duration, refer to the *DC* and Switching Characteristics for Stratix IV Devices chapter.

- (2) For  $t_{LTR\_LTD\_Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

- (3) For  $t_{LTD\_Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–7, for the receiver CDR in manual lock mode, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, rx\_digitalreset, and rx\_locktorefclk signals asserted and the rx\_locktodata signal de-asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. After the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert the tx\_digitalreset signal (marker 4). For the receiver operation, after de-assertion of the busy signal, wait for a minimum of two parallel clock cycles to de-assert the rx\_analogreset signal. After the rx\_analogreset signal is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock because rx\_locktorefclk is asserted.

- 4. Wait for the rx\_pll\_locked signal from each channel to go high. The rx\_pll\_locked signal of each channel may go high at different times with respect to each other (indicated by the slashed pattern at marker 7).

- 5. In a bonded channel group, when the rx\_pll\_locked signal of all the channels has gone high, from that point onwards, wait for at least t<sub>LTR\_LTD\_Manual</sub>, then de-assert rx\_locktorefclk and assert rx\_locktodata (marker 8). At this point, the receiver CDR of all the channels enters into lock-to-data mode and starts locking to the received data.

- 6. De-assert rx\_digitalreset at least t<sub>LTD\_Manual</sub> (the time between markers 8 and 9) after asserting the rx\_locktodata signal.

#### **Non-Bonded Channel Configuration**

In non-bonded channels, each channel in the ALTGX MegaWizard Plug-In Manager instance contains its own tx\_digitalreset, rx\_analogreset, rx\_digitalreset, rx\_pll\_locked, and rx\_freqlocked signals.

You can reset each channel independently. For example, if there are four non-bonded channels, the ALTGX MegaWizard Plug-In Manager provides four each of the following signals: tx\_digitalreset, rx\_analogreset, rx\_digitalreset, rx\_pll\_locked, and rx\_freqlocked.

Table 4–6 lists the reset and power-down sequences for one channel in a non-bonded configuration under the stated functional modes.

Table 4–6. Reset and Power-Down Sequences for Bonded Channel Configurations (Part 1 of 2)

| Channel Set Up   | Receiver CDR Mode   | Refer to                                                                 |

|------------------|---------------------|--------------------------------------------------------------------------|

| Transmitter Only | Basic ×4            | "Transmitter Only Channel" on page 4–16                                  |

| Receiver Only    | Automatic lock mode | "Receiver Only Channel—Receiver CDR in Automatic Lock Mode" on page 4–16 |

| Receiver Only    | Manual lock mode    | "Receiver Only Channel—Receiver CDR in Manual Lock<br>Mode" on page 4–17 |

Table 4-6. Reset and Power-Down Sequences for Bonded Channel Configurations (Part 2 of 2)

| Channel Set Up           | Receiver CDR Mode   | Refer to                                                                               |

|--------------------------|---------------------|----------------------------------------------------------------------------------------|

| Receiver and Transmitter | Automatic lock mode | "Receiver and Transmitter Channel—Receiver CDR in<br>Automatic Lock Mode" on page 4–18 |

| Receiver and Transmitter | Manual lock mode    | "Receiver and Transmitter Channel—Receiver CDR in<br>Manual Lock Mode" on page 4–20    |

Follow the same reset sequence for all the other channels in the non-bonded configuration.

#### **Transmitter Only Channel**

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager, use the same reset sequence shown in Figure 4–3 on page 4–7.

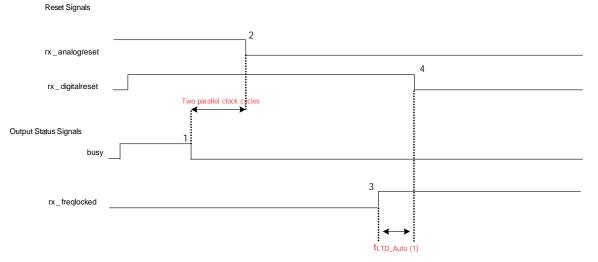

#### Receiver Only Channel—Receiver CDR in Automatic Lock Mode

This configuration contains only a receiver channel. If you create a **Receiver Only** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 4–8.

Figure 4-8. Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Automatic Lock Mode

#### Note to Figure 4-8:

(1) For  $t_{LTD\_Auto}$  duration, refer to the *DC* and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–8, for the receiver in CDR automatic lock mode, follow these reset steps:

- 1. After power up, wait for the busy signal to be de-asserted.

- 2. De-assert the rx\_analogreset signal.

- 3. Keep the rx\_digitalreset signal asserted during this time period. After you de-assert the rx\_analogreset signal, the receiver CDR starts locking to the receiver input reference clock.

- 4. Wait for the rx\_freqlocked signal to go high.

- 5. When rx\_freqlocked goes high (marker 3), from that point onwards, wait for at least t<sub>LTD\_Auto</sub>, then de-assert the rx\_digitalreset signal (marker 4). At this point, the receiver is ready to receive data.

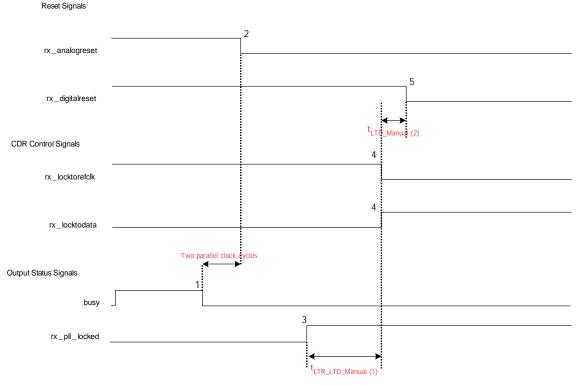

#### Receiver Only Channel—Receiver CDR in Manual Lock Mode

This configuration contains only a receiver channel. If you create a **Receiver Only** instance in the ALTGX MegaWizard Plug-In Manager with receiver CDR in manual lock mode, use the reset sequence shown in Figure 4–9.

Figure 4-9. Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Manual Lock Mode

#### Notes to Figure 4-9:

- (1) For t<sub>LTR LTD</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

- (2) For t<sub>LTD Manual</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

As shown in Figure 4–9, for the receiver CDR in manual lock mode, follow these reset steps:

- 1. After power up, wait for the busy signal to be asserted.

- 2. Keep the rx\_digitalreset and rx\_locktorefclk signals asserted and the rx\_locktodata signal de-asserted during this time period.

- 3. After de-assertion of the busy signal, de-assert the rx\_analogreset signal. The receiver CDR then starts locking to the receiver input reference clock because the rx\_locktorefclk signal is asserted.

- 4. Wait for at least t<sub>LTR\_LTD\_Manual</sub> time (the time between markers 3 and 4) after the rx\_pll\_locked signal goes high and then de-assert the rx\_locktorefclk signal. At the same time, assert the rx\_locktodata signal (marker 4). At this point, the receiver CDR enters lock-to-data mode and the receiver PLL starts locking to the received data.

- De-assert rx\_digitalreset at least t<sub>LTD\_Manual</sub> (the time between markers 4 and

after asserting the rx\_locktodata signal.

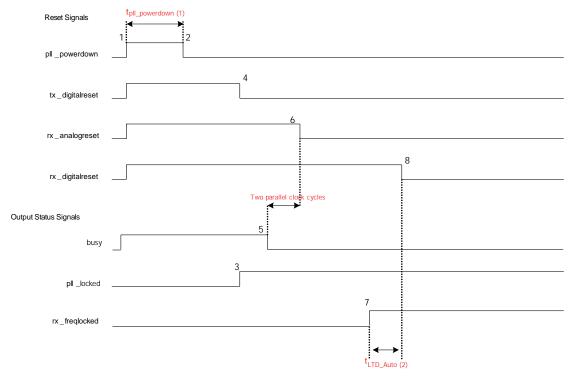

#### Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

This configuration contains both a transmitter and a receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 4–10.

Figure 4-10. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 4-10:

- (1) For t<sub>pll powerdown</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

- (2) For t<sub>LTD Auto</sub> duration, refer to the *DC* and *Switching Characteristics for Stratix IV Devices* chapter.

As shown in Figure 4–10, for the receiver in CDR automatic lock mode, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. After the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert tx\_digitalreset. For receiver operation, wait for the busy signal to be de-asserted, after which rx\_analogreset is de-asserted. After you de-assert rx\_analogreset, the receiver CDR starts locking to the receiver input reference clock.

- 4. Wait for the rx\_freqlocked signal to go high (marker 7).

- 5. After the rx\_freqlocked signal goes high, wait for at least t<sub>LTD\_Auto</sub>, then de-assert the rx\_digitalreset signal (marker 8). Note that rx\_digitalreset must not be released if there is no data present at the receiver pins to avoid overflow/underflow of the phase compensation FIFOs. At this point, the transmitter and receiver are ready for data traffic.

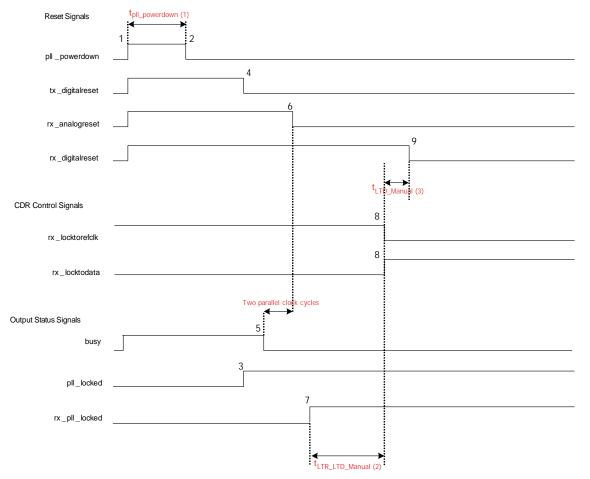

#### Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode

This configuration contains both a transmitter and receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in manual lock mode, use the reset sequence shown in Figure 4–11.

Figure 4-11. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode

#### Notes to Figure 4-11:

- (1) For  $t_{\text{pll\_powerdown}}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

- (2) For  $t_{LTR\_LTD\_Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

- (3) For t<sub>LTD Manual</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

As shown in Figure 4–11, perform the following reset procedure for the receiver in manual lock mode:

- 1. After power up, assert pll\_powerdown for a minimum period of t<sub>pll\_powerdown</sub> (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, rx\_digitalreset, and rx\_locktorefclk signals asserted and the rx\_locktodata signal de-asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. After the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert tx\_digitalreset. For receiver operation, wait for the busy signal to be de-asserted. At this point rx\_analogreset is de-asserted. When rx\_analogreset is de-asserted, the receiver CDR starts locking to the receiver input reference clock because rx\_locktorefclk is asserted.

- 4. Wait for at least t<sub>LTR\_LTD\_Manual</sub> (the time between markers 7 and 8) after the rx\_pll\_locked signal goes high, then de-assert the rx\_locktorefclk signal. At the same time, assert the rx\_locktodata signal (marker 8). At this point, the receiver CDR enters lock-to-data mode and the receiver CDR starts locking to the received data.

- 5. De-assert rx\_digitalreset at least  $t_{LTD\_Manual}$  (the time between markers 8 and 9) after asserting the rx\_locktodata signal.

### **PCIe Functional Mode**

You can configure PCIe functional mode with or without the receiver clock rate compensation FIFO in the Stratix IV device. The reset sequence remains the same whether or not you use the receiver clock rate compensation FIFO.

#### **PCIe Reset Sequence**

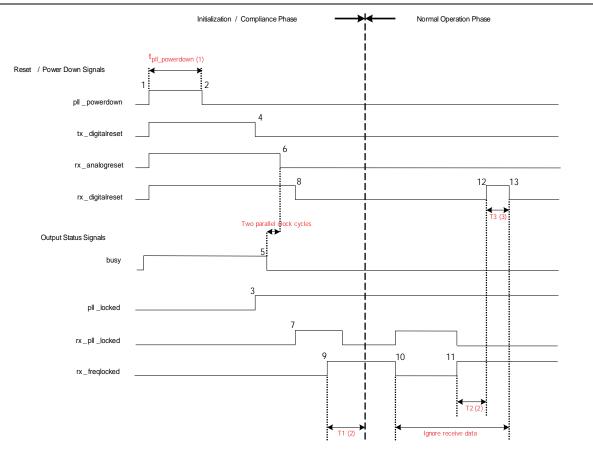

The PCIe protocol consists of an initialization/compliance phase and a normal operation phase. The reset sequences for these two phases are described based on the timing diagram in Figure 4–12.

Figure 4-12. Reset Sequence of PCIe Functional Mode

#### Notes to Figure 4-12:

- $(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.} \\$

- (2) The minimum T1 and T2 period is 4  $\mu$ s.

- (3) The minimum T3 period is two parallel clock cycles.

#### **PCIe Initialization/Compliance Phase**

After the device is powered up, a PCIe-compliant device goes through the compliance phase during initialization. In this phase, the PCIe protocol requires the system to be operating at the Gen 1 data rate. The rx\_digitalreset signal must be de-asserted during this compliance phase to achieve transitions on the pipephydonestatus signal, as expected by the link layer. The rx\_digitalreset signal is de-asserted based on the assertion of the rx\_freqlocked signal.

During the initialization/compliance phase, do not use the rx\_freqlocked signal to trigger a de-assertion of the rx\_digitalreset signal. Instead, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of  $t_{pll_powerdown}$  (the time between markers 1 and 2). Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 2. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert tx\_digitalreset. For a receiver operation, wait for the busy signal to be de-asserted. rx\_analogreset is then de-asserted. After rx\_analogreset is de-asserted, the receiver CDR starts locking to the receiver input reference clock.

- 3. When the receiver CDR locks to the input reference clock, as indicated by the rx\_pll\_locked signal going high at marker 7 in Figure 4–12, de-assert the rx\_digitalreset signal (marker 8). After de-asserting rx\_digitalreset, the pipephydonestatus signal transitions from the transceiver channel to indicate the status to the link layer. Depending on its status, pipephydonestatus helps with the continuation of the compliance phase. After successful completion of this phase, the device enters into the normal operation phase.

#### **PCIe Normal Phase**

For the normal PCIe phase, follow these steps:

- 1. After completion of the Initialization/Compliance phase, during the normal operation phase at the Gen 1 data rate, when the rx\_freqlocked signal is de-asserted (marker 10 in Figure 4–12), wait for the rx\_pll\_locked signal assertion signifying the lock-to-reference clock.

- Wait for the rx\_freqlocked signal to go high again. In this phase, the received data

is valid (not electrical idle) and the receiver CDR locks to the incoming data.

Proceed with the reset sequence after assertion of the rx\_freqlocked signal.

- 3. After the rx\_freqlocked signal goes high, wait for at least 4 µs before asserting rx\_digitalreset (marker 12 in Figure 4–12) for two parallel receive clock cycles so that the receiver phase compensation FIFO is initialized.

- 4. During normal operation, after you speed-negotiate to the Gen 2 data rate, asserting the rx\_digitalreset signal causes the PCIe rate switch circuitry to switch the transceiver to the Gen 1 data rate.

- Data from the transceiver block is not valid from the time the rx\_freqlocked signal goes low (marker 10 in Figure 4–12) to the time rx\_digitalreset is de-asserted (marker 13 in Figure 4–12). The PLD logic ignores the data during this period (between markers 10 and 13 in Figure 4–12).

You can configure the Stratix IV device in ×1, ×4, and ×8 PCIe configurations. The reset sequence described in "PCIe Reset Sequence" on page 4–22 applies to all these multi-lane configurations.

## **PMA Direct Drive Mode Reset Sequences**

Stratix IV devices provide a PMA Direct mode in which all PCS blocks, including the phase compensation FIFOs, are bypassed in both the transmitter and receiver channel data paths. In this mode, the PMA block in the transmitter and receiver channels directly interface with the FPGA fabric.

In PMA Direct drive mode, you can configure the transceiver channels as a single channel or in bonded configurations. Basic single- and double-width functional modes support bonding of PMA functional blocks across all transceiver channels on the same side of the device.

The tx\_digitalreset and rx\_digitalreset signals are not available because there are no PCS blocks available in this mode.

Table 4–7 lists the reset and power-down sequences for PMA Direct drive ×N functional mode.

Table 4-7. Reset and Power-Down Sequences for PMA Direct Drive ×N Configurations

| Channel Set Up                   | Functional Mode                                             | Refer to                                                                                          |

|----------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Transmitter Only with no PLL_L/R | Basic (PMA Direct) drive ×4                                 | "Transmitter Only Channel with No PLL_L/R" on page 4–25                                           |

| Transmitter Only with a PLL_L/R  | Manual lock mode                                            | "Transmitter Only Channel with a PLL_L/R" on page 4–26                                            |

| Receiver and Transmitter         | Automatic lock mode for Basic<br>(PMA Direct) drive ×N mode | "Receiver and Transmitter Channel Set-up—<br>Receiver CDR in Automatic Lock Mode" on<br>page 4–28 |

| Receiver and Transmitter         | Manual lock mode for Basic<br>(PMA Direct) drive ×N mode    | "Receiver and Transmitter Channel Set-up—<br>Receiver CDR in Manual Lock Mode" on<br>page 4–30    |

## **Basic (PMA Direct) Drive ×N Mode**

When bonding ×N channels in a Basic (PMA Direct) drive mode configuration, you can reset all bonded channels simultaneously.

#### Transmitter Only Channel with No PLL\_L/R

Figure 4–13 shows an example reset sequence timing diagram of four **Transmitter Only** channels in Basic (PMA Direct) drive ×4 functional mode with no PLL\_L/R.

Figure 4-13. Reset Sequence Timing in Basic (PMA Direct) Drive ×4 Mode

#### Note to Figure 4-13:

(1) For  $t_{pll\_powerdown}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–13, for the **Transmitter Only** channel in Basic (PMA Direct) drive functional ×4 mode with no PLL\_L/R, follow these reset steps:

- 1. After power up, assert  $pll_powerdown$  for a minimum of  $t_{pll_powerdown}$  (the time between markers 1 and 2).

- 2. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), the transmitter is ready to accept parallel data from the FPGA fabric and subsequently transmitting serial data reliably.

#### Transmitter Only Channel with a PLL\_L/R

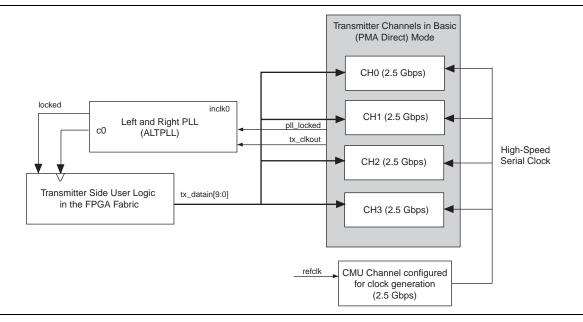

The Basic (PMA Direct) mode configuration that requires a PLL\_L/R is one where each channel in PMA-Direct mode is identical. Figure 4–14 shows a simple set up of identical channels.

Figure 4-14. Identical Channels

Identical channels have the following same configuration:

- Same effective data rate

- Same transmitter local clock divider settings in each channel

- Same FPGA fabric-to-transceiver interface data path width

- The transmitter channels must receive the high-speed clock from the same PLL (either CMU PLL or ATX PLL).

Figure 4–15 shows an example reset sequence timing diagram of four **Transmitter Only** channels in Basic (PMA Direct) Drive x4 functional mode with a PLL\_L/R.

As shown in Figure 4–15, for the **Transmitter Only** channel in Basic (PMA Direct) Drive functional mode with a PLL\_L/R configuration, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum of t<sub>pll\_powerdown</sub> (the time between markers 1 and 2).

- 2. After the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), wait for the locked signal to be asserted. The locked signal is an output of the PLL\_L/R.

3. After the PLL\_L/R locks, as indicated by the locked signal going high (marker 4), the transmitter is ready to accept parallel data from the FPGA fabric and subsequently transmitting serial data reliably.

Figure 4–15. Reset Sequence Timing Diagram of Four Transmitter-Only Channels in Basic (PMA Direct) Drive ×4 Functional Mode

Reset and Power-Down Signals

pll\_powerdown (1)

pll\_powerdown (2)

pll\_locked

Locked (output of PLL\_L/R)

Keep the TX side user logic under reset until this point

#### Note to Figure 4-15:

$(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.}$

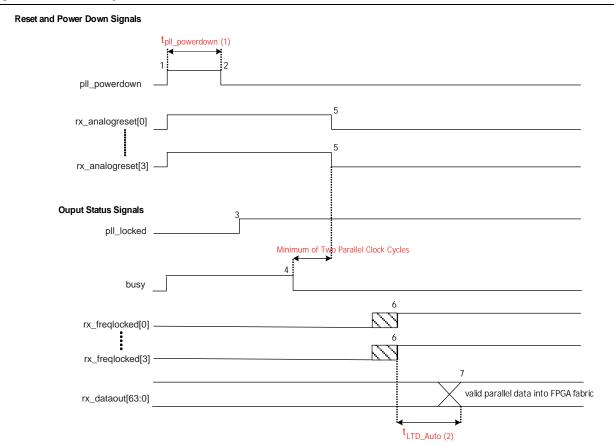

#### Receiver and Transmitter Channel Set-up—Receiver CDR in Automatic Lock Mode

This configuration contains both a transmitter and receiver channel. For PMA Direct drive  $\times N$  mode, with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 4–16. In this example, N = 4.

Figure 4-16. Reset Sequence with CDR in Automatic Lock Mode

#### Notes to Figure 4-16:

- $(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.} \\$

- (2) For t<sub>LTD Auto</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

As shown in Figure 4–16, for the receiver and transmitter channel in PMA Direct drive ×4 double-width configuration with CDR in automatic lock mode, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of t<sub>pll\_powerdown</sub> (the time between markers 1 and 2).

- 2. Keep the rx\_analogreset signal asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), the transmitter is ready to accept parallel data from the FPGA fabric and transmitting serial data reliably.

- 4. For the receiver operation, after de-assertion of the busy signal, wait for a minimum of two parallel clock cycles to de-assert the rx\_analogreset signals of each channel. After rx\_analogreset is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock.

- 5. Wait for the rx\_freqlocked signal from each channel to go high. The rx\_freqlocked signal of each channel may go high at different times (as indicated by the slashed pattern at marker 6).

- 6. In a PMA Direct drive  $\times 4$  double-width configuration, when the rx\_freqlocked signals of all the channels has gone high (marker 6), from that point onwards, wait for at least  $t_{LTD\_Auto}$  (marker 7) for the receiver parallel clock to become stable. At this point, all the receivers are ready for transferring valid parallel data into the FPGA fabric (until this time, Altera recommends that the user logic that processes this data be under reset).

#### Receiver and Transmitter Channel Set-up—Receiver CDR in Manual Lock Mode

This configuration contains both a transmitter and receiver channel. For PMA Direct drive  $\times N$  mode, with receiver CDR in manual lock mode, use the reset sequence shown in Figure 4–17. In this example, N = 4.

Figure 4-17. Reset Sequence with CDR in Manual Lock Mode

#### Notes to Figure 4-17:

- $(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.}$

- (2) For t<sub>LTR\_LTD\_Manual</sub> duration, refer to the *DC* and Switching Characteristics for Stratix IV Devices chapter.

- (3) For  $t_{LTD\_Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–17, for the receiver and transmitter channel in PMA Direct drive ×4 double-width configuration with CDR in manual lock mode, follow these reset steps:

- 1. After power up, assert pll\_powerdown for a minimum period of t<sub>pll\_powerdown</sub> (the time between markers 1 and 2).

- 2. Keep the rx\_analogreset and rx\_locktorefclk signals asserted and the rx\_locktodata signal de-asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), the transmitter is ready to accept parallel data from the FPGA fabric and transmitting serial data reliably.

- 4. For the receiver operation, after de-assertion of the busy signal (marker 4), wait for a minimum of two parallel clock cycles to de-assert the rx\_analogreset signal. After the rx\_analogreset signal is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock because rx\_locktorefclk is asserted.

- 5. Wait for the rx\_pll\_locked signal from each channel to go high. The rx\_pll\_locked signal of each channel may go high at different times with respect to each other (indicated by the slashed pattern at marker 6).

- 6. In a PMA Direct drive ×4 double-width configuration, when the rx\_pll\_locked signal of all the channels has gone high, from that point onwards, wait for at least t\_LTR\_LTD\_Manual, then de-assert rx\_locktorefclk and assert rx\_locktodata (marker 7). At this point, the receiver CDR of all the channels enters into lock-to-data mode and starts locking to the received data.

- 7. After assertion of the rx\_locktodata signal, from that point onwards, wait for at least t<sub>LTD\_Manual</sub> (marker 8) for the receiver parallel clock to become stable. At this point, all the receivers are ready for transferring valid parallel data into the FPGA fabric (until this time, Altera recommends that the user logic that processes this data be under reset).

## Basic (PMA Direct) Drive x1 Mode

The following timing diagram examples are used to describe the reset and power down sequences for Basic (PMA Direct) drive mode without bonding between the transceiver channels.

Table 4–8 lists the reset and power-down sequences for Basic (PMA Direct) drive ×1 functional mode.

Table 4–8. Reset and Power-Down Sequences for Basic (PMA Direct) Drive ×1 Configurations

| Channel Set Up           | Functional Mode | Refer to                                                                                   |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------|

| Receiver and Transmitter |                 | "Receiver and Transmitter Channel Set-Up—Receiver CDR in Automatic Lock Mode" on page 4–32 |

| Receiver and Transmitter |                 | "Receiver and Transmitter Channel Set-up—Receiver CDR in Manual Lock Mode" on page 4–34    |

# Receiver and Transmitter Channel Set-Up—Receiver CDR in Automatic Lock Mode

This configuration contains both a transmitter and receiver channel. For Basic (PMA Direct) drive ×1 mode, with receiver CDR in automatic lock mode, use the reset sequence shown in Figure 4–18. In this example, four channels are configured in this mode.

Figure 4–18. Reset Sequence with CDR in Automatic Lock Mode

#### Notes to Figure 4-18:

- (1) For t<sub>pll powerdown</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–18, for the receiver and transmitter channel in Basic (PMA Direct) drive double-width configuration, non-bonded with CDR in automatic lock mode, follow these reset steps:

- After power up, assert pll\_powerdown of each channel for a minimum period of t<sub>pll\_powerdown</sub> (the time between markers 1 and 2).

- 2. Keep the rx\_analogreset signal of each channel asserted during this time period. After you de-assert the pll\_powerdown signal on all channels, the transmitter PLL of each channel starts locking to the transmitter input reference clock.

- 3. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), the transmitters are ready for accepting parallel data from the FPGA fabric and subsequently transmitting serial data reliably.

- 4. For the receiver operation, after de-assertion of the busy signal, wait for a minimum of two parallel clock cycles to de-assert the rx\_analogreset signals of each channel. After rx\_analogreset is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock.

- 5. Wait for the rx\_freqlocked signal from each channel to go high. The rx\_freqlocked signal of each channel may go high at different times (indicated by the slashed pattern at marker 6).

- 6. In a Basic (PMA Direct) drive double-width configuration without bonding between channels, when the rx\_freqlocked signals of all the channels have gone high (marker 6), from that point onwards, wait for at least t<sub>LTD\_Auto</sub> (marker 7) for the receiver parallel clock to become stable. At this point, all the receivers are ready for transferring valid parallel data into the FPGA fabric (until this time, Altera recommends that the user logic that processes this data be under reset).

# Receiver and Transmitter Channel Set-up—Receiver CDR in Manual Lock Mode

This configuration contains both a transmitter and receiver channel. For Basic (PMA Direct) drive  $\times 1$  mode, with receiver CDR in manual lock mode, use the reset sequence shown in Figure 4–19. In this example, four channels are configured in this mode.

Figure 4-19. Reset Sequence with CDR in Manual Lock Mode

#### Notes to Figure 4-19

- $(1) \quad \text{For } t_{\text{pll\_powerdown}} \text{ duration, refer to the } \textit{DC and Switching Characteristics for Stratix IV Devices} \text{ chapter.}$

- (2) For  $t_{LTR\_LTD\_Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

- (3) For  $t_{LTD\_Manual}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–19, for the receiver and transmitter channel in Basic (PMA Direct) drive double-width configuration, non-bonded with CDR in manual lock mode, follow these reset steps:

- After power up, assert pll\_powerdown of each channel for a minimum period of t<sub>pll\_powerdown</sub> (the time between markers 1 and 2).

- 2. Keep the rx\_analogreset and rx\_locktorefclk signals of each channel asserted and the rx\_locktodata signals de-asserted during this time period. After you de-assert the pll\_powerdown signal, the transmitter PLL starts locking to the transmitter input reference clock.

- 3. When the transmitter PLL locks, as indicated by the pll\_locked signal going high (marker 3), the transmitters are ready to accept parallel data from the FPGA fabric and subsequently transmitting serial data reliably.

- 4. For the receiver operation, after de-assertion of the busy signal (marker 4), wait for a minimum of two parallel clock cycles to de-assert the rx\_analogreset signal of each channel. After the rx\_analogreset signal is de-asserted, the receiver CDR of each channel starts locking to the receiver input reference clock because rx\_locktorefclk is asserted.

- 5. Wait for the rx\_pll\_locked signal from each channel to go high. The rx\_pll\_locked signal of each channel may go high at different times with respect to each other (indicated by the slashed pattern at marker 6).

- 6. In a Basic (PMA Direct) drive double-width configuration without bonding between channels, when the rx\_pll\_locked signal of all the channels has gone high, from that point onwards, wait for at least tLTR\_LTD\_Manual, then de-assert rx\_locktorefclk and assert rx\_locktodata (marker 7). At this point, the receiver CDR of all the channels enters into lock-to-data mode and starts locking to the received data.

- 7. After assertion of the rx\_locktodata signal, from that point onwards, wait for at least t<sub>LTD\_Manual</sub> (marker 8) for the receiver parallel clock to be stable. At this point, all the receivers are ready for transferring valid parallel data into the FPGA fabric (until this time, Altera recommends that the user logic that processes this data be reset).

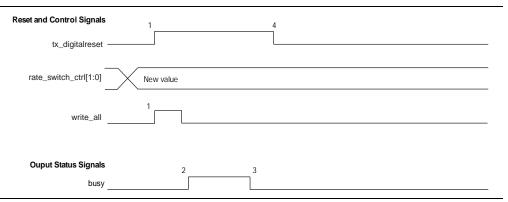

## **Dynamic Reconfiguration Reset Sequences**

When using dynamic reconfiguration in data rate divisions in TX or channel and TX CMU PLL select/reconfig modes, use the following reset sequences.

# Reset Sequence when Using Dynamic Reconfiguration with the 'data rate division in TX' Option

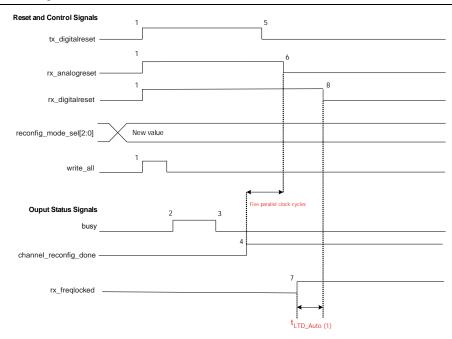

Use the example reset sequence shown in Figure 4–20 when you use the dynamic reconfiguration controller to change the data rate of the transceiver channel. In this example, dynamic reconfiguration is used to dynamically reconfigure the data rate of the transceiver channel configured in Basic ×1 mode with the receiver CDR in automatic lock mode.

Figure 4–20. Reset Sequence When Using the Dynamic Reconfiguration Controller to Change the Data Rate of the Transceiver Channel

As shown in Figure 4–20, when using the dynamic reconfiguration controller to change the configuration of the transmitter channel, follow these reset steps:

- 1. After power up and properly establishing that the transmitter is operating as desired, write the desired new value for the data rate in the appropriate register (in this example, rate\_switch\_ctrl[1:0]) and subsequently assert the write\_all signal (marker 1) to initiate the dynamic reconfiguration.

- For more information, refer to the *Dynamic Reconfiguration in Stratix IV Devices* chapter.

- 2. Assert the tx\_digitalreset signal.

- 3. As soon as write\_all is asserted, the dynamic reconfiguration controller starts to execute its operation. This is indicated by the assertion of the busy signal (marker 2).

- 4. After the completion of dynamic reconfiguration, the busy signal is de-asserted (marker 3).

- 5. Lastly, tx\_digitalreset can be de-asserted to continue with the transmitter operation (marker 4).

# Reset Sequence when Using Dynamic Reconfiguration with the 'Channel and TX PLL select/reconfig' Option

Use the example reset sequence shown in Figure 4–21 when you are using the dynamic reconfiguration controller to change the TX PLL settings of the transceiver channel. In this example, the dynamic reconfiguration is used to dynamically reconfigure the data rate of the transceiver channel configured in Basic ×1 mode with receiver CDR in automatic lock mode.

Figure 4–21. Reset Sequence When Using the Dynamic Reconfiguration Controller to Change the TX PLL Settings of the Transceiver Channel

#### Note to Figure 4-21:

(1) For  $t_{LTD\ Auto}$  duration, refer to the DC and Switching Characteristics for Stratix IV Devices chapter.

As shown in Figure 4–21, when using the dynamic reconfiguration controller to change the configuration of the transceiver channel, follow these reset steps:

- After power up and establishing that the transceiver is operating as desired, write the desired new value in the appropriate registers (including reconfig\_mode\_sel[2:0]) and subsequently assert the write\_all signal (marker 1) to initiate the dynamic reconfiguration.

- For more information, refer to the *Dynamic Reconfiguration in Stratix IV Devices* chapter.

- 2. Assert the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals.

- 3. As soon as write\_all is asserted, the dynamic reconfiguration controller starts to execute its operation. This is indicated by the assertion of the busy signal (marker 2).

- 4. Wait for the assertion of the channel\_reconfig\_done signal (marker 4) that indicates the completion of dynamic reconfiguration in this mode.

- 5. After assertion of the channel\_reconfig\_done signal, de-assert tx\_digitalreset (marker 5) and wait for at least five parallel clock cycles to de-assert the rx\_analogreset signal (marker 6).

- 6. Lastly, wait for the rx\_freqlocked signal to go high. After rx\_freqlocked goes high (marker 7), wait for t<sub>LTD\_Auto</sub> to de-assert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

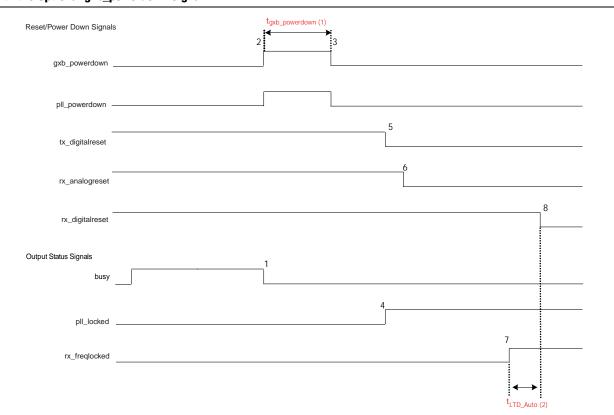

### **Power Down**

The Quartus II software automatically selects the power-down channel feature, which takes effect when you configure the Stratix IV device. All unused transceiver channels and blocks are powered down to reduce overall power consumption. The gxb\_powerdown signal is an optional transceiver block signal. It powers down all transceiver channels and all functional blocks in the transceiver block. The minimum pulse width for this signal is 1  $\mu$ s. After power up, if you use the gxb\_powerdown signal, wait for de-assertion of the busy signal, then assert the gxb\_powerdown signal for a minimum of 1  $\mu$ s. Lastly, follow the sequence shown in Figure 4–22.

The de-assertion of the busy signal indicates proper completion of the offset cancellation process on the receiver channel.

Figure 4–22. Sample Reset Sequence of Four Receiver and Transmitter Channels-Receiver CDR in Automatic Lock Mode with the Optional gxb\_powerdown Signal

#### Notes to Figure 4-22:

- (1) For  $t_{gxb\_powerdown}$  duration, refer to the *DC* and Switching Characteristics for Stratix IV Devices chapter.

- (2) For t<sub>LTD Auto</sub> duration, refer to the *DC and Switching Characteristics for Stratix IV Devices* chapter.

## **Simulation Requirements**

The following are simulation requirements:

- The gxb\_powerdown port is optional. In simulation, if the gxb\_powerdown port is not instantiated, you must assert the tx\_digitalreset, rx\_digitalreset, and rx\_analogreset signals appropriately for correct simulation behavior.

- If the gxb\_powerdown port is instantiated, and the other reset signals are not used, you must assert the gxb\_powerdown signal for at least one parallel clock cycle for correct simulation behavior.

- You can de-assert the rx\_digitalreset signal immediately after the rx\_freqlocked signal goes high to reduce the simulation run time. It is not necessary to wait for t<sub>LTD\_Auto</sub> (as suggested in the actual reset sequence).

- The busy signal is de-asserted after about 20 parallel reconfig\_clk clock cycles in order to reduce simulation run time. For silicon behavior in hardware, you can follow the reset sequences described in the previous pages.

- In PCIe mode simulation, you must assert the tx\_forceelecidle signal for at least one parallel clock cycle before transmitting normal data for correct simulation behavior.

## **Reference Information**

For more information about some useful reference terms used in this chapter, refer to the links listed in Table 4–9.

Table 4-9. Reference Information (Part 1 of 2)

| Terms Used in this Chapter              | Useful Reference Points |

|-----------------------------------------|-------------------------|

| Automatic Lock Mode                     | page 4–8                |

| Basic (PMA Direct) Drive x1 Mode        | page 4–31               |

| Basic (PMA Direct) Drive xN Mode        | page 4–25               |

| Bonded channel configuration            | page 4–6                |

| busy                                    | page 4–3                |

| Dynamic Reconfiguration Reset Sequences | page 4–36               |

| gxb_powerdown                           | page 4–3                |

| LTD                                     | page 4–6                |

| LTR                                     | page 4–6                |

| Manual Lock Mode                        | page 4–10               |

| Non-Bonded channel configuration        | page 4–15               |

| PCIe                                    | page 4–22               |

| pll_locked                              | page 4–3                |

| pll_powerdown                           | page 4–3                |

| rx_analogreset                          | page 4–2                |

| rx_digitalreset                         | page 4–2                |

| rx_freqlocked                           | page 4–3                |

Table 4-9. Reference Information (Part 2 of 2)

| Terms Used in this Chapter | Useful Reference Points |

|----------------------------|-------------------------|

| rx_pll_locked              | page 4–3                |

| tx_digitalreset            | page 4–2                |

## **Document Revision History**

Table 4–10 lists the revision history for this chapter.

Table 4-10. Document Revision History

| Date           | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2014   | 4.4     | Updated Figure 4–4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| September 2012 | 4.3     | Updated Table 4–2 to close FB #65274.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| December 2011  | 4.2     | Updated Table 4–2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| February 2010  | 4.1     | <ul> <li>Updated the "Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode", "Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode", "Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode", "Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode", "Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode", "Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode", "Receiver and Transmitter Channel Set-up—Receiver CDR in Automatic Lock Mode", "Receiver and Transmitter Channel Set-up—Receiver CDR in Manual Lock Mode"</li> <li>Updated Figure 4–4, Figure 4–5, Figure 4–6, Figure 4–7, Figure 4–16, Figure 4–17,</li> </ul> |

|                |         | Figure 4–18, and Figure 4–19.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |