# 5. Quartus II Support for HardCopy II Devices

H51022-2.5

# HardCopy II Device Support

Altera® HardCopy® II devices feature 1.2-V, 90 nm process technology, and provide a structured ASIC alternative to increasingly expensive multi-million gate ASIC designs. The HardCopy II design methodology offers a fast time-to-market schedule, providing ASIC designers with a solution to long ASIC development cycles. Using the Quartus® II software, you can leverage a Stratix® II FPGA as a prototype and seamlessly migrate your design to a HardCopy II device for production.

This document discusses the following topics:

- "HardCopy II Development Flow" on page 5–3

- "HardCopy II Device Resource Guide" on page 5–7

- "HardCopy II Recommended Settings in the Quartus II Software" on page 5–12

- "HardCopy II Utilities Menu" on page 5–25

For more information about HardCopy II, HardCopy Stratix, and HardCopy APEX<sup>TM</sup> devices, refer to the respective device data sheets in the *HardCopy Series Handbook*.

# HardCopy II Design Benefits

Designing with HardCopy II structured ASICs offers substantial benefits over other structured ASIC offerings:

- Prototyping using a Stratix II FPGA for functional verification and system development reduces total project development time

- Seamless migration from a Stratix II FPGA prototype to a HardCopy II device reduces time to market and risk

- Unified design methodology for Stratix II FPGA design and HardCopy II design reduces the need for ASIC development software

- Low up-front development cost of HardCopy II devices reduces the financial risk to your project

#### Quartus II Features for HardCopy II Planning

With the Quartus II software you can design a HardCopy II device using a Stratix II device as a prototype. The Quartus II software contains the following expanded features for HardCopy II device planning:

HardCopy II Companion Device Assignment—Identifies compatible HardCopy II devices for migration with the Stratix II device currently selected.

This feature constrains the pins of your Stratix II FPGA prototype making it compatible with your HardCopy II device. It also constrains the correct resources available for the HardCopy II device making sure that your Stratix II FPGA design does not become incompatible. In addition, you are still required to compile the design targeting the HardCopy II device to ensure that the design fits, routes, and meets timing.

- HardCopy II Utilities—The HardCopy II Utilities functions create or overwrites HardCopy II companion revisions, change revisions to use, and compare revisions for equivalency.

- HardCopy II Advisor—The HardCopy II Advisor helps you follow the necessary steps to successfully submit a HardCopy II design to Altera's HardCopy Design Center.

The HardCopy II Advisor is similar to the Resource Optimization Advisor and Timing Optimization Advisor. The HardCopy II Advisor provides guidelines you can follow during development, reporting the tasks completed as well as the tasks that remain to be completed during development

- HardCopy II Floorplan—The Quartus II software can show a preliminary floorplan view of your HardCopy II design's Fitter placement results.

- HardCopy II Design Archiving—The Quartus II software archives the HardCopy II design project's files needed to handoff the design to the HardCopy Design Center.

This feature is similar to the Quartus II software HardCopy Files Wizard used for HardCopy Stratix and HardCopy APEX families.

- HardCopy II Device Preliminary Timing—The Quartus II software performs a timing analysis of HardCopy II devices based on preliminary timing models and Fitter placements. Final timing results for HardCopy II devices are provided by the HardCopy Design Center.

- HardCopy II Handoff Report—The Quartus II software generates a handoff report containing information about the HardCopy II design used by the HardCopy Design Center in the design review process.

- Formal Verification—Cadence Encounter Conformal software can now perform formal verification between the source RTL design files and post-compile gate level netlist from a HardCopy II design.

# HardCopy II Development Flow

In the Quartus II software, you have two methods for designing your Stratix II FPGA and HardCopy II companion device together in one Quartus II project.

- Design the HardCopy II device first, and create the Stratix II FPGA companion device second and build your prototype for in-system verification

- Design the Stratix II FPGA first and create a HardCopy II companion device second

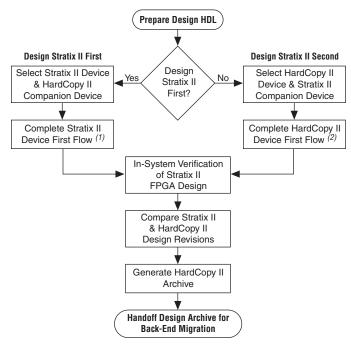

Both of these flows are illustrated at a high level in Figure 5–1. The added features in the HardCopy II Utilities menu assist you in completing your HardCopy II design for submission to Altera's HardCopy Design Center for back-end implementation.

Figure 5-1. HardCopy II Flow in Quartus II Software

Notes for Figure 5-1:

- (1) Refer to Figure 5–2 for an expanded description of this process.

- (2) Refer to Figure 5–3 for an expanded description of this process.

# **Designing the Stratix II FPGA First**

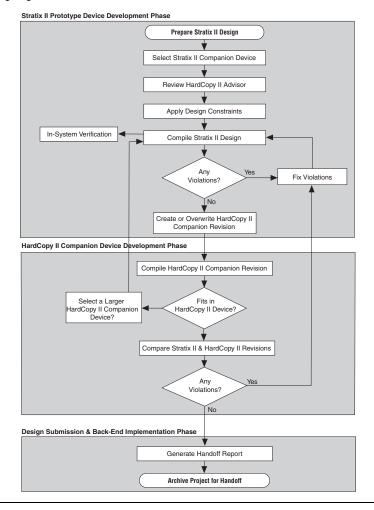

The HardCopy II development flow beginning with the Stratix II FPGA prototype is very similar to a traditional Stratix II FPGA design flow, but requires a few additional tasks be performed to migrate the design to the HardCopy II companion device. To design your HardCopy II device using the Stratix II FPGA as a prototype, complete the following tasks:

- Specify a HardCopy II device for migration

- Compile the Stratix II FPGA design

- Create and compile the HardCopy II companion revision

- Compare the HardCopy II companion revision compilation to the Stratix II device compilation

Figure 5–2 provides an overview highlighting the development process for designing with a Stratix II FPGA first and creating a HardCopy II companion device second.

Figure 5-2. Designing Stratix II Device First Flow

Prototype your HardCopy II design by selecting and then compiling a Stratix II device in the Quartus II software.

After you compile the Stratix II design successfully, you can view the HardCopy II Device Resource Guide in the Quartus II software Fitter report to evaluate which HardCopy II devices meet your design's resource requirements. When you are satisfied with the compilation results and the choice of Stratix II and HardCopy II devices, on the Assignments menu, click **Settings**. In the **Category** list, select **Device**. In the **Device** page, select a HardCopy II companion device.

After you select your HardCopy II companion device, do the following:

- Review the HardCopy II Advisor for required and recommended tasks to perform

- Enable Design Assistant to run during compilation

- Add timing and location assignments

- Compile your Stratix II design

- Create your HardCopy II companion revision

- Compile your design for the HardCopy II companion device

- Use the HardCopy II Utilities to compare the HardCopy II companion device compilation with the Stratix II FPGA revision

- Generate a HardCopy II Handoff Report using the HardCopy II Utilities

- Generate a HardCopy II Handoff Archive using the HardCopy II Utilities

- Arrange for submission of your HardCopy II handoff archive to Altera's HardCopy Design Center for back-end implementation

For more information about the overall design flow using the Quartus II software, refer to the *Introduction to Quartus II* manual on the Altera website at www.altera.com.

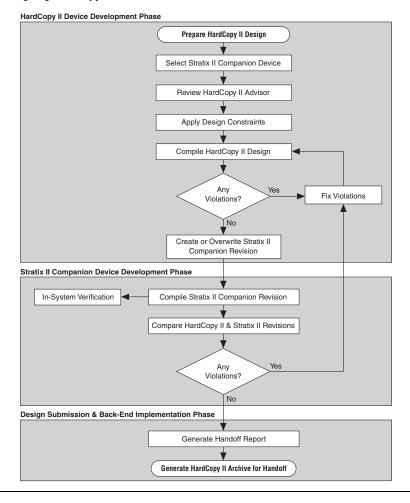

#### Designing the HardCopy II Device First

The HardCopy II family presents a new option in designing unavailable in previous HardCopy families. You can design your HardCopy II device first and create your Stratix II FPGA prototype second in the Quartus II software. This allows you to see your potential maximum performance in the HardCopy II device immediately during development, and you can create a slower performing FPGA prototype of the design for in-system verification. This design process is similar to the traditional HardCopy II design flow where you build the FPGA first, but instead, you merely change the starting device family. The remaining tasks to complete your design for both Stratix II and HardCopy II devices roughly follow the same process (Figure 5–3). The HardCopy II Advisor adjusts its list of tasks based on which device family you start with, Stratix II or HardCopy II, to help you complete the process seamlessly.

Figure 5-3. Designing HardCopy II Device First Flow

# HardCopy II Device Resource Guide

The HardCopy II Device Resource Guide compares the resources required to successfully compile a design with the resources available in the various HardCopy II devices. The report rates each HardCopy II device and each device resource for how well it fits the design. The Quartus II software generates the HardCopy II Device Resource Guide for all designs successfully compiled for Stratix II devices. This guide is found in the Fitter folder of the Compilation Report. Figure 5–4 shows an example of the HardCopy II Device Resource Guide. Refer to Table 5–1 for an explanation of the color codes in Figure 5–4.

Figure 5-4. HardCopy II Device Resource Guide

|    | Re | source                       | Stratix II<br>EP2S130 | HC210W*    | HC210      | HC220      | HC220      | HC230       | HC240       | HC240       |

|----|----|------------------------------|-----------------------|------------|------------|------------|------------|-------------|-------------|-------------|

| 1  |    | Migration Compatibility      |                       | None       | None       | None       | None       | Medium      | None        | None        |

| 2  |    | Primary Migration Constraint |                       | Package    | Package    | Package    | Package    | Package     | Package     | Package     |

| 3  |    | Package                      | FBGA - 1020           | FBGA - 484 | FBGA - 484 | FBGA - 672 | FBGA - 780 | FBGA - 1020 | FBGA - 1020 | FBGA - 1508 |

| 1  | Ξ  | Logic                        |                       | 19%        | 19%        | 10%        | 10%        | 6%          | 4%          | 4%          |

| 5  |    | Logic cells                  | 35572 ALUTs           |            |            |            |            |             |             |             |

| 93 |    | DSP elements                 | 0                     |            | -          |            |            | -           |             |             |

| 7  | Ξ  | Pins                         |                       |            |            |            |            |             |             |             |

| 8  |    | Total                        | 515                   | 515 / 302  | 515 / 335  | 515 / 493  | 515 / 495  | 515 / 699   | 515 / 743   | 515 / 952   |

| 9  |    | Differential Input           | 0                     | 0 / 66     | 0 / 70     | 0 / 90     | 0 / 90     | 0 / 128     | 0 / 224     | 0 / 272     |

| 10 |    | Differential Output          | 0                     | 0 / 44     | 0 / 50     | 0 / 70     | 0 / 70     | 0 / 112     | 0 / 200     | 0 / 256     |

| 11 |    | PCI / PCI-X                  | 0                     | 0 / 153    | 0 / 167    | 0 / 245    | 0 / 247    | 0 / 359     | 0 / 367     | 0 / 472     |

| 12 |    | DQ                           | 0                     | 0 / 20     | 0 / 20     | 0 / 50     | 0 / 50     | 0 / 204     | 0 / 204     | 0 / 204     |

| 13 |    | DQS                          | 0                     | 0/8        | 0/8        | 0 / 18     | 0 / 18     | 0 / 72      | 0 / 72      | 0 / 72      |

| 14 | =  | Memory                       |                       |            |            |            |            |             |             |             |

| 15 |    | M-RAM                        | 6                     | 670        | 670        | 6/2        | 6/2        | 6/6         | 6/9         | 6/9         |

| 16 |    | M4K blocks & M512 blocks**   | 44                    | 44 / 190   | 44 / 190   | 44 / 408   | 44 / 408   | 44 / 614    | 44 / 816    | 44 / 816    |

| 17 | Ξ  | PLLs                         |                       |            |            |            |            |             |             |             |

| 18 |    | Enhanced                     | 2                     | 2/2        | 2/2        | 2/2        | 2/2        | 2/4         | 2/4         | 2/4         |

| 19 |    | Fast                         | 0                     | 0/2        | 0/2        | 0/2        | 0/2        | 0/4         | 0/8         | 0/8         |

| 20 |    | DLLs                         | 0                     | 0/1        | 0/1        | 0/1        | 0/1        | 0/2         | 0/2         | 0/2         |

| 21 | Ξ  | SERDES                       |                       |            |            |            |            |             |             |             |

| 22 |    | RX                           | 0                     | 0 / 17     | 0 / 21     | 0 / 31     | 0 / 31     | 0 / 46      | 0 / 92      | 0 / 116     |

| 23 |    | TX                           | 0                     | 0 / 18     | 0 / 19     | 0 / 29     | 0 / 29     | 0 / 44      | 0 / 88      | 0 / 116     |

| 24 | Ξ  | Configuration                |                       |            |            |            |            |             |             |             |

| 25 |    | CRC                          | 0                     | 0/0        | 0/0        | 0/0        | 0/0        | 0/0         | 0/0         | 0/0         |

| 26 |    | ASMI                         | 0                     | 0/0        | 0/0        | 0/0        | 0/0        | 0/0         | 0/0         | 0/0         |

| 27 |    | Remote Update                | 0                     | 0/0        | 0/0        | 0/0        | 0/0        | 0/0         | 0/0         | 0/0         |

| 28 |    | JTAG                         | 0                     | 0/1        | 0/1        | 0/1        | 0/1        | 0/1         | 0/1         | 0/1         |

Use this report to determine which HardCopy II device is a potential candidate for migration of your Stratix II design. The HardCopy II device package must be compatible with the Stratix II device package. A logic resource usage greater than 100% or a ratio greater than 1/1 in any category indicates that the design does not fit in that particular HardCopy II device.

| Table 5–1          | Table 5–1. HardCopy II Device Resource Guide Color Legend                                                                                                                              |                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Color              | Package Resource (1)                                                                                                                                                                   | Device Resources                                                                                                                                                                                                                                                 |  |  |  |  |

| Green<br>(High)    | The design can migrate to the Hardcopy II package and the design has been fitted with target device migration enabled in the HardCopy II Companion Device dialog box.                  | The resource quantity is within the range of the HardCopy II device and the design can likely migrate if all other resources also fit.  You are still required to compile the HardCopy II                                                                        |  |  |  |  |

|                    |                                                                                                                                                                                        | revision to make sure the design is able to route and migrate all other resources.                                                                                                                                                                               |  |  |  |  |

|                    | The design can migrate to the Hardcopy II package. However, the design has not been fitted with target device migration enabled in the <b>HardCopy II Companion Device</b> dialog box. | The resource quantity is within the range of the HardCopy II device. However, the resource is at risk of exceeding the range for the HardCopy II package.                                                                                                        |  |  |  |  |

| Orange<br>(Medium) |                                                                                                                                                                                        | If your target HardCopy II device falls in this category, compile your design targeting the HardCopy II device as soon as possible to check if the design fits and is able to route and migrate all other resources. You may need to migrate to a larger device. |  |  |  |  |

| Red<br>(None)      | The design cannot migrate to the Hardcopy II package.                                                                                                                                  | The resource quantity exceeds the range of the HardCopy II device. The design cannot migrate to this HardCopy II device.                                                                                                                                         |  |  |  |  |

#### Note to Table 5-1:

(1) The package resource is constrained by the Stratix II FPGA for which the design was compiled. Only vertical migration devices within the same package are able to migrate to HardCopy II devices.

The HardCopy II architecture consists of an array of fine-grained HCells, which are used to build logic equivalent to Stratix II adaptive logic modules (ALMs) and digital signal processing (DSP) blocks. The DSP blocks in HardCopy II devices match the functionality of the Stratix II DSP blocks, though timing of these blocks is different than the FPGA DSP blocks because they are constructed of HCell Macros. The M4K and M-RAM memory blocks in HardCopy II devices are equivalent to the Stratix II memory blocks. Preliminary timing reports of the HardCopy II device are available in the Quartus II software. Final timing results of the HardCopy II device are provided by the HardCopy Design Center after back-end migration is complete.

For more information about the HardCopy II device resources, refer to the *Introduction to HardCopy II Devices* and the *Description, Architecture* and Features chapters in the *HardCopy II Device Family Data Sheet* in the *HardCopy Series Handbook*.

The report example in Figure 5–4 shows the resource comparisons for a design compiled for a Stratix II EP2S130F1020 device. Based on the report, the HC230F1020 device in the 1,020-pin FineLine BGA® package is an appropriate HardCopy II device to migrate to. If the HC230F1020 device is not specified as a migration target during the compilation, its package and migration compatibility is rated orange, or Medium. The migration compatibilities of the other HardCopy II devices are rated red, or None, because the package types are incompatible with the Stratix II device. The 1,020-pin FBGA HC240 device is rated red because it is only compatible with the Stratix II EP2S180F1020 device.

Figure 5–5 shows the report after the (unchanged) design was recompiled with the HardCopy II HC230F1020 device specified as a migration target. Now the HC230F1020 device package and migration compatibility is rated green, or High.

HardCopy II Device Resource Guide Color Legend: -- Package Resource: The HardCopy II package can be migrated from the Stratix II FPGA selected package, and the design has been fitted with the target device migration enabled. Stratix II HC210W\* HC210 HC220 HC220 HC230 HC240 HC240 EP2S130 Migration Compatibility Primary Migration Constraint Package Package Package Package Package Package

FBGA - 672

Figure 5–5. HardCopy II Device Resource Guide with Target Migration Enabled

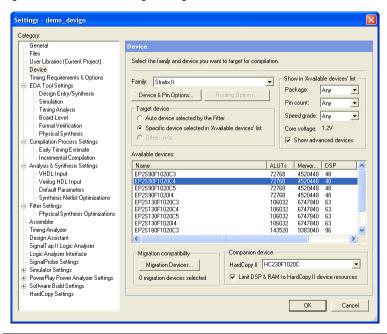

# HardCopy II Companion Device Selection

In the Quartus II software, you can select a HardCopy II companion device to help structure your design for migration from a Stratix II device to a HardCopy II device. To make your HardCopy II companion device selection, on the Assignments menu, click **Settings**. In the **Settings** dialog box in the **Category** list, select **Device** (Figure 5–6) and select your companion device from the **Available devices** list.

Selecting a HardCopy II Companion device to go with your Stratix II prototype constrains the memory blocks, DSP blocks, and pin assignments, so that your Stratix II and HardCopy II devices are migration-compatible. Pin assignments are constrained in the Stratix II design revision so that the HardCopy II device selected is pin-compatible. The Quartus II software also constrains the Stratix II design revision so it does not use M512 memory blocks or exceed the number of M-RAM blocks in the HardCopy II companion device.

Figure 5-6. Quartus II Settings Dialog Box

You can also specify your HardCopy II companion device using the following tool command language (Tcl) command:

```

set_global_assignment -name\

DEVICE TECHNOLOGY MIGRATION LIST <HardCopy II Device Part Number>

```

For example, to select the HC230F1020 device as your HardCopy II companion device for the EP2S130F1020C4 Stratix II FPGA, the Tcl command is:

```

set_global_assignment -name\

DEVICE TECHNOLOGY MIGRATION LIST HC230F1020C

```

# HardCopy II Recommended Settings in the Quartus II Software

The HardCopy II development flow involves additional planning and preparation in the Quartus II software compared to a standard FPGA design. This is because you are developing your design to be implemented in two devices: a prototype of your design in a Stratix II prototype FPGA, and a companion revision in a HardCopy II device for production. You need additional settings and constraints to make the Stratix II design compatible with the HardCopy II device and, in some cases, you must remove certain settings in the design. This section explains the additional settings and constraints necessary for your design to be successful in both Stratix II FPGA and HardCopy II structured ASIC devices.

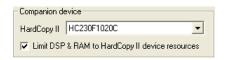

#### Limit DSP and RAM to HardCopy II Device Resources

On the Assignments menu, click **Settings** to view the **Settings** dialog box. In the **Category** list, select **Device**. In the **Family** list, select **Stratix II**. Under **Companion device**, **Limit DSP and RAM to HardCopy II device resources** is turned on by default (Figure 5–7). This maintains compatibility between the Stratix II and HardCopy II devices by ensuring your design does not use resources in the Stratix II device that are not available in the selected HardCopy II device.

If you require additional memory blocks or DSP blocks for debugging purposes using SignalTap® II, you can temporarily turn this setting off to compile and verify your design in your test environment. However, your final Stratix II and HardCopy II designs submitted to Altera for back-end migration must be compiled with this setting turned on.

Figure 5–7. Limit DSP and RAM to HardCopy II Device Resources Check Box

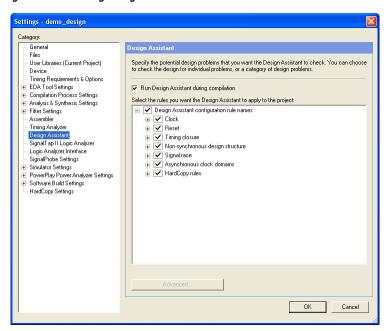

# **Enable Design Assistant to Run During Compile**

You must use the Quartus II Design Assistant to check all HardCopy series designs for design rule violations before submitting the designs to the Altera HardCopy Design Center. Additionally, you must fix all critical and high-level errors.

Altera recommends turning on the Design Assistant to run automatically during each compile, so that during development, you can see the violations you must fix.

For more information about the Design Assistant and the rules it uses, refer to the *Design Guidelines for HardCopy Series Devices* chapter of the *HardCopy Series Handbook*.

To enable the Design Assistant to run during compilation, on the Assignment menu, click **Settings**. In the **Category** list, select **Design Assistant** and turn on **Run Design Assistant during compilation** (Figure 5–8) or by entering the following Tcl command in the Tcl Console:

set global assignment -name ENABLE DRC SETTINGS ON

Figure 5-8. Enabling Design Assistant

# **Timing Settings**

Beginning in Quartus II Software version 7.1, TimeQuest is the recommended timing analysis tool for all designs. Classic Timing Analyzer is no longer supported and the HardCopy Design Center will not accept any designs which use Classic Timing Analyzer for timing closure.

If you are still using the Classic Timing Analyzer, Altera strongly recommends that you switch to TimeQuest.

For more information on how to switch to TimeQuest, refer to the *Switching to the TimeQuest Timing Analyzer* chapter of the *Quartus II Handbook*, volume 3, on the Altera website at www.altera.com.

When you specify the TimeQuest analyzer as the timing analysis tool, the TimeQuest analyzer guides the Fitter and analyzes timing results after compilation.

#### TimeQuest

The TimeQuest Timing Analyzer is a powerful ASIC-style timing analysis tool that validates timing in your design by using an industry-standard constraint, analysis, and reporting methodology. You can use the TimeQuest Timing Analyzer's GUI or command-line interface to constrain, analyze, and report results for all timing paths in your design.

Before running the TimeQuest Timing Analyzer, you must specify initial timing constraints that describe the clock characteristics, timing exceptions, and signal transition arrival and required times. You can specify timing constraints in the Synopsys Design Constraints (SDC) file format using the GUI or command-line interface. The Quartus II Fitter optimizes the placement of logic to meet your constraints.

During timing analysis, the TimeQuest Timing Analyzer analyzes the timing paths in the design, calculates the propagation delay along each path, checks for timing constraint violations, and reports timing results as slack in the Report pane and in the Console pane. If the TimeQuest Timing Analyzer reports any timing violations, you can customize the reporting to view precise timing information about specific paths, and then constrain those paths to correct the violations. When your design is free of timing violations, you can be confident that the logic will operate as intended in the target device.

The TimeQuest Timing Analyzer is a complete static timing analysis tool that you can use as a sign-off tool for Altera FPGAs and structured ASICs.

#### Setting Up the TimeQuest Timing Analyzer

If you want use TimeQuest for timing analysis, from the Assignments tab in the Quartus II software, click on **Timing Analysis Settings**, and in the pop-up window, click the **Use TimeQuest Timing Analyzer during compilation** tab.

Use the following Tcl command to use TimeQuest as your timing analysis engine:

```

set_global_assignment -name \

USE TIMEQUEST TIMING ANALYZER ON

```

You can launch the TimeQuest analyzer in one of the following modes:

- Directly from the Quartus II software

- Stand-alone mode

- Command-line mode

In order to perform a thorough Static Timing Analysis, you would need to specify all the timing requirements. The most important timing requirements are clocks and generated clocks, input and output delays, false paths and multi-cycle paths, minimum and maximum delays.

In TimeQuest, clock latency, and recovery and removal analysis are enabled by default.

For more information about TimeQuest, refer to the *Quartus II TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook* on the Altera website at **www.altera.com**.

#### **Constraints for Clock Effect Characteristics**

The create\_clock, create\_generated\_clock commands create ideal clocks and do not account for board effects. In order to account for clock effect characteristics, you can use the following commands:

- set\_clock\_latency

- set clock uncertainty

For more information about how to use these commands, refer to the *Quartus II TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook*.

Beginning in Quartus II version 7.1, you can use the new command derive\_clock\_uncertainty to automatically derive the clock uncertainties. This command is useful when you are not sure what the clock uncertainties might be. The calculated clock uncertainty values are based on I/O buffer, static phase errors (SPE) and jitter in the PLL's, clock networks, and core noises.

The derive\_clock\_uncertainty command applies inter-clock, intra-clock, and I/O interface uncertainties. This command automatically calculates and applies setup and hold clock uncertainties for each clock-to-clock transfer found in your design.

In order to get I/O interface uncertainty, you must create a virtual clock, then assign delays to the input/output ports by using the set\_input\_delay and set\_output\_delay commands for that virtual clock.

These uncertainties are applied in addition to those you specified using the set\_clock\_uncertainty command. However, if a clock uncertainty assignment for a source and destination pair was already defined, the new one will be ignored. In this case, you can use either the -overwrite command to overwrite the previous clock uncertainty command or manually remove them by using the remove\_clock\_uncertainty command.

The syntax for the derive\_clock\_uncertainty is as follows:

```

derive_clock_uncertainty [-h | -help] [-long_help]

[-dtw] [-overwrite]

```

where the arguments are listed in Table 5-2:

| Table 5–2. Arguments for derive_clock_uncertainty |                                                               |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------|--|--|--|

| Option                                            | Description                                                   |  |  |  |

| -h   -help                                        | Short help                                                    |  |  |  |

| -long_help                                        | Long help with examples and possible return values            |  |  |  |

| -dtw                                              | Creates PLLJ_PLLSPE_INFO.txt file                             |  |  |  |

| -overwrite                                        | Overwrites previously performed clock uncertainty assignments |  |  |  |

When the dtw option is used, a PLLJ\_PLLSPE\_INFO.txt file is generated. This file lists the name of the PLLs, as well as their jitter and SPE values in the design. This text file can be used by HCII\_DTW\_CU\_Calculator. When this option is used, clock uncertainties are not calculated.

For more information on the derive\_clock\_uncertainty command, refer to the *Quartus II TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook*.

Altera strongly recommends that you use the derive\_clock\_uncertainty command in the HardCopy II revision. The HardCopy Design Center will not be accepting designs that do not have clock uncertainty constraint by either using the derive\_clock\_uncertainty command or the HardCopy II Clock Uncertainty Calculator, and then using the set\_clock\_uncertainty command.

For more information on how to use the HardCopy II Clock Uncertainty Calculator, refer to the *HardCopy II Clock Uncertainty User Guide* available on the Altera website at **www.altera.com**.

#### Quartus II Software Features Supported for HardCopy II Designs

The Quartus II software supports optimization features for HardCopy II prototype development, including:

- Physical Synthesis Optimization

- LogicLock Regions

- PowerPlay Power Analyzer

- Incremental Compilation (Synthesis and Fitter)

- Maximum Fan-Out Assignments

#### Physical Synthesis Optimization

To enable Physical Synthesis Optimizations for the Stratix II FPGA revision of the design, on the Assignments menu, click **Settings**. In the **Settings** dialog box, in the **Category** list, select **Fitter Settings**. These optimizations are migrated into the HardCopy II companion revision for placement and timing closure. When designing with a HardCopy II device first, physical synthesis optimizations can be enabled for the HardCopy II device, and these post-fit optimizations are migrated to the Stratix II FPGA revision.

#### LogicLock™ Regions

The use of LogicLock Regions in the Stratix II FPGA is supported for designs migrating to HardCopy II. However, LogicLock Regions are not passed into the HardCopy II Companion Revision. You can use LogicLock in the HardCopy II design but you must create new LogicLock Regions in the HardCopy II companion revision. In addition, LogicLock Regions in HardCopy II devices can not have their properties set to **Auto Size**. However, Floating LogicLock regions are supported. HardCopy II LogicLock Regions must be manually sized and placed in the floorplan. When LogicLock Regions are created in a HardCopy II device, they start with width and height dimensions set to (1,1), and the origin coordinates for placement are at X1\_Y1 in the lower left corner of

the floorplan. You must adjust the size and location of the LogicLock Regions you created in the HardCopy II device before compiling the design.

•

For information about using LogicLock Regions, refer to the *Quartus II Analyzing and Optimizing Design Floorplan* chapter in volume 2 of the *Quartus II Handbook*.

#### PowerPlay Power Analyzer

You can perform power estimation and analysis of your HardCopy II and Stratix II devices using the PowerPlay Early Power Estimator. Use the PowerPlay Power Analyzer for more accurate estimation of your device's power consumption. The PowerPlay Early Power Estimator is available in the Quartus II software version 5.1 and later. The PowerPlay Power Analyzer supports HardCopy II devices in version 6.0 and later of the Quartus II software.

For more information about using the PowerPlay Power Analyzer, refer to the *Quartus II PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook* on the Altera website at www.altera.com.

#### Incremental Compilation

The use of the Quartus II Incremental Compilation in the Stratix II FPGA is supported when migrating a design to a HardCopy II device. Incremental compilation is supported in the Stratix II First design flow or HardCopy II First design flow.

To take advantage of Quartus II Incremental Compilation, organize your design into logical and physical partitions for synthesis and fitting (or place-and-route). Incremental compilation preserves the compilation results and performance of unchanged partitions in your design. This feature dramatically reduces your design iteration time by focusing new compilations only on changed design partitions. New compilation results are then merged with the previous compilation results from unchanged design partitions. You can also target optimization techniques, such as physical synthesis, to specific partitions while leaving other partitions untouched.

In addition, be aware of the following guidelines:

- User partitions and synthesis results are migrated to a companion device.

- LogicLock regions are suggested for user partitions, but are not migrated automatically.

- The first compilation after migration to a companion device requires a full compilation (all partitions are compiled), but subsequent compilations can be incremental if changes to the source RTL are not required. For example, PLL phase changes can be implemented incrementally if the blocks are partitioned.

- The entire design must be migrated between Stratix II and HardCopy II companion devices. The Quartus II software does not support migration of partitions between companion devices.

- Bottom-up Quartus II Incremental Compilation is not supported for HardCopy II devices.

- Physical Synthesis can be run on individual partitions within the originating device only. The resulting optimizations are preserved in the migration to the companion device.

For information about using Quartus II Incremental Compilation, refer to the *Quartus II Incremental Compilation for Hierarchical and Team-Based Design* chapter in volume 1 of the *Quartus II Handbook*.

#### Maximum Fanout Assignments

This feature is supported beginning in Quartus II 6.1. In order to meet timing, it may be necessary to limit the number of fanouts of a net in your design. You can limit the maximum fanout of a given net by using this feature.

For example, you can use the following Tcl command to enable the maximum fanout setting:

```

set_instance_assignment -name MAX_FANOUT <number>

- to\ <net name>

```

For example, if you want to limit the maximum fanout of net called "m3122\_combout\_1" to 25, the Tcl command is as follows:

```

set_instance_assignment -name MAX_FANOUT 25 -to\ m3122\_combout\_1

```

# Performing ECOs with Change Manager and Chip Planner

As designs grow larger and larger in density, the need to analyze the design for performance, routing congestion, logic placement, and executing Engineering Change Orders (ECOs) becomes critical. In addition to design analysis, you can use various bottom-up and top-down flows to implement and manage the design. This becomes difficult to manage since ECOs are often implemented as last minute changes to your design.

With the Altera® Chip Planner tool, you can shorten the design cycle time significantly. When changes are made to your design as ECOs, you do not have to perform a full compilation in the Quartus II software. Instead, you would make changes directly to the post place-and-route netlist, generate a new programming file, test the revised design by performing a gate-level simulation and timing analysis, and proceed to verify the fix on the system (if you are using a Stratix II FPGA as a prototype). Once the fix has been verified on the Stratix II FPGA, switch to the HardCopy II revision, apply the same ECOs, run the timing analyzer and assembler, perform a revision compare and then run the HardCopy II Netlist Writer for design submission.

There are three scenarios from a migration point of view:

- There are changes which can map one-to-one (that is, the same change can be implemented on each architecture—Stratix II FPGA and HardCopy II).

- There are changes that must be implemented differently on the two architectures to achieve the same result.

- There are some changes that cannot be implemented on both architectures.

The following sections outline the methods for migrating each of these types of changes.

#### Migrating One-to-One Changes

One-to-one changes are implemented using identical commands in both architectures. In general, such changes include those that affect only I/O cells or PLL cells. Some examples of one-to-one changes are changes such as creating, deleting or moving pins, changing pin or PLL properties, or changing pin connectivity (provided the source and destination of the connectivity changes are I/Os or PLLs). These can be implemented identically on both architectures.

If such changes are exported to Tcl, a direct reapplication of the generated Tcl script (with a minor text edit) on the companion revision should implement the appropriate changes as follows:

- Export the changes from the Change Manager to Tcl.

- Apply the Tcl script to the companion revision.

A partial list of examples of this type are as follows:

- I/O creation, deletion, and moves

- I/O property changes (for example, I/O standards, delay chain settings, etc.)

- PLL property changes

- Connectivity changes between non-LCELL\_COMB atoms (for example, PLL to I/O, DSP to I/O, etc.)

#### Migrating Changes that must be Implemented Differently

Some changes must be implemented differently on the two architectures. Changes affecting the logic of the design may fall into this category. Examples are LUTMASK changes, LC\_COMB/HSADDER creation and deletion, and connectivity changes not covered in the previous section.

Another example of this would be to have different PLL settings for the Stratix II and the HardCopy II revisions.

For more information about how to use different PLL settings for the Stratix II and HardCopy II Devices, refer to AN432: Using Different PLL Settings Between Stratix II and HardCopy II Devices.

Table 5–3 summarizes suggested implementation for various changes.

| Table 5–3. Implementation Suggestions for Various Changes (Part 1 of 2) |                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Change Type                                                             | Suggested Implementation                                                                                                                                                                                                                                                                                        |  |  |  |

| LUTMASK changes                                                         | Because a single Stratix II atom may require multiple HardCopy II atoms to implement, it may be necessary to change multiple HardCopy II atoms to implement the change, including adding or modifying connectivity                                                                                              |  |  |  |

| Make/Delete LC_COMB                                                     | If you are using a Stratix II LC_COMB in extended mode (7-LUT) or using a SHARE chain, you must create multiple atoms to implement the same logic functions in HardCopy II. Additionally, the placement of the LC_COMB cell has no meaning in the companion revision as the underlying resources are different. |  |  |  |

| Table 5–3. Implementation Suggestions for Various Changes (Part 2 of 2) |                                                                                                                                                                                                                                                       |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Change Type                                                             | Suggested Implementation                                                                                                                                                                                                                              |  |  |

| Make/Delete LC_FF                                                       | The basic creation and deletion is the same on both architectures. However, as with LC_COMB creation and deletion, the location of an LC_FF in a HardCopy II revision has no meaning in the Stratix II revision and vice versa.                       |  |  |

| Editing Logic Connectivity                                              | Because a Stratix II LCELL_COMB atom may have to be broken up into several HardCopy II LCELL_COMB atoms, the source or destination ports for connectivity changes may need to be analyzed to properly implement the change in the companion revision. |  |  |

#### **Changes that Cannot be Migrated**

A small set of changes cannot be implemented in the other architecture because they do not make sense in the other architecture. The best example of this occurs when moving logic in a design; because the logic fabric is different between the two architectures, locations in Stratix II make no sense in HardCopy II and vice versa.

# Overall Migration Flow

This section outlines the migration flow and the suggested procedure for implementing changes in both revisions to ensure a successful Revision Compare such that the design can be submitted to the HardCopy Design Center.

# **Preparing the Revisions**

The general procedure for migrating changes between devices is the same, whether going from Stratix II to HardCopy II or vice versa. The major steps are as follows:

- 1. Compile the design on the initial device.

- 2. Migrate the design from the initial device to the target device in the companion revision.

- 3. Compile the companion revision.

- 4. Perform a Revision Compare operation. The two revisions should pass the Revision Compare.

If testing identifies problems requiring ECO changes, equivalent changes can be applied to both Stratix II and HardCopy II revisions, as described in the next section.

#### **Applying ECO Changes**

The general flow for applying equivalent changes in companion revisions is as follows:

- Make changes in one revision using the Chip Planner tools (Chip Planner, Resource Property Editor, and Change Manager), then verify and export these changes. The procedure for doing this is as follows:

- a. Make changes using the Chip Planner tool.

- b. Perform a netlist check using the Check and Save All Netlist Changes command.

- c. Verify correctness using timing analysis, simulation, and prototyping (Stratix II only). If more changes are required, repeat steps a-b.

- d. Export change records from the Change Manager to Tcl scripts, or .csv or .txt file formats.

- This exported file is used to assist in making the equivalent changes in the companion revision.

- 2. Open the companion revision in the Quartus II software.

- Using the exported file, manually reapply the changes using the Chip Planner tool.

- As stated previously, some changes can be reapplied directly to the companion revision (either manually or by applying the Tcl commands), while others require some modifications.

- Perform a Revision Compare operation. The revisions should now match once again.

- 5. Verify the correctness of all changes (you may need to run timing analysis).

- Run the HardCopy II Assembler and the HardCopy II Netlist Writer for design submission along with handoff files.

The Tcl command for running the HardCopy II Assembler is as follows:

```

execute_module -tool asm -args "--

read_settings_files=\ off --write_settings_files=off"

```

The Tcl command for the HardCopy II Netlist Writer is as follows:

```

execute_module -tool cdb -args "--

generate hardcopyii files"\

```

For more information about using Chip Planner, refer to the *Quartus II Engineering Change Management with Chip Planner* chapter in volume 3 of the *Quartus II Handbook* at www.altera.com.

# Formal Verification of Stratix II and HardCopy II Revisions

Third-party formal verification software is available for your HardCopy II design. Cadence Encounter Conformal verification software is used for Stratix II and HardCopy II families, as well as several other Altera product families.

To use the Conformal software with the Quartus II software project for your Stratix II and HardCopy II design revisions, you must enable the **EDA Netlist Writer**. It is necessary to turn on the EDA Netlist Writer so it can generate the necessary netlists and command files needed to run the Conformal software. To automatically run the EDA Netlist Writer during the compile of your Stratix II and HardCopy II design revisions, perform the following steps:

- On the Assignment menu, click EDA Tool Settings. The Settings dialog box displays.

- 2. In the **EDA Tool Settings** list, select **Formal Verification**, and in the **Tool name** list, select **Conformal LEC**.

- Compile your Stratix II and Hardcopy II design revisions, with both the EDA Tool Settings and the Conformal LEC turned on so the EDA Netlist Writer automatically runs.

The Quartus II EDA Netlist Writer produces one netlist for Stratix II when it is run on that revision, and generates a second netlist when it runs on the HardCopy II revision. You can compare your Stratix II post-compile netlist to your RTL source code using the scripts generated by the EDA Netlist Writer. Similarly, you can compare your HardCopy II post-compile netlist to your RTL source code with scripts provided by the EDA Netlist Writer.

For more information about using the Cadence Encounter Conformal verification software, refer to the *Cadence Encounter Conformal Support* chapter in volume 3 of the *Quartus II Handbook*.

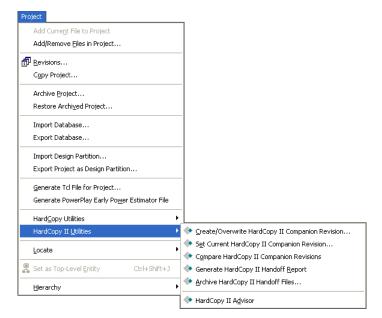

# HardCopy II Utilities Menu

The **HardCopy II Utilities** menu in the Quartus II software is shown Figure 5–9. To access this menu, on the Project menu, click **HardCopy II Utilities**. This menu contains the main functions you use to develop your HardCopy II design and Stratix II FPGA prototype companion revision. From the HardCopy II Utilities menu, you can:

- Create or update HardCopy II companion revisions

- Set which HardCopy II companion revision is the current revision

- Generate a HardCopy II Handoff Report for design reviews

- Archive HardCopy II Handoff Files for submission to the HardCopy Design Center

- Compare the companion revisions for functional equivalence

- Track your design progress using the HardCopy II Advisor

Figure 5-9. HardCopy II Utilities Menu

Each of the features within **HardCopy II Utilities** is summarized in Table 5–4. The process for using each of these features is explained in the following sections.

| Table 5–4. HardCopy II Utilities Menu Options         |                                                                                                                                                                                             |                                                                      |                                                                                                                                                                                  |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Menu                                                  | Description                                                                                                                                                                                 | Applicable Design<br>Revision                                        | Restrictions                                                                                                                                                                     |  |  |

| Create/Overwrite<br>HardCopy II<br>Companion Revision | Create a new companion revision or update an existing companion revision for your Stratix II and HardCopy II design.                                                                        | Stratix II prototype<br>design and HardCopy II<br>Companion Revision | <ul> <li>Must disable Auto Device<br/>selection</li> <li>Must set a Stratix II device<br/>and a HardCopy II<br/>companion device</li> </ul>                                      |  |  |

| Set Current<br>HardCopy II<br>Companion Revision      | Specify which companion revision to associate with current design revision.                                                                                                                 | Stratix II prototype<br>design and HardCopy II<br>Companion Revision | Companion Revision must already exist                                                                                                                                            |  |  |

| Compare<br>HardCopy II<br>Companion<br>Revisions      | Compares the Stratix II design revision with the HardCopy II companion design revision and generates a report.                                                                              | Stratix II prototype<br>design and HardCopy II<br>Companion Revision | Compilation of both revisions must be complete                                                                                                                                   |  |  |

| Generate<br>HardCopy II Handoff<br>Report             | Generate a report containing important design information files and messages generated by the Quartus II compile                                                                            | Stratix II prototype<br>design and HardCopy II<br>Companion Revision | Compilation of both revisions must be complete     Compare HardCopy II Companion Revisions must have been executed                                                               |  |  |

| Archive HardCopy II<br>Handoff Files                  | Generate a Quartus II Archive<br>File specifically for submitting<br>the design to the HardCopy<br>Design Center. Similar to the<br>HardCopy Files Wizard for<br>HardCopy Stratix and APEX. | HardCopy II<br>Companion Revision                                    | Compilation of both revisions must be completed     Compare HardCopy II Companion Revisions must have been executed     Generate HardCopy Handoff Report must have been executed |  |  |

| HardCopy II Advisor                                   | Open an Advisor, similar to the<br>Resource Optimization<br>Advisor, helping you through<br>the steps of creating a<br>HardCopy II project.                                                 | Stratix II prototype<br>design and HardCopy II<br>Companion Revision | None                                                                                                                                                                             |  |  |

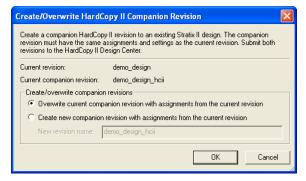

# **Companion Revisions**

HardCopy II designs follow a different development flow in the Quartus II software compared with previous HardCopy families. You can create multiple revisions of your Stratix II prototype design, but you can also create separate revisions of your design for a HardCopy II device.

The Quartus II software creates specific HardCopy II design revisions of the project in conjunction to the regular project revisions. These parallel design revisions for HardCopy II devices are called companion revisions.

Although you can create multiple project revisions, Altera recommends that you maintain only one Stratix II FPGA revision once you have created the HardCopy II companion revision.

When you have successfully compiled your Stratix II prototype FPGA, you can create a HardCopy II companion revision of your design and proceed with compiling the HardCopy II companion revision. To create a companion revision, on the Project menu, point to HardCopy II Utilities and click **Create/Overwrite HardCopy II Companion Revision**. Use the dialog box to create a new companion revision or overwrite an existing companion revision (Figure 5–10).

Figure 5–10. Create or Overwrite HardCopy II Companion Revision

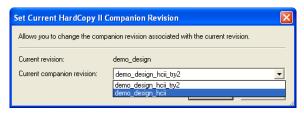

You can associate only one Stratix II revision to one HardCopy II companion revision. If you created more than one revision or more than one companion revision, set the current companion for the revision you are working on. On the Project menu, point to HardCopy II Utilities and click **Set Current HardCopy II Companion Revision** (Figure 5–11).

Figure 5-11. Set Current HardCopy II Companion Revision

#### Compiling the HardCopy II Companion Revision

The Quartus II software allows you to compile your HardCopy II design with preliminary timing information. The timing constraints for the HardCopy II companion revision can be the same as the Stratix II design used to create the revision. The Quartus II software contains preliminary timing models for HardCopy II devices and you can gauge how much performance improvement you can achieve in the HardCopy II device compared to the Stratix II FPGA. Altera verifies that the HardCopy II Companion Device timing requirements are met in the HardCopy Design Center.

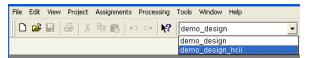

After you create your HardCopy II companion revision from your compiled Stratix II design, select the companion revision in the Quartus II software design revision drop-down box (Figure 5–12) or from the **Revisions** list. Compile the HardCopy II companion revision. After the Quartus II software compiles your design, you can perform a comparison check of the HardCopy II companion revision to the Stratix II prototype revision.

Figure 5–12. Changing Current Revision

#### Comparing HardCopy II and Stratix II Companion Revisions

Altera uses the companion revisions in a single Quartus II project to maintain the seamless migration of your design from a Stratix II FPGA to a HardCopy II structured ASIC. This methodology allows you to design with one set of Register Transfer Level (RTL) code to be used in both Stratix II FPGA and HardCopy II structured ASIC, guaranteeing functional equivalency.

When making changes to companion revisions, use the Compare HardCopy II Companion Revisions feature to ensure that your Stratix II design matches your HardCopy II design functionality and compilation settings. To compare companion revisions, on the Project menu, point to HardCopy II Utilities and click Compare HardCopy II Companion Revisions.

You must perform this comparison after both Stratix II and HardCopy II designs are compiled in order to hand off the design to Altera's HardCopy Design Center

The Comparison Revision Summary is found in the Compilation Report and identifies where assignments were changed between revisions or if there is a change in the logic resource count due to different compilation settings.

#### Generate HardCopy II Handoff Report

In order to submit a design to the HardCopy Design Center, you must generate a HardCopy II Handoff Report providing important information about the design that you want the HardCopy Design Center to review. To generate the HardCopy II Handoff Report, you must:

- Successfully compile both Stratix II and HardCopy II revisions of your design

- Successfully run the Compare HardCopy II Companion Revisions utility

Once you generate the HardCopy II Handoff Report, you can archive the design using the Archive HardCopy II Handoff Files utility described in "Archive HardCopy II Handoff Files" on page 5–29.

### Archive HardCopy II Handoff Files

The last step in the HardCopy II design methodology is to archive the HardCopy II project for submission to the HardCopy Design Center for back-end migration. The HardCopy II archive utility creates a different Quartus II Archive File than the standard Quartus II project archive

utility generates. This archive contains only the necessary data from the Quartus II project needed to implement the design in the HardCopy Design Center.

In order to use the **Archive HardCopy II Handoff Files** utility, you must complete the following:

- Compile both the Stratix II and HardCopy II revisions of your design

- Run the Compare HardCopy II Revisions utility

- Generate the HardCopy II Handoff Report

To select this option, on the Project menu, point to HardCopy II Utilities and click **Archive HardCopy II Handoff File** utility.

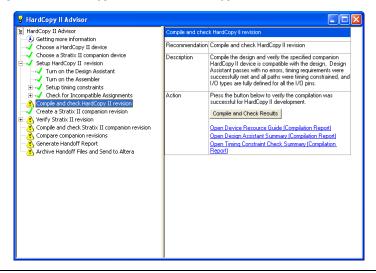

#### HardCopy II Advisor

The HardCopy II Advisor provides the list of tasks you should follow to develop your Stratix II prototype and your HardCopy II design. To run the HardCopy II Advisor, on the Project menu, point to HardCopy II Utilities and click **HardCopy II Advisor**. The following list highlights the checkpoints that the HardCopy II Advisor reviews. This list includes the major check points in the design process; it does not show every step in the process for completing your Stratix II and HardCopy II designs:

- 1. Select a Stratix II device.

- 2. Select a HardCopy II device.

- 3. Turn on the **Design Assistant**.

- 4. Set up timing constraints.

- 5. Check for incompatible assignments.

- 6. Compile and check the Stratix II design.

- 7. Create or overwrite the companion revision.

- 8. Compile and check the HardCopy II companion results.

- 9. Compare companion revisions.

- 10. Generate a Handoff Report.

- 11. Archive Handoff Files and send to Altera.

The HardCopy II Advisor shows the necessary steps that pertain to your current selected device. The Advisor shows a slightly different view for a design with Stratix II selected as compared to a design with HardCopy II selected.

In the Quartus II software, you can start designing with the HardCopy II device selected first, and build a Stratix II companion revision second. When you use this approach, the HardCopy II Advisor task list adjusts automatically to guide you from HardCopy II development through Stratix II FPGA prototyping, then completes the comparison archiving and handoff to Altera.

When your design uses the Stratix II FPGA as your starting point, Altera recommends following the Advisor guidelines for your Stratix II FPGA until you complete the prototype revision.

When the Stratix II FPGA design is complete, create and switch to your HardCopy II companion revision and follow the Advisor steps shown in that revision until you are finished with the HardCopy II revision and are ready to submit the design to Altera for back-end migration.

Each category in the HardCopy II Advisor list has an explanation of the recommended settings and constraints, as well as quick links to the features in the Quartus II software that are needed for each section. The HardCopy II Advisor displays:

- A green check box when you have successfully completed one of the steps

- A yellow caution sign for steps that must be completed before submitting your design to Altera for HardCopy development

- An information callout for items you must verify

Selecting an item within the HardCopy II flow menu provides a description of the task and recommended action. The view in the HardCopy II Advisor differs depending on the device you select.

Figure 5–13 shows the HardCopy II Advisor with the Stratix II device selected.

Figure 5-13. HardCopy II Advisor with Stratix II Selected

Figure 5–14 shows the HardCopy II Advisor with the HardCopy II device selected.

Figure 5-14. HardCopy II Advisor with HardCopy II Device Selected

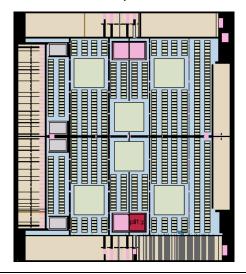

#### HardCopy II Floorplan View

The Quartus II software displays the preliminary timing closure floorplan and placement of your HardCopy II companion revision. This floorplan shows the preliminary placement and connectivity of all I/O pins, PLLs, memory blocks, HCell macros, and DSP HCell macros. Congestion mapping of routing connections can be viewed using the Layers Setting dialog box (in the View menu) settings. This is useful in analyzing densely packed areas of your floorplan that could be reducing the peak performance of your design. The HardCopy Design Center verifies final HCell macro timing and placement to guarantee timing closure is achieved.

Figure 5–15 shows an example of the HC230F1020 device floorplan.

Figure 5-15. HC230F1020 Device Floorplan

In this small example design, the logic is placed near the bottom edge. You can see the placement of a DSP block constructed of HCell Macros, various logic HCell Macros, and an M4K memory block. A labeled close-up view of this region is shown in Figure 5–16.

M4K Memory

Block

example\_ran.ram\_inst1|atsyncram.ram\_data\_rt1\_0|atsyncram\_

HCell Macros

Figure 5–16. Close-Up View of Floorplan

The HardCopy Design Center performs final placement and timing closure on your HardCopy II design based on the timing constraints provided in the Stratix II design.

For more information about the HardCopy Design Center's process, refer to the *Back-End Design Flow for HardCopy Series Devices* chapter in volume 1 of the *HardCopy Series Device Handbook*.

# **Conclusion**

You can use the Quartus II software to design HardCopy II devices and to develop prototypes using Stratix II FPGAs. This is done using the standard FPGA development process with the addition of the HardCopy II Device Resource Guide, HardCopy II Companion Devices assignment HardCopy II Utilities, and the HardCopy II Advisor.

The addition of the HardCopy II Advisor to the Quartus II software provides an instrumental development guide for you to complete your HardCopy II and Stratix II device designs. The HardCopy II Utilities included in the Quartus II software provide you with the tools necessary to complete your Stratix II FPGA prototype and HardCopy II structured ASIC design. The addition of the HardCopy II companion revisions feature to the process allows for rapid development and verification that your HardCopy II design is functionally equivalent to your Stratix II FPGA prototype.

# Document Revision History

Table 5–5 shows the revision history for this chapter.

| Table 5–5. Document Revision History |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date and Document<br>Version         | Changes Made                                                                                                                                                                                                                                                                        | Summary of Changes                                                                                                                                                                                                    |  |  |

| September 2008, v2.5                 | Updated chapter number and metadata.                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                     |  |  |

| June 2007 v2.4                       | Updated with the current Quartus II software version 7.1 information.                                                                                                                                                                                                               | _                                                                                                                                                                                                                     |  |  |

| December 2006<br>v2.3                | <ul> <li>Minor updates for the Quartus II software version 6.1.0</li> <li>Added "Performing ECOs with Change Manager and Chip Planner" and "Overall Migration Flow" sections.</li> <li>Updated "Quartus II Software Features Supported for HardCopy II Designs" section.</li> </ul> | A medium update to the chapter, due to changes in the Quartus II software version 6.1 release; most changes were in the "Performing ECOs with Change Manager and Chip Planner" and "Overall Migration Flow" sections. |  |  |

| May 2006, v2.2                       | Added information on support for HardCopy II devices in version 6.0 of the Quartus II software.                                                                                                                                                                                     | _                                                                                                                                                                                                                     |  |  |

| March 2006                           | Formerly chapter 18; no content change.                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                     |  |  |

| October 2005 v2.1                    | <ul> <li>Moved Chapter 17 Quartus II Support for HardCopy II         Devices to Chapter 18 in Hardcopy Series Device         Handbook 3.2.</li> <li>Updated Graphics.</li> <li>Updated technical content for Quartus II 5.1 support of         HardCopy II devices.</li> </ul>      | _                                                                                                                                                                                                                     |  |  |

| May 2005<br>v2.0                     | Added information on support for HardCopy II devices in version 5.0 of the Quartus II software.                                                                                                                                                                                     | _                                                                                                                                                                                                                     |  |  |

| January 2005<br>v1.0                 | Added document to the HardCopy Series Handbook.                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                     |  |  |