# **FIR Compiler**

# **User Guide**

The FIR Compiler is scheduled for product obsolescence and discontinued support as described in PDN1306. Therefore, Altera does not recommend use of this IP in new designs. For more information about Altera's current IP offering, refer to Altera's Intellectual Property website.

101 Innovation Drive San Jose, CA 95134 www.altera.com

Software Version: **Document Date:** May 2011

11.0

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter 1. About the FIR Compiler                                                                                                                                                                                                                                                                   |                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Features                                                                                                                                                                                                                                                                                            | 1–3                                      |

| Release Information                                                                                                                                                                                                                                                                                 |                                          |

| Device Family Support                                                                                                                                                                                                                                                                               |                                          |

| MegaCore Verification                                                                                                                                                                                                                                                                               |                                          |

| Performance and Resource Utilization                                                                                                                                                                                                                                                                |                                          |

| Installation and Licensing                                                                                                                                                                                                                                                                          |                                          |

| OpenCore Plus Evaluation                                                                                                                                                                                                                                                                            |                                          |

| OpenCore Plus Time-Out Behavior                                                                                                                                                                                                                                                                     |                                          |

| Chapter 2. Getting Started                                                                                                                                                                                                                                                                          |                                          |

| Design Flows                                                                                                                                                                                                                                                                                        |                                          |

| DSP Builder Flow                                                                                                                                                                                                                                                                                    |                                          |

| MegaWizard Plug-In Manager Flow                                                                                                                                                                                                                                                                     |                                          |

| Parameterize the MegaCore Function                                                                                                                                                                                                                                                                  |                                          |

| Generate the MegaCore Function                                                                                                                                                                                                                                                                      |                                          |

| Simulate the Design                                                                                                                                                                                                                                                                                 |                                          |

| Simulating in ModelSim                                                                                                                                                                                                                                                                              |                                          |

| Simulating in MATLAB                                                                                                                                                                                                                                                                                |                                          |

| Simulating in Third-Party Simulation Tools Using NativeLink                                                                                                                                                                                                                                         |                                          |

| Compile the Design and Program a Device                                                                                                                                                                                                                                                             |                                          |

| Chapter 3. Parameter Settings  Specifying the Coefficients  Using the FIR Compiler Coefficient Generator  Loading Coefficients from a File  Analyzing the Coefficients  Specify the Input and Output Specifications  Specify the Architecture Specification  Resource Estimates  Filter Design Tips | 3-2<br>3-6<br>3-8<br>3-9<br>3-11<br>3-16 |

| Chapter 4. Functional Description                                                                                                                                                                                                                                                                   |                                          |

| FIR Compiler I Find Print Provider                                                                                                                                                                                                                                                                  |                                          |

| Number Systems and Fixed-Point Precision                                                                                                                                                                                                                                                            |                                          |

| Generating or Importing Coefficients                                                                                                                                                                                                                                                                |                                          |

| Coefficient Scaling                                                                                                                                                                                                                                                                                 |                                          |

| Symmetrical Architecture Selection                                                                                                                                                                                                                                                                  |                                          |

| Symmetrical Serial                                                                                                                                                                                                                                                                                  |                                          |

| Coefficient Reloading and Reordering                                                                                                                                                                                                                                                                |                                          |

| Structure Types                                                                                                                                                                                                                                                                                     |                                          |

| Multicycle Variable Structures                                                                                                                                                                                                                                                                      |                                          |

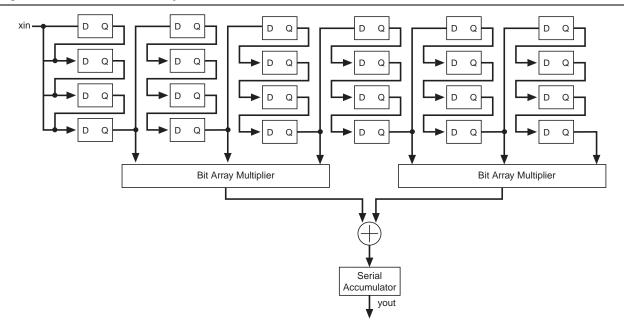

| Parallel Structures                                                                                                                                                                                                                                                                                 |                                          |

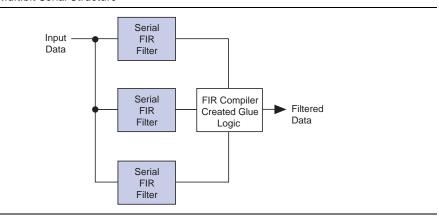

| Serial Structures                                                                                                                                                                                                                                                                                   |                                          |

| Multibit Serial Structure                                                                                                                                                                                                                                                                           |                                          |

| Multichannel Structures                                                                                                                                                                                                                                                                             |                                          |

iv Contents

| Leternal attenues I Destruction                                    | 4 0    |

|--------------------------------------------------------------------|--------|

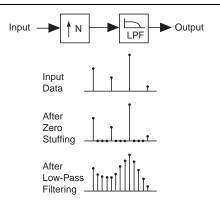

| Interpolation and Decimation                                       |        |

| Implementation Details for Interpolation and Decimation Structures |        |

| Availability of Interpolation and Decimation Filters               |        |

| Half-Band Decimation Filters                                       |        |

| Symmetric-Interpolation Filters                                    |        |

| Pipelining                                                         |        |

| Simulation Output                                                  | 4–13   |

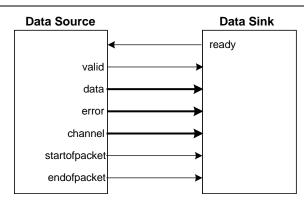

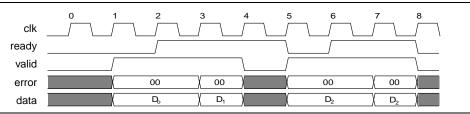

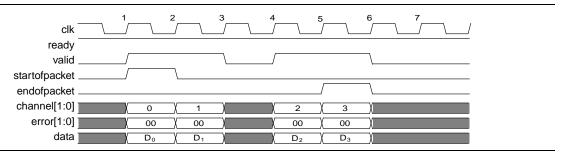

| Avalon Streaming Interface                                         | 4–13   |

| Avalon-ST Data Transfer Timing                                     |        |

| Packet Data Transfers                                              |        |

| Signals                                                            |        |

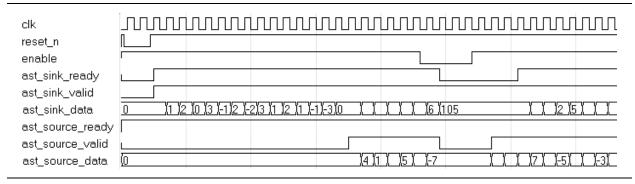

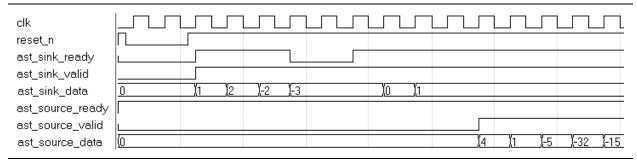

| Timing Diagrams                                                    |        |

| Reset and Global Clock Enable Operations                           |        |

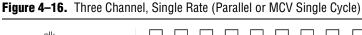

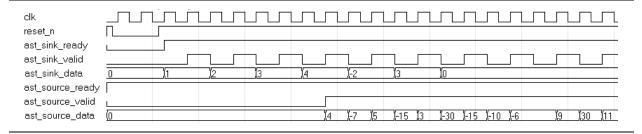

| Single Rate Filter Timing Diagram                                  |        |

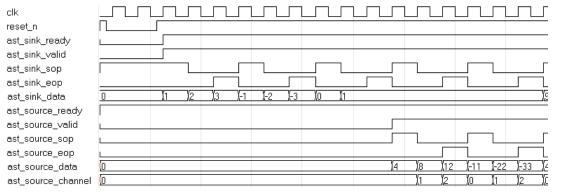

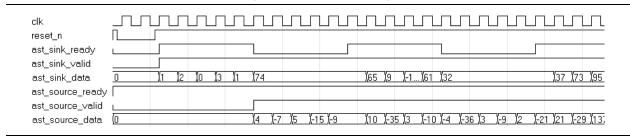

| Interpolation Filter Timing Diagrams                               |        |

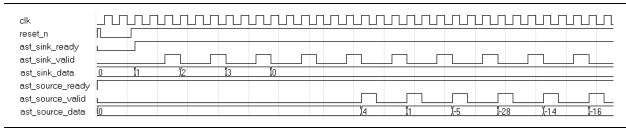

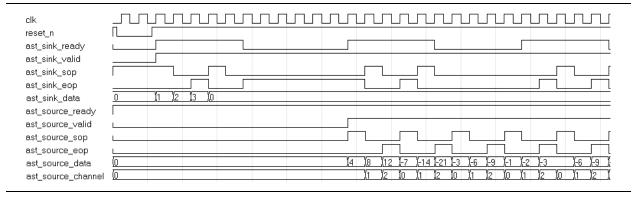

| Decimation Filter Timing Diagrams                                  |        |

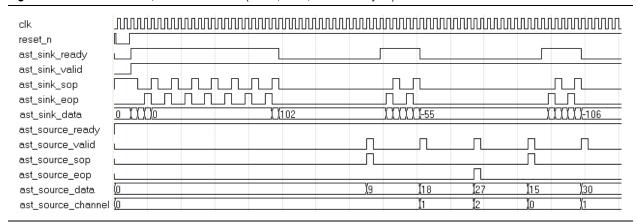

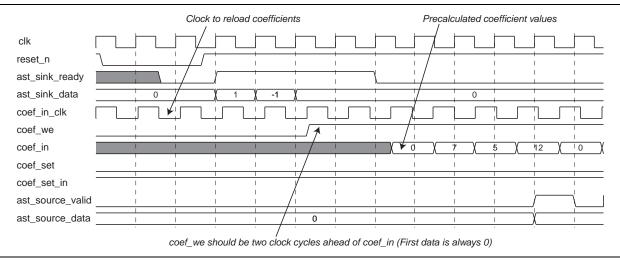

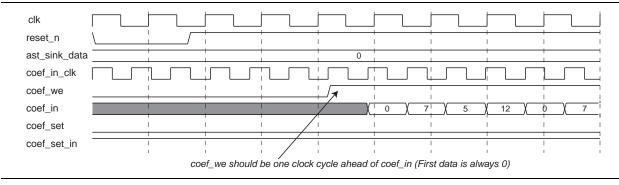

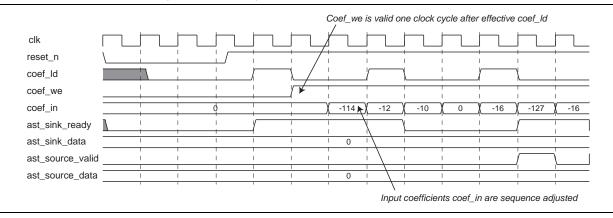

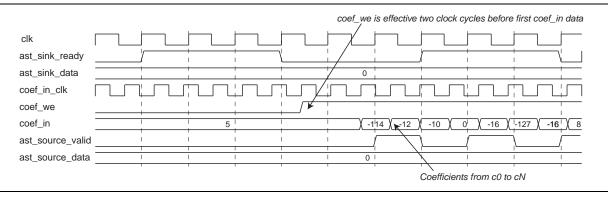

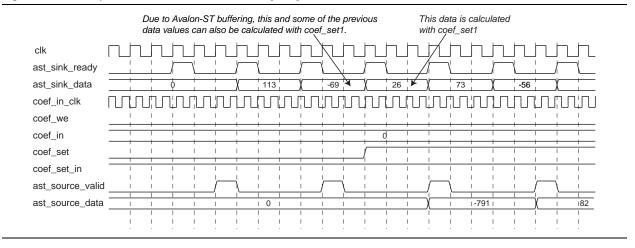

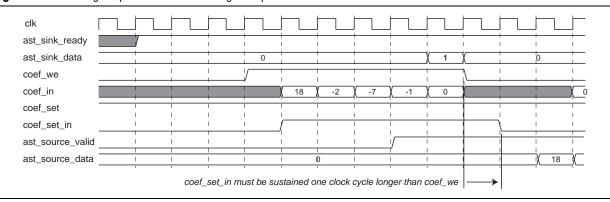

| Coefficient Reloading Timing Diagrams                              |        |

| Referenced Documents                                               |        |

| Referenced Documents                                               | 20     |

| Appendix A. FIR Compiler Supported Device Structures               |        |

|                                                                    | A 1    |

| Supported Device Structures                                        |        |

| Support for HardCopy Series Devices                                |        |

| Compiling HardCopy Designs                                         | A-3    |

|                                                                    |        |

| Additional Information                                             |        |

| Revision History                                                   |        |

| How to Contact Altera                                              |        |

| Typographic Conventions                                            | Info-2 |

# 1. About the FIR Compiler

This document describes the Altera® FIR Compiler. The Altera FIR Compiler provides a fully integrated finite impulse response (FIR) filter development environment optimized for use with Altera FPGA devices.

You can use the Altera IP Toolbench interface with the Altera FIR Compiler to implement a variety of filter architectures, including fully parallel, serial, or multibit serial distributed arithmetic, and multicycle fixed/variable filters. The FIR Compiler includes a coefficient generator.

Traditionally, designers have been forced to make a trade-off between the flexibility of digital signal processors and the performance of ASICs and application-specific standard product (ASSPs) digital signal processing (DSP) solutions. The Altera DSP solution reduces the need for this trade-off by providing exceptional performance combined with the flexibility of FPGAs.

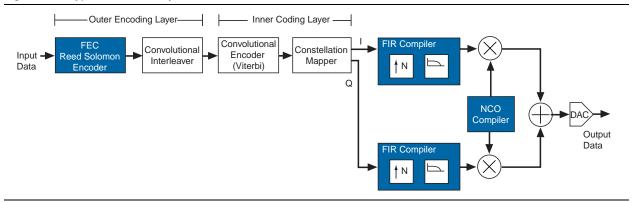

Figure 1–1 shows a typical DSP system that uses Altera IP cores, including the FIR Compiler and other DSP IP cores.

Figure 1–1. Typical Modulator System

Many digital systems use signal filtering to remove unwanted noise, to provide spectral shaping, or to perform signal detection or analysis. Two types of filters that provide these functions are finite impulse response (FIR) filters and infinite impulse response (IIR) filters. Typical filter applications include signal preconditioning, band selection, and low-pass filtering.

In contrast to IIR filters, FIR filters have a linear phase and inherent stability. This benefit makes FIR filters attractive enough to be designed into a large number of systems. However, for a given frequency response, FIR filters are a higher order than IIR filters, making FIR filters more computationally expensive.

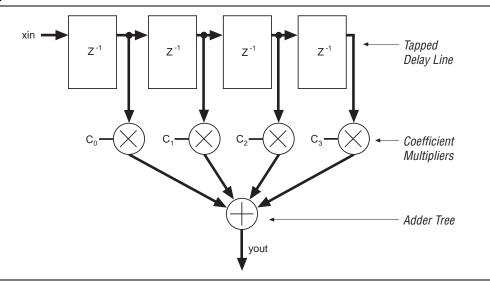

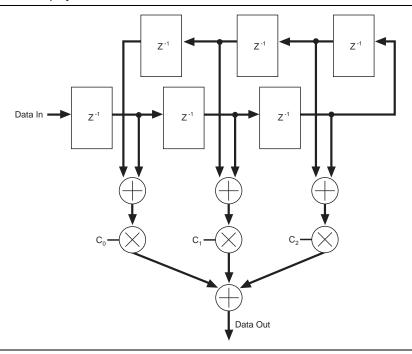

The structure of a FIR filter is a weighted, tapped delay line as shown in Figure 1–2.

Figure 1-2. Basic FIR Filter

The filter design process involves identifying coefficients that match the frequency response specified for the system. These coefficients determine the response of the filter. You can change the signal frequencies that pass through the filter by changing the coefficient values or adding more coefficients.

DSP processors have a limited number of multiply accumulators (MACs), and require many clock cycles to compute each output value (the number of cycles is directly related to the order of the filter).

A dedicated hardware solution can achieve one output per clock cycle. A fully parallel, pipelined FIR filter implemented in an FPGA can operate at very high data rates, making FPGAs ideal for high-speed filtering applications.

Table 1–1 compares resource usage and performance for different implementations of a 120-tap FIR filter with a 12-bit data input bus.

**Table 1–1.** FIR Filter Implementation Comparison (*Note 1*)

| Device        | Implementation    | Clock Cycles to<br>Compute Result |

|---------------|-------------------|-----------------------------------|

| DSP processor | 1 MAC             | 120                               |

| FPGA          | 1 serial filter   | 12                                |

|               | 1 parallel filter | 1                                 |

#### Note to Table 1-1:

(1) If you use the FIR Compiler to create a filter, you can also implement a variable filter in a FPGA that uses from 1 to 120 MACs, and 120 to 1 clock cycles.

The Altera FIR Compiler speeds the design cycle by:

- Generating the coefficients needed to design custom FIR filters.

- Generating bit-accurate and clock-cycle-accurate FIR filter models (also known as bit-true models) in the Verilog HDL and VHDL languages and in the MATLAB environment.

- Automatically generating the code required for the Quartus II software to synthesize high-speed, area-efficient FIR filters of various architectures.

- Generating a VHDL testbench for all architectures.

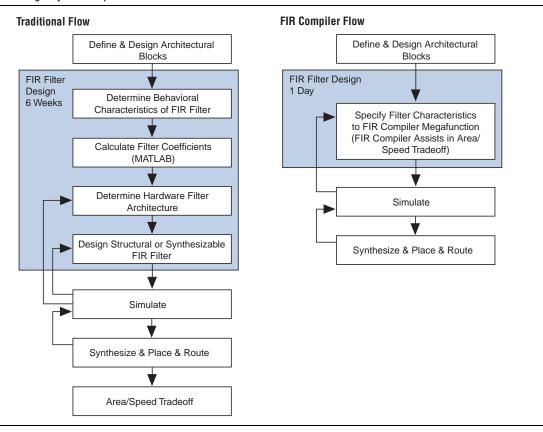

Figure 1–3 compares the design cycle using a FIR Compiler with a traditional implementation.

Figure 1-3. Design Cycle Comparison

## **Features**

The Altera® FIR Compiler implements a finite impulse response (FIR) filter MegaCore function and supports the following features:

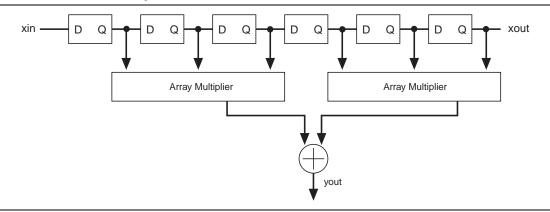

- The following hardware architectures are supported to enable optimal trade- offs between logic, memory, DSP blocks, and performance:

- Fully parallel distributed arithmetic

- Fully serial distributed arithmetic

- Multibit serial distributed arithmetic

- Multicycle variable structures

- Exploit maximal efficiency designs as a result of FIR Compiler hardware optimizations such as interpolation, decimation, symmetry, decimation half-band, and time sharing.

- Easy system integration using Avalon® Streaming (Avalon-ST) interfaces.

- Precision control of chip resource utilization:

- Logic cells, M512, M4K, M-RAM, MLAB, M9K, or M144K for data storage.

- M512, M4K, M9K, M20K, MLAB or logic cells for coefficient storage.

- Includes a resource estimator.

- Support for run-time coefficient reloading capability and multiple coefficient sets.

- Includes a built-in coefficient generator to enable efficient design space exploration.

- User-selectable output precision via rounding and saturation.

- DSP Builder ready.

### **Release Information**

Table 1–2 provides information about this release of the Altera® FIR Compiler.

Table 1-2. FIR Compiler Release Information

| Item          | Description |

|---------------|-------------|

| Version       | 11.0        |

| Release Date  | May 2011    |

| Ordering Code | IP-FIR      |

| Product ID    | 0012        |

| Vendor ID     | 6AF7        |

For more information about this release, refer to the *MegaCore IP Library Release Notes* and *Errata*.

Altera verifies that the current version of the Quartus® II software compiles the previous version of each MegaCore® function. The *MegaCore IP Library Release Notes and Errata* report any exceptions to this verification. Altera does not verify compilation with MegaCore function versions older than one release.

# **Device Family Support**

Table 1–3 defines the device support levels for Altera IP cores.

Table 1-3. Altera IP Core Device Support Levels

| FPGA Device Families                                                                                                                                                                                                                                                     | HardCopy Device Families                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary support—The IP core is verified with preliminary timing models for this device family. The IPcore meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution. | HardCopy Companion—The IP core is verified with preliminary timing models for the HardCopy companion device. The IP core meets all functional requirements, but might still be undergoing timing analysis for the HardCopy device family. It can be used in production designs with caution. |

| Final support—The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                             | HardCopy Compilation—The IP core is verified with final timing models for the HardCopy device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                                  |

Table 1–4 shows the level of support offered by the FIR Compiler to each Altera device family.

Table 1-4. Device Family Support

| Device Family         | Support              |

|-----------------------|----------------------|

| Arria™ GX             | Final                |

| Arria II GX           | Final                |

| Arria II GZ           | Final                |

| Cyclone®              | Final                |

| Cyclone II            | Final                |

| Cyclone III           | Final                |

| Cyclone III LS        | Final                |

| Cyclone IV GX         | Final                |

| HardCopy® II          | HardCopy Compilation |

| HardCopy III          | HardCopy Compilation |

| HardCopy IV E         | HardCopy Compilation |

| HardCopy IV GX        | HardCopy Compilation |

| Stratix®              | Final                |

| Stratix II            | Final                |

| Stratix II GX         | Final                |

| StratixIII            | Final                |

| Stratix IV GT         | Final                |

| Stratix IV GX/E       | Final                |

| Stratix V             | Preliminary          |

| Stratix GX            | Final                |

| Other device families | No support           |

# **MegaCore Verification**

Before releasing an updated version of the FIR Compiler, Altera runs a comprehensive regression test to verify its quality and correctness.

All features and architectures are tested by sweeping all parameter options and verifying that the simulation matches a master functional model.

### **Performance and Resource Utilization**

This section shows typical expected performance for a FIR Compiler MegaCore function with Cyclone III and Stratix IV devices. All figures are given for a FIR filter with 97 taps, 8-bit input data, 14-bit coefficients, a target  $f_{MAX}$  set to 1 GHz.

Cyclone III devices use combinational look-up tables (LUTs) and logic registers; Stratix IV devices use combinational adaptive look-up tables (ALUTs) and logic registers.

The resource and performance data was generated with the source ready signal (ast\_source\_ready) always driven high, as described in "Avalon Streaming Interface" on page 4–13.

Table 1–5 shows performance figures for Cyclone III devices:

Table 1-5. FIR Compiler Performance—Cyclone III Devices (Part 1 of 2)

| O a mala mala mala                                       | •                                                        | Memo             | ory <i>(6)</i>    | B# 4: :              | BAILIII                   | B4 - 14' - 1'        |                                  | T1 | Processing |

|----------------------------------------------------------|----------------------------------------------------------|------------------|-------------------|----------------------|---------------------------|----------------------|----------------------------------|----|------------|

| Combinational<br>LUTs                                    | Logic<br>Registers                                       | Bits             | М9К               | Multipliers<br>(9x9) | f <sub>max</sub><br>(MHz) | Throughput<br>(MSPS) | Equivalent<br>(GMACs) <i>(1)</i> |    |            |

| Multibit Serial, p                                       | ipeline level 1 (                                        | (2), (3)         |                   |                      |                           |                      |                                  |    |            |

| 899                                                      | 1,331                                                    | 55,148           | 31                | _                    | 310                       | 62                   | 6                                |    |            |

| Multicycle variat                                        | ole (1 cycle) dec                                        | cimation by 4, p | ipeline level 1 ( | (2), (3)             |                           |                      |                                  |    |            |

| 857                                                      | 1,336                                                    | 1,158            | 12                | 26                   | 281                       | 281                  | 27                               |    |            |

| Multicycle variat                                        | ole (1 cycle) inte                                       | erpolation by 4, | pipeline level 2  | (4)                  |                           |                      |                                  |    |            |

| 1,528                                                    | 2,657                                                    | 66               | 1                 | 50                   | 290                       | 290                  | 28                               |    |            |

| Multicycle variat                                        | Multicycle variable (1 cycle), pipeline level 2 (2), (4) |                  |                   |                      |                           |                      |                                  |    |            |

| 2,543                                                    | 4,837                                                    | 92               | 1                 | 98                   | 280                       | 280                  | 27                               |    |            |

| Multicycle variable (4 cycle), pipeline level 2 (2), (3) |                                                          |                  |                   |                      |                           |                      |                                  |    |            |

| 1,182                                                    | 1,715                                                    | 578              | 9                 | 26                   | 283                       | 71                   | 7                                |    |            |

**Table 1–5.** FIR Compiler Performance—Cyclone III Devices (Part 2 of 2)

| O ambination al                           | 1                                       | Memory (6) |     |                      | Multipliana               |                      | Thursday                         | Processing |

|-------------------------------------------|-----------------------------------------|------------|-----|----------------------|---------------------------|----------------------|----------------------------------|------------|

| Combinational<br>LUTs                     | Logic<br>Registers                      | Bits       | М9К | Multipliers<br>(9x9) | T <sub>max</sub><br>(MHz) | Throughput<br>(MSPS) | Equivalent<br>(GMACs) <i>(1)</i> |            |

| Parallel (LE), pip                        | Parallel (LE), pipeline level 1(2), (3) |            |     |                      |                           |                      |                                  |            |

| 3,416                                     | 3,715                                   | 208        | 3   | _                    | 288                       | 288                  | 28                               |            |

| Parallel (M9K), pipeline level 1 (2), (5) |                                         |            |     |                      |                           |                      |                                  |            |

| 1,948                                     | 2,155                                   | 120,030    | 48  | _                    | 283                       | 283                  | 27                               |            |

| Serial (M9K), pipeline level 1 (2), (3)   |                                         |            |     |                      |                           |                      |                                  |            |

| 327                                       | 462                                     | 14,167     | 8   | _                    | 323                       | 36                   | 3                                |            |

#### Notes to Table 1-5:

- (1) GMAC = giga multiply accumulates per second (1 giga = 1,000 million).

- (2) This FIR filter takes advantage of symmetric coefficients.

- (3) Using EP3C10F256C6 devices.

- (4) Using EP3C16F484C6 devices.

- (5) Using EP3C40F780C6 devices.

- (6) It may be possible to significantly reduce memory utilization by setting a lower target f<sub>MAX</sub>.

Table 1–6 shows performance figures for Stratix IV devices:

Table 1-6. FIR Compiler Performance—Stratix IV Devices

| 0                                    |                          | Memory        |             | B4-12-11      | _                      | <b>TL</b>                 | Processing           |                           |

|--------------------------------------|--------------------------|---------------|-------------|---------------|------------------------|---------------------------|----------------------|---------------------------|

| Combinational<br>ALUTs               | Logic<br>Registers       | Bits          | (M9K)       | ALUTs         | Multipliers<br>(18x18) | t <sub>max</sub><br>(MHz) | Throughput<br>(MSPS) | Equivalent<br>(GMACS) (1) |

| Multibit Serial, p                   | ipeline level 1 (        | (2), (3), (4) |             | •             | <u> </u>               |                           | •                    | <u> </u>                  |

| 766                                  | 1,166                    | 55,276        | 42          | 16            | _                      | 503                       | 101                  | 10                        |

| Multicycle variat                    | ole (1 cycle) de         | cimation by   | 4, pipeline | e level 1 (2) | ), (3)                 |                           | •                    | •                         |

| 336                                  | 844                      | 1,400         | 16          | 28            | 14                     | 443                       | 443                  | 43                        |

| Multicycle variat                    | ole (1 cycle) int        | erpolation b  | y 4, pipeli | ne level 2 (  | (3)                    |                           | •                    | •                         |

| 200                                  | 1,274                    | 64            | _           | 8             | 24                     | 372                       | 372                  | 36                        |

| Multicycle variat                    | ole (1 cycle), pi        | peline level  | 2 (2), (3)  |               |                        |                           | 1                    | •                         |

| 741                                  | 1,936                    | 148           | 1           | 8             | 48                     | 443                       | 443                  | 43                        |

| Multicycle variat                    | ole (4 cycle), pi        | peline level  | 2 (2), (3)  |               |                        |                           | •                    | •                         |

| 717                                  | 1,398                    | 796           | 6           | 36            | 14                     | 323                       | 81                   | 8                         |

| Parallel (LE), pip                   | eline level 1 <i>(2)</i> | ), (3)        |             |               |                        |                           | •                    | •                         |

| 2,153                                | 2,672                    | 157           | 1           | 8             | _                      | 421                       | 421                  | 41                        |

| Parallel (M9K), pipeline level 1 (3) |                          |               |             |               |                        |                           |                      |                           |

| 821                                  | 1,730                    | 119,872       | 45          | 8             | _                      | 457                       | 457                  | 44                        |

| Serial (M9K), pip                    | peline level 1 (2        | 2), (3)       |             | -             |                        |                           | •                    |                           |

| 245                                  | 415                      | 14,231        | 11          | 8             | _                      | 523                       | 58                   | 6                         |

#### Notes to Table 1-6:

- (1) GMAC = giga multiply accumulates per second (1 giga = 1,000 million).

- (2) This FIR filter takes advantage of symmetric coefficients.

- (3) Using EP4SGX70DF29C2X devices.

- (4) The data width is 16-bits and there are 4 serial units.

# **Installation and Licensing**

The FIR Compiler MegaCore function is part of the MegaCore® IP Library, which is distributed with the Quartus® II software and downloadable from the Altera® website, www.altera.com.

For system requirements and installation instructions, refer to the *Altera Software Installation and Licensing* manual.

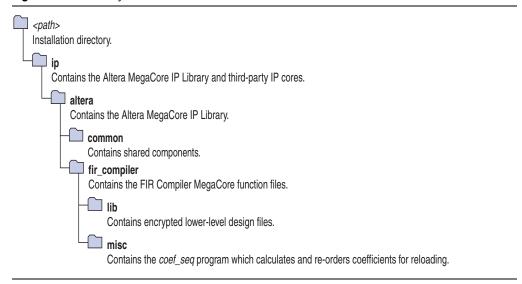

Figure 1–4 shows the directory structure after you install the FIR Compiler, where *<path>* is the installation directory for the Quartus II software. The default installation directory on Windows is **c:\altera**\<*version>* and on Linux is */opt/altera*<*version>*.

Figure 1-4. Directory Structure

### **OpenCore Plus Evaluation**

With Altera's free OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a megafunction (Altera MegaCore function or AMPP<sup>SM</sup> megafunction) within your system.

- Verify the functionality of your design, as well as evaluate its size and speed quickly and easily.

- Generate time-limited device programming files for designs that include megafunctions.

- Program a device and verify your design in hardware.

You only need to purchase a license for the FIR Compiler when you are completely satisfied with its functionality and performance, and want to take your design to production.

After you purchase a license, you can request a license file from the Altera website at **www.altera.com/licensing** and install it on your computer. When you request a license file, Altera emails you a **license.dat** file. If you do not have Internet access, contact your local Altera representative.

For more information about OpenCore Plus hardware evaluation, refer to *AN320: OpenCore Plus Evaluation of Megafunctions*.

## **OpenCore Plus Time-Out Behavior**

OpenCore Plus hardware evaluation supports the following operation modes:

- *Untethered*—the design runs for a limited time.

- Tethered—requires a connection between your board and the host computer. If tethered mode is supported by all megafunctions in a design, the device can operate for a longer time or indefinitely.

All megafunctions in a device time-out simultaneously when the most restrictive evaluation time is reached. If there is more than one megafunction in a design, a specific megafunction's time-out behavior might be masked by the time-out behavior of the other megafunctions.

The untethered timeout for the FIR Compiler MegaCore function is one hour; the tethered timeout value is indefinite.

The data output signal is forced to zero when the hardware evaluation time expires.

# 2. Getting Started

# **Design Flows**

The FIR Compiler MegaCore® function supports the following design flows:

- **DSP Builder**: Use this flow if you want to create a DSP Builder model that includes a FIR Compiler MegaCore function variation.

- MegaWizard<sup>TM</sup> Plug-In Manager: Use this flow if you would like to create a FIR Compiler MegaCore function variation that you can instantiate manually in your design.

This chapter describes how you can use a FIR Compiler MegaCore function in either of these flows. The parameterization is the same in each flow and is described in Chapter 3, Parameter Settings.

After parameterizing and simulating a design in either of these flows, you can compile the completed design in the Quartus II software.

### **DSP Builder Flow**

Altera's DSP Builder product shortens digital signal processing (DSP) design cycles by helping you create the hardware representation of a DSP design in an algorithm-friendly development environment.

DSP Builder integrates the algorithm development, simulation, and verification capabilities of The MathWorks MATLAB® and Simulink® system-level design tools with Altera Quartus® II software and third-party synthesis and simulation tools. You can combine existing Simulink blocks with Altera DSP Builder blocks and MegaCore function variation blocks to verify system level specifications and perform simulation.

In DSP Builder, a Simulink symbol for the FIR Compiler appears in the **MegaCore Functions** library of the **Altera DSP Builder Blockset** in the Simulink library browser.

You can use the FIR Compiler in the MATLAB/Simulink environment by performing the following steps:

- 1. Create a new Simulink model.

- 2. Select the FIR Compiler block from the **MegaCore Functions** library in the Simulink Library Browser, add it to your model, and give the block a unique name.

- 3. Double-click the FIR Compiler block in your model to display IP Toolbench and click **Step 1: Parameterize** to parameterize a FIR Compiler MegaCore function variation. For an example of how to set parameters for the FIR Compiler block, refer to Chapter 3, Parameter Settings.

- 4. Click **Step 2: Generate** in IP Toolbench to generate your FIR Compiler MegaCore function variation. For information about the generated files, refer to Table 2–1 on page 2–6.

- 5. Connect your FIR Compiler MegaCore function variation block to the other blocks in your model.

Simulate the FIR Compiler MegaCore function variation in your DSP Builder model.

When you are using the DSP Builder flow, device selection, simulation, Quartus II compilation and device programming are all controlled within the DSP Builder environment.

DSP Builder supports integration with SOPC Builder using Avalon® Memory-Mapped (Avalon-MM) master or slave, and Avalon Streaming (Avalon-ST) source or sink interfaces.

For more information about these interface types, refer to the *Avalon Interface Specifications*.

# **MegaWizard Plug-In Manager Flow**

The MegaWizard Plug-in Manager flow allows you to customize a FIR Compiler MegaCore function, and manually integrate the MegaCore function variation into a Quartus II design.

To launch the MegaWizard Plug-in Manager, perform the following steps:

- 1. Create a new project using the **New Project Wizard** available from the File menu in the Quartus II software.

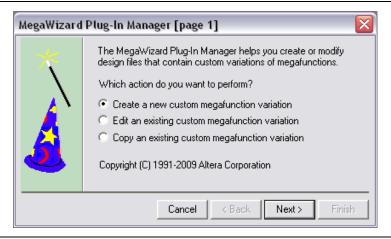

- 2. Launch **MegaWizard Plug-in Manager** from the Tools menu, and select the option to create a new custom megafunction variation (Figure 2–1).

Figure 2–1. MegaWizard Plug-In Manager

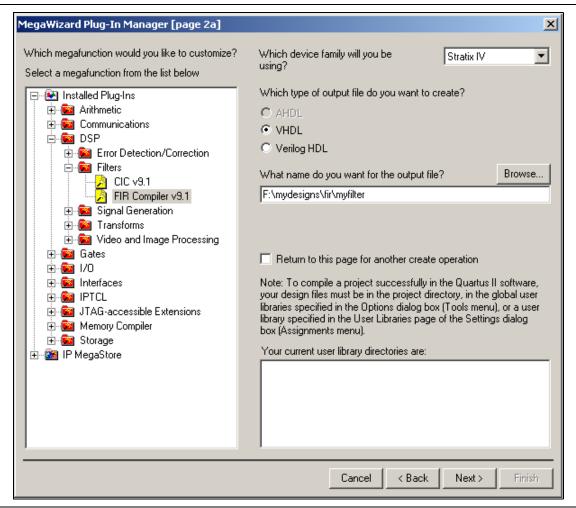

3. Click **Next** and select **FIR Compiler** < *version*> from the **DSP>Filters** section in the **Installed Plug-Ins** tab. (Figure 2–2).

Figure 2–2. Selecting the MegaCore Function

- 4. Verify that the device family is the same as you specified in the **New Project Wizard**.

- 5. Select the top-level output file type for your design; the wizard supports VHDL and Verilog HDL.

- 6. Specify the top level output file name for your MegaCore function variation and click **Next** to launch IP Toolbench (Figure 2–3 on page 2–4).

### Parameterize the MegaCore Function

To parameterize your MegaCore function variation, perform the following steps:

Click Step 1: Parameterize in IP Toolbench to display the Parameterize - FIR

Compiler window. Use this interface to specify the required parameters for the

MegaCore function variation. For an example of how to set parameters for the FIR

Compiler MegaCore function, refer to Chapter 3, Parameter Settings.

Figure 2–3. IP Toolbench—Parameterize

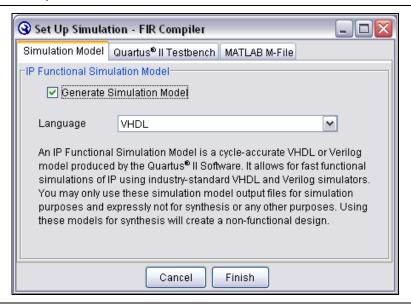

2. Click **Step 2: Setup Simulation** in IP Toolbench to display the **Set Up Simulation** - **FIR Compiler** page (Figure 2–4).

Figure 2–4. Set Up Simulation

3. Turn on Generate Simulation Model to create an IP functional model.

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software.

Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a non-functional design.

- 4. Select the required language from the Language list.

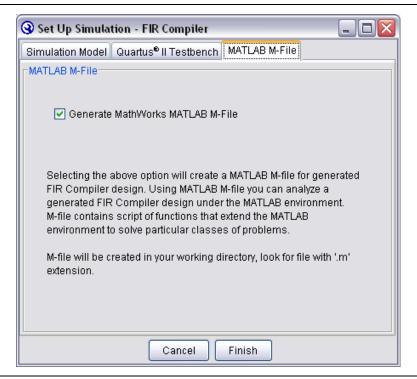

- 5. Click the **MATLAB M-File** tab on the **Set Up Simulation** page (Figure 2–5).

- 6. Turn on the Generate MathWorks MATLAB M-File option.

This option generates a MATLAB m-file script that contains functions you can use to analyze a FIR Compiler design in the MATLAB environment. A testbench is also generated.

Figure 2-5. Create a MATLAB M-File

#### 7. Click Finish.

The **Quartus II Testbench** tab contains an option that is not used in this version of the FIR Compiler and should be ignored.

### **Generate the MegaCore Function**

To generate your MegaCore function variation, perform the following steps:

1. Click **Step 3: Generate** in IP Toolbench to generate your MegaCore function variation and supporting files. The generation phase may take several minutes to complete. The generation progress and status is displayed in a report window.

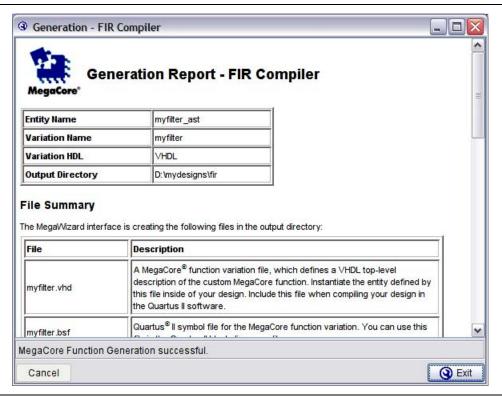

Figure 2–6 shows the generation report.

**Figure 2–6.** Generation Report - FIR Compiler MegaCore Function

Table 2–1 describes the IP Toolbench-generated files and other files that may be in your project directory. The names and types of files specified in the report vary based on whether you created your design with VHDL or Verilog HDL.

**Table 2–1.** Generated Files (Part 1 of 2) (Note 1),(2)

| Filename                             | Description                                                                                                                                                                                                                                                                               |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <entity name="">.vhd</entity>        | A VHDL wrapper file for the Avalon-ST interface.                                                                                                                                                                                                                                          |

| <variation name="">.bsf</variation>  | A Quartus II block symbol file for the MegaCore function variation. You can use this file in the Quartus II block diagram editor.                                                                                                                                                         |

| <variation name="">.cmp</variation>  | A VHDL component declaration file for the MegaCore function variation. Add the contents of this file to any VHDL architecture that instantiates the MegaCore function.                                                                                                                    |

| <variation name="">.html</variation> | A MegaCore function report file in hypertext markup language format.                                                                                                                                                                                                                      |

| <variation name="">.qip</variation>  | A single Quartus II IP file is generated that contains all of the assignments and other information required to process your MegaCore function variation in the Quartus II compiler. You are prompted to add this file to the current Quartus II project when you exit from IP Toolbench. |

**Table 2–1.** Generated Files (Part 2 of 2) (Note 1),(2)

| Filename                                                    | Description                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <variation name="">.vec</variation>                         | Quartus II vector file. This file provides simulation test vectors to be used for simulating the customized FIR MegaCore function variation with the Quartus II software.                                                                                                  |

| <variation name="">.vhd or .v</variation>                   | A VHDL or Verilog HDL file that defines a VHDL or Verilog HDL top-level description of the custom MegaCore function variation. Instantiate the entity defined by this file inside of your design. Include this file when compiling your design in the Quartus II software. |

| <variation name="">.vho or .vo</variation>                  | A VHDL or Verilog HDL output file that defines the IP functional simulation model.                                                                                                                                                                                         |

| <variation name="">_bb.v</variation>                        | A Verilog HDL black-box file for the MegaCore function variation. Use this file when using a third-party EDA tool to synthesize your design.                                                                                                                               |

| <pre><variation name="">_coef_in_mlab.txt</variation></pre> | Text files that provides coefficient inputs for the MATLAB testbench model.                                                                                                                                                                                                |

| <pre><variation name="">_coef_int.txt</variation></pre>     |                                                                                                                                                                                                                                                                            |

| <pre><variation name="">_coef_n_inv.hex</variation></pre>   | Memory initialization files in INTEL Hex format. These files are required both for                                                                                                                                                                                         |

| <pre><variation name="">_coef_n.hex</variation></pre>       | simulation with IP functional simulation models and synthesis using the Quartus II software.                                                                                                                                                                               |

| <variation name="">_zero.hex</variation>                    | Software.                                                                                                                                                                                                                                                                  |

| <variation name="">_constraints.tcl</variation>             | Constraints setting Tcl file for Quartus II synthesis. This file contains the necessary constraints to achieve FIR Filter size and speed.                                                                                                                                  |

| <variation name="">_input.txt</variation>                   | This text file provides simulation data for the MATLAB model and the simulation testbench.                                                                                                                                                                                 |

| <variation name="">_mlab.m</variation>                      | This MATLAB M-File provides the kernel of the MATLAB simulation model for the customized FIR MegaCore function variation.                                                                                                                                                  |

| <variation name="">_model.m</variation>                     | This MATLAB M-File provides a MATLAB simulation model for the customized FIR MegaCore function variation.                                                                                                                                                                  |

| <variation name="">_msim.tcl</variation>                    | This Tcl script can be used to simulate the VHDL testbench together with the simulation model of the customized FIR MegaCore function variation.                                                                                                                           |

| <variation name="">_nativelink.tcl</variation>              | A Tcl script that can be used to assign NativeLink simulation testbench settings to the Quartus II project.                                                                                                                                                                |

| <variation name="">_param.txt</variation>                   | This text file records all output parameters for customized FIR MegaCore function variation.                                                                                                                                                                               |

| <pre><variation name="">_silent_param.txt</variation></pre> | This text file records all input parameters for customized FIR MegaCore function variation.                                                                                                                                                                                |

| <variation name="">_core.vhd</variation>                    | Generated FIR Filter netlists. These files are required for Quartus II synthesis and are                                                                                                                                                                                   |

| <variation name="">_st.v</variation>                        | added to your current Quartus II project.                                                                                                                                                                                                                                  |

| <variation name="">_st_s.v</variation>                      |                                                                                                                                                                                                                                                                            |

| <variation name="">_st_u.v</variation>                      |                                                                                                                                                                                                                                                                            |

| <variation name="">_st_wr.v</variation>                     |                                                                                                                                                                                                                                                                            |

| tb_ <variation name="">.vhd</variation>                     | This VHDL file provides a testbench for the customized FIR MegaCore function variation.                                                                                                                                                                                    |

#### Notes to Table 2-1

- (1) < variation name> is a prefix variation name supplied automatically by IP Toolbench.

- (2) The <entity name> prefix is added automatically. The VHDL code for each MegaCore instance is generated dynamically when you click **Finish** so that the <entity name> is different for every instance. It is generated from the <*variation name*> by appending \_ast.

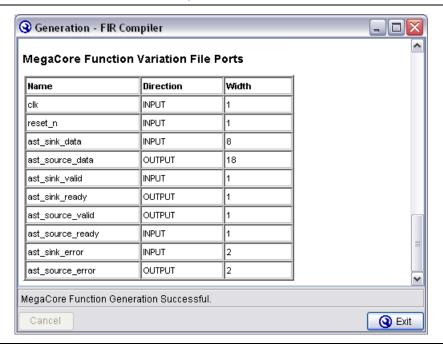

The generation report also lists the ports defined in the MegaCore function variation file (Figure 2–7). For a full description of the signals supported on external ports for your MegaCore function variation, refer to Table 4–3 on page 4–16.

Figure 2-7. Port Lists in the Generation Report

2. After you review the generation report, click **Exit** to close IP Toolbench. Then click **Yes** on the **Quartus II IP Files** prompt to add the .**qip** file describing your custom MegaCore function variation to the current Quartus II project.

## Simulate the Design

To simulate your design in Verilog HDL or VHDL, use the IP functional simulation models generated by IP Toolbench.

The IP functional simulation model is the .vo or .vho file (located in your design directory) generated as specified in Step 1 on page 2–3.

For more information about IP functional simulation models, refer to the *Simulating Altera Designs* chapter in volume 3 of the *Quartus II Handbook*.

#### Simulating in ModelSim

A Tcl script (*<variation name*>\_msim.tcl) is also generated which can be used to load the VHDL testbench into the ModelSim simulator.

This script uses the file *<variation name>\_input.txt* to provide input data to the FIR filter. The output from the simulation is stored in a file *<variation name>\_output.txt*.

#### Simulating in MATLAB

To simulate in a MATLAB environment, run the *<variation\_name>\_model.m* testbench m-script, which also is located in your design directory. This script also uses the file *<variation name>\_input.txt* to provide input data. The output from the MATLAB simulation is stored in the file *<variation name>\_model\_output.txt*.

For MCV decimation filters, the *<variation name>*\_model\_output\_full.txt file is generated to display all the phases of the filter. You can compare this file with the *<variation name>*\_output.txt file to understand which phase the output belongs. For all other architectures, decimation filters provide the *N*th phase where *N* is the decimation factor.

#### Simulating in Third-Party Simulation Tools Using NativeLink

You can perform a simulation in a third-party simulation tool from within the Quartus II software, using NativeLink.

The Tcl script file *<variation name>\_nativelink.tcl* can be used to assign default NativeLink testbench settings to the Quartus II project.

To perform a simulation in the Quartus II software using NativeLink, perform the following steps:

- 1. Create a custom MegaCore function variation as described earlier in this chapter but ensure you specify your variation name to match the Quartus II project name.

- 2. Verify that the absolute path to your third-party EDA tool is set in the **Options** page under the Tools menu in the Quartus II software.

- 3. On the Processing menu, point to Start and click Start Analysis & Elaboration.

- 4. On the Tools menu, click **Tcl scripts**. In the **Tcl Scripts** dialog box, select <*variation name*>\_nativelink.tcl and click **Run**. Check for a message confirming that the Tcl script was successfully loaded.

- 5. On the Assignments menu, click **Settings**, expand **EDA Tool Settings**, and select **Simulation**. Select a simulator under **Tool name** then in **NativeLink Settings**, select **Compile test bench** and click **Test Benches**.

- 6. On the Tools menu, point to **EDA Simulation Tool** and click **Run EDA RTL Simulation**.

The Quartus II software selects the simulator, and compiles the Altera libraries, design files, and testbenches. The testbench runs and the waveform window shows the design signals for analysis.

For more information, refer to the *Simulating Altera Designs* chapter in volume 3 of the *Quartus II Handbook*.

### **Compile the Design and Program a Device**

You can use the Quartus II software to compile your design.

After you have compiled your design, program your targeted Altera device and verify your design in hardware.

For instructions on compiling and programming your design, and more information about the MegaWizard Plug-In Manager flow, refer to the Quartus II Help.

# 3. Parameter Settings

This chapter gives an example of how to parameterize a FIR Compiler MegaCore® function and describes the available parameters.

The **Parameterize - FIR Compiler** pages provide the same options whether they have been opened from the DSP Builder or MegaWizard Plug-In Manager flow.

For information about opening the parameterization pages, refer to "Design Flows" on page 2–1.

The user interface only allows you to select legal combinations of parameters, and warns you of any invalid configurations.

# **Specifying the Coefficients**

A FIR filter is defined by its coefficients. The FIR Compiler provides the following options for obtaining coefficients:

- You can use the FIR Compiler to generate coefficients. The coefficient generator supports single rate, interpolation, and decimation rate specification filter types. For information about generating coefficients for these filter types, refer to "Using the FIR Compiler Coefficient Generator" on page 3–2.

- You can load coefficients from a file. For example, you can create the coefficients in another application such as MATLAB, SPW, or a user-created program, save them to a file, and import them into the FIR Compiler. For more information, refer to "Loading Coefficients from a File" on page 3–6.)

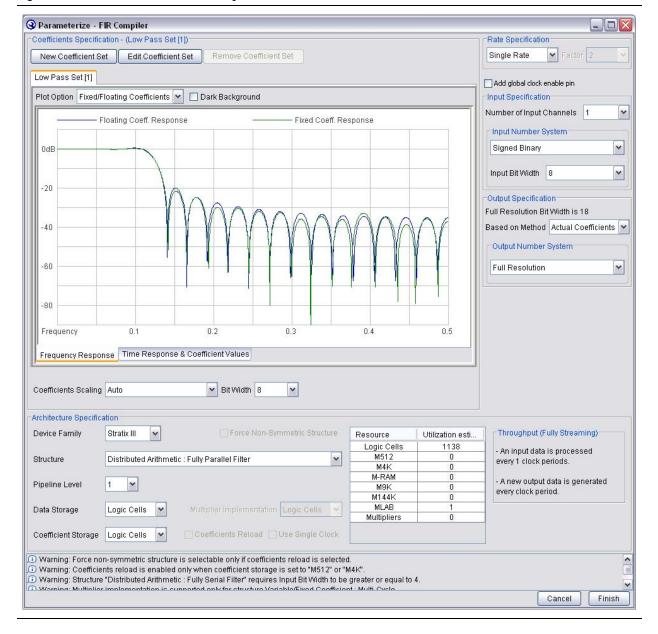

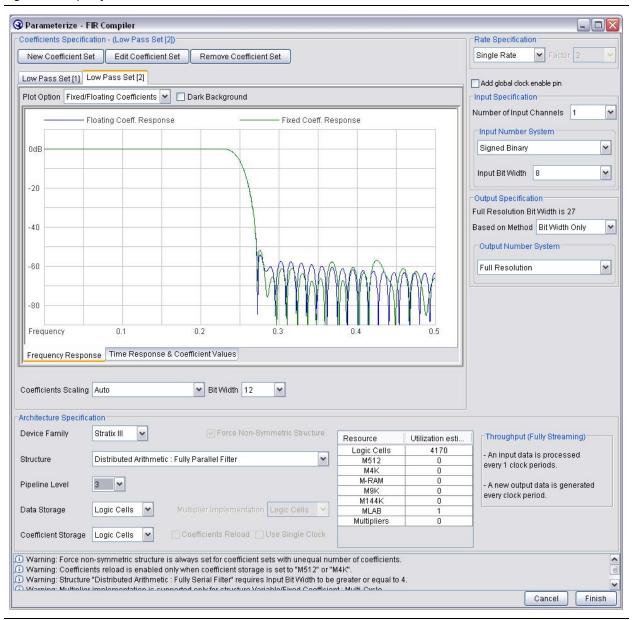

Figure 3–1 on page 3–2 shows the **Parameterize - FIR Compiler** page.

You can click **New Coefficient Set** on this page to define or load new coefficients. Alternatively, or you can click **Edit Coefficient Set** to edit the default coefficient set or **Remove Coefficient Set** to clear the currently loaded coefficients.

Figure 3–1. IP Toolbench Parameterize Page

## **Using the FIR Compiler Coefficient Generator**

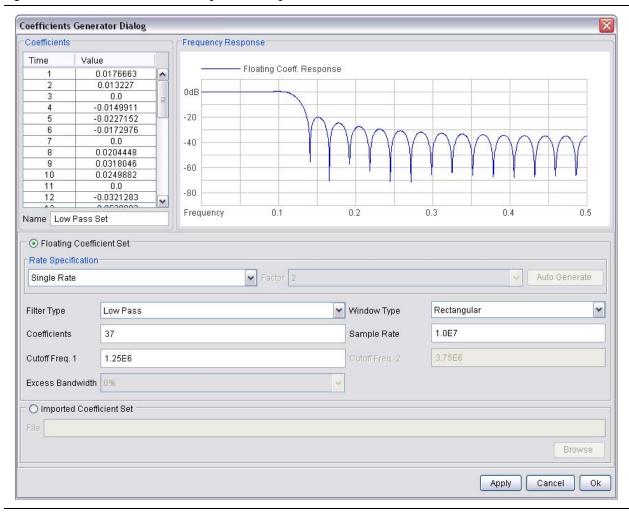

Click New Coefficient Set in the Parameterize - FIR Compiler page to open the Coefficients Generator dialog box.

You can use this dialog box to specify parameters for the coefficients, including the filter type, window type, sample rate, and excess bandwidth (for use with cosine filters).

Figure 3–2 on page 3–3 shows the default values for a low pass filter.

**Figure 3–2.** Coefficients Generator Dialog Box Showing Default Low Pass Filter Parameters

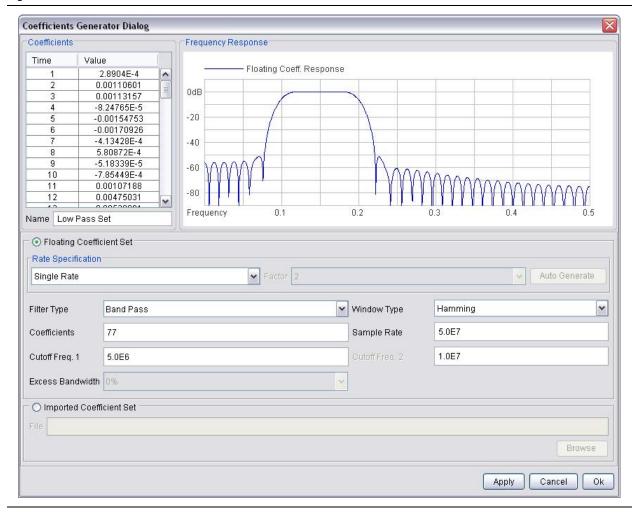

2. To generate the coefficients for a simple parallel filter, use the **Coefficients Generator** dialog box to make the settings listed in Table 3–1.

Table 3-1. Coefficients Generator Parameter Settings for a Simple Parallel Filter

| Parameter          | Value       |

|--------------------|-------------|

| Rate Specification | Single Rate |

| Filter Type        | Band Pass   |

| Coefficients       | 77          |

| Cutoff Freq. 1     | 5e+006      |

| Window Type        | Hamming     |

| Sample Rate:       | 50e+006     |

| Cutoff Freq. 2     | 10e+006     |

3. After making your settings, click **Apply**. The dialog box displays the frequency response of the filter in blue and also displays a list of the actual coefficient values. (Figure 3–3).

Figure 3-3. Parallel FIR Filter Coefficient Parameters for Band Pass Filter

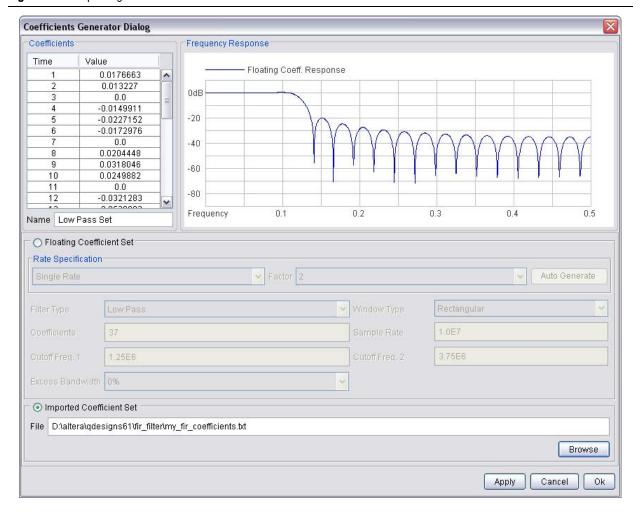

4. To generate floating-point coefficients for interpolation or decimation rate filters, select **Interpolation** or **Decimation** and the required **Factor** from the **Rate Specification** drop-down boxes.

When you click **Auto Generate**, IP Toolbench generates coefficients for a low-pass filter with a cutoff frequency based on the specified rate.

Figure 3–4 on page 3–5 shows a decimation filter. The cut-off frequency is ¼ of the sampling rate and results in a half-band coefficient set.

For an explanation of interpolation and decimation, refer to "Interpolation and Decimation" on page 4–8.

**Coefficients Generator Dialog** Coefficients Frequency Response Time Value Floating Coeff. Response -0.0167338 0dB 0.0 3 0.0187044 -20 -0.0211985 -40 0.0 -60 0.0244618 0.0 -80 Frequency 0.1 0.2 Name Low Pass Set Floating Coefficient Set Rate Specification ▼ Factor 2 Decimation Auto Generate Filter Type Low Pass Window Type Rectangular Coefficients 39 Sample Rate 5.0E7 Cutoff Freq. 1 1.25E7 Excess Bandwidth 0% O Imported Coefficient Set Browse Cancel Apply Ok

Figure 3-4. Low-Pass Filter Results for an Interpolation Filter

5. Click **OK** when you have finished making the parameter settings.

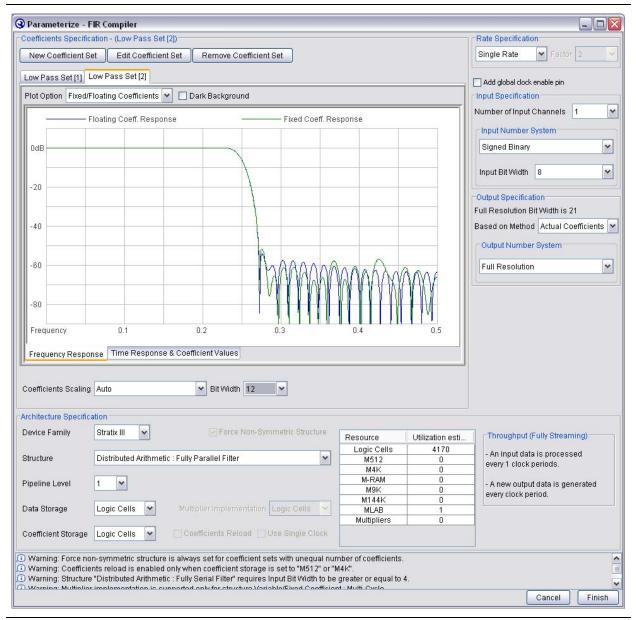

The **Parameterize - FIR Compiler** page (Figure 3–1 on page 3–2) is updated to display the frequency response of the floating coefficients in blue and the frequency response of the fixed coefficients in green.

You can click the **Time Response & Coefficient Values** tab to list the coefficients as shown in Figure 3–5 on page 3–6.

Figure 3–5. IP Toolbench Parameterize Page, Time Response and Coefficient Values Tab

#### **Loading Coefficients from a File**

To load a coefficient set from a file, perform the following steps:

1. Click **New Coefficient Set** in the **Parameterize - FIR Compiler** page (Figure 3–1 on page 3–2); then select **Imported Coefficient Set** in the **Coefficients Generator** dialog box (Figure 3–6 on page 3–7).

Figure 3-6. Importing a Coefficient Set

#### Note to Figure 3-6:

- (1) The radio buttons for the Floating Coefficient Set and Imported Coefficient Set parameters are linked together; selecting one disables the other.

- 2. Browse in the file system for the file you want to use, and click **Open**.

Your coefficient file should have each coefficient on a separate line and no carriage returns at the end of the file. You can use floating-point or fixed-point numbers, as well as scientific notation.

Do not insert additional carriage returns at the end of the file. The FIR Compiler interprets each carriage return as an extra coefficient with the value of the most recent past coefficient. The file should have a minimum of five non-zero coefficients.

3. Click **OK** to import your coefficient set.

## **Analyzing the Coefficients**

The FIR Compiler contains a coefficient analysis tool, which you can use to create sets of coefficients and perform actions on each set.

Some actions, such as scaling, apply to all sets. Other actions, such as recreating, reloading, or deleting, apply to the set you are currently viewing.

The FIR Compiler supports up to 16 sets of coefficients. You can switch between sets using the coefficient tabs in the **Parameterize - FIR Compiler** page. (The coefficient sets are numbered, for example, **Low Pass Set 1**, **Low Pass Set 2** and so on.)

When you select a set, the frequency response of the floating-point coefficients is displayed in blue, and the frequency response of the fixed-point coefficients in green. You can also view the actual coefficient values. by clicking the **Time Response & Coefficient Values** tab.

The FIR Compiler supports two's complement, signed binary fractional notation, which allows you to monitor which bits are preserved and which bits are removed during filtering. A signed binary fractional number has the format:

```

<sign> <integer bits>.<fractional bits>

```

A signed binary fractional number is interpreted as shown below:

```

<sign> <x_1 integer bits>.<y_1 fractional bits> Original input data <sign> <x_2 integer bits>.<y_2 fractional bits> Original coefficient data <sign> <i integer bits>.<y_1 + y_2 fractional bits> Full precision after FIR calculation <sign> <x_3 integer bits>.<y_3 fractional bits> Output data after limiting precision where i = ceil(log_2(number of coefficients)) + x_1 + x_2

```

If, for example, the number has 3 fractional bits and 4 integer bits plus a sign bit, the entire 8-bit integer number is divided by 8, which yields a number with a binary fractional component.

DSP Builder incorporates the sign bit as part of the integer bits. Thus, if you are using the FIR filter in a DSP Builder design, DSP builder will recognize the sign bit as an additional integer bit.

When converted to decimal numbers, certain fractions have an infinite number of binary bits. For example, converting 1/3 to a decimal number yields 0.333n with n representing an infinite number of 3s. Similarly, numbers such as 1/10 cannot be represented in a finite number of binary digits with full precision. If you use signed binary fractional notation, the FIR Compiler uses the fractional number that most closely matches the original number for the number of bits of precision you select.

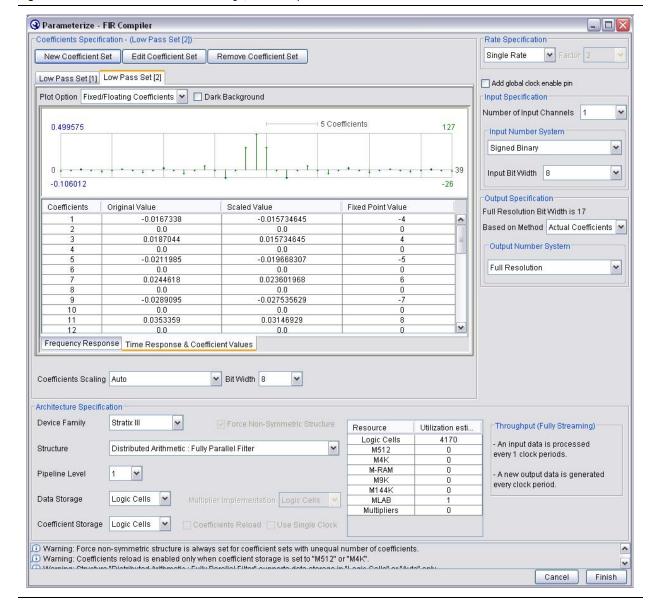

For this tutorial, select **Auto** for **Coefficients Scaling** and **12** for the **Coefficient Bit Width**.

Auto scaling (without the power of two option) provides the maximum signal-tonoise ratio. All other scaling factors such as Signed Binary Fractional can result in a loss of effective bits (that is, where each effective bit provides 6dB of SNR). Figure 3–7 shows the result after you have made the selections. Note that the side lobes of the fixed-point frequency response decrease when you change the bit width from 8 (the default) to 12.

Figure 3–7. Analyzing the Coefficients

# **Specify the Input and Output Specifications**

You can specify the **Number of Input Channels** (that is, the number of data streams that generate an output for each stream) and the **Input Number System** in the **Parameterize - FIR Compiler** page (Figure 3–7).

The FIR Compiler calculates how many bits your filter requires for full resolution using two methods: actual coefficients or the coefficient bit widths. These parameters define the maximum positive and negative output values. Select either **Bit Width Only** or **Actual Coefficients** in the **Output Specification** drop-down box. The FIR Compiler will extrapolate the number of bits required to represent that range of values. For full precision, you must use this number of bits in your system.

If your filter has coefficient reloading or multiple sets of coefficients, you must select **Bit Width Only**.

You can use full or limited precision for the filtered output (out). To use full precision, leave the **Output Number System** set to Full Resolution (default). To limit the precision, select **Custom Resolution** or **Signed Binary Fractional** from the drop down box.

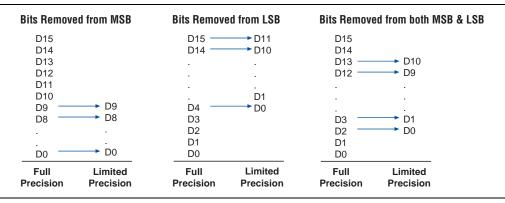

When the **Output Number System** is set to **Custom Resolution**, you can choose to truncate or saturate the most significant bit (MSB) and to truncate or round the least significant bit (LSB). Saturation, truncation, and rounding are non-linear operations.

Table 3–2 shows the options for limiting the precision of your filter.

Bit Range Option Result

MSB Truncate In truncation, the filter disregards specified bits. (Figure 3–8).

Saturate In saturation, if the filtered output is greater than the maximum positive or negative value that can be represented, the output is forced (or saturated) to the maximum positive or negative value.

LSB Truncate Same process as for MSB.

Round The output is rounded away from zero.

Table 3-2. Options for Limiting Precision

Figure 3–8 shows an example of removing bits from the MSB and LSB.

Figure 3-8. Removing Bits from the MSB and LSB

Alternatively, you can select **Signed Binary Fractional** notation and specify the number of bits to keep. The FIR Compiler displays how many bits are removed.

When adjusting the input and output specification, follow these tips:

- Truncating from the MSB reduces logic resources more than saturation.

- The Number of Input Channels option is useful for designs such as modulators and demodulators, which have I and Q channels. If you are designing this type of application, select 2 input channels. This tutorial uses the default settings.

# **Specify the Architecture Specification**

You are now ready to select the architecture parameters from the lower half of the **Parameterize - FIR Compiler** page.

The FIR Compiler supports several filter structures, including:

- Variable/Fixed coefficient: Multicycle

- Distributed arithmetic: Fully Parallel Filter

- Distributed arithmetic: Fully Serial Filter

- Distributed arithmetic: Multibit Serial Filter

For maximum clock speed, select the Distributed Arithmetic: Fully Serial Filter structure. (For Stratix, Stratix II, Stratix III, or Stratix IV devices, using smaller memory resources for coefficient and data storage is faster than using larger memory resources.) For maximum throughput, select the Distributed Arithmetic: Fully Parallel structure.

When reloading coefficients, a multicycle variable FIR filter structure has a short reloading time compared to a fixed FIR filter. Additionally, smaller memory blocks have a shorter reloading time than larger memory blocks.

Table 3–3 describes the relative trade-offs for the different architecture options.

Table 3-3. Architecture Trade-Offs

| Technology                             | Option             | Area                                                                                                                     | Speed (Data Throughput)                                                                                                                                                                               |

|----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Distributed arithmetic                 | Fully parallel     | Large area                                                                                                               | Creates a fast filter: 140 to over 300 MSPS throughput with pipelining in Stratix II devices.                                                                                                         |

| Distributed arithmetic                 | Fully serial       | Small area                                                                                                               | Requires multiple clock cycles for a single computation.                                                                                                                                              |

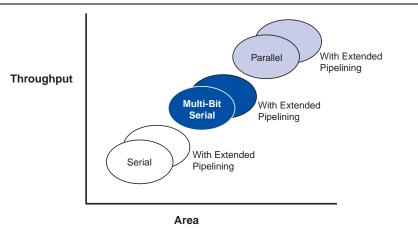

| Distributed arithmetic                 | Multibit<br>serial | Medium area                                                                                                              | Uses several serial units to increase throughput. This results in greater throughput than fully serial, but less throughput than fully parallel.                                                      |

| DSP block<br>multiplier                | Multicycle         | Area depends on the number of calculation cycles selected (area increases as the number of calculation cycles increases) | Data throughput increases as the number of calculation cycles decreases. This architecture takes advantage of Stratix, Stratix II, Stratix III, or Stratix IV DSP Blocks, and Cyclone II Multipliers. |

| Available option for all architectures | Pipelining         | Creates a higher performance filter with an area increase.                                                               | Increases throughput with additional latency and size increase.                                                                                                                                       |

For more information about the filter architectures and how they operate, refer to "FIR Compiler" on page 4–1.

Table 3–4, Table 3–5, Table 3–6, and Table 3–7 describe the FIR Compiler options that are available for each architecture.

**Table 3–4.** Multicycle Filter Architecture (Note 1)