MegaCore IP Library

# **Release Notes and Errata**

101 Innovation Drive San Jose, CA 95134 www.altera.com

RN-IP-7.3

Document last updated for Altera Complete Design Suite version: Document publication date: 10.1 March 2011

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

#### **About These Release Notes**

| Trademarks                                                       |      |

|------------------------------------------------------------------|------|

| System Requirements                                              |      |

| Revision Dates                                                   | –xvi |

| Chapter 1. 8B10B Encoder/Decoder                                 |      |

| Revision History                                                 | 1–1  |

| Errata                                                           |      |

| Chapter 2. 10GBASE-R PHY                                         |      |

| Revision History                                                 | 2–1  |

| Errata                                                           | 2–1  |

| FIFO Full Signals Are Swapped                                    |      |

| rx_ready Bit Does not Update When Synchronization Is Lost        |      |

| Incorrect Device Support Listed 10GBASE-R PHY IP Core User Guide |      |

#### **Chapter 3. 10-Gbps Ethernet MAC**

| Revision History                                    | 3–1 |

|-----------------------------------------------------|-----|

| Errata                                              | 3–1 |

| No Length Checking for VLAN and Stacked VLAN Frames | 3–1 |

| Simulation Not Supported for Stratix V Designs      | 3–2 |

#### Chapter 4. ASI

| Revision History                                                        | 4–1 |

|-------------------------------------------------------------------------|-----|

| Errata                                                                  | 4–1 |

| ASI Does Not Support VHDL Functional Simulation Model for Cyclone IV GX | 4–1 |

| ASI 10.1 Does Not Support Qsys                                          | 4–2 |

| NativeLink Does Not Support Gate-Level Simulation                       |     |

#### Chapter 5. CIC

| Revision History                                                               | 5–1 |

|--------------------------------------------------------------------------------|-----|

| Errata                                                                         | 5–1 |

| Compilation Targeting a Stratix V Device Fails                                 | 5–1 |

| Error Generating HDL for Decimator with More Than 9 Stages and 11 Interfaces   |     |

| OpenCore Plus Feature Not Supported for Cyclone IV E and Cyclone IV GX Devices |     |

#### Chapter 6. CPRI

| Revision History                                                                      | 6–1      |

|---------------------------------------------------------------------------------------|----------|

| Errata                                                                                | 6–1      |

| MII Interface Description in v10.1 User Guide Contains Errors                         | 6–3      |

| CPRI Protocol Version Default Value is Invalid                                        | 6–4      |

| CPU Interface Deadlocks After Attempt to Access Ethernet or HDLC Registers When MII I | nterface |

| Enabled                                                                               | 6–4      |

| Errors in .mif File Names in Auto-rate Negotiation Testbenches                        | 6–5      |

| Testbench tb_altera_cpri.vhd Does Not Simulate                                        | 6–5      |

| Cyclone IV GX REC Master Cannot Achieve Link Synchronization                          | 6–6      |

| Some MegaCore Variations Have Invalid cpri_clkout Frequency                           | 6–7      |

|     | cpri_rx_cnt_sync port Description and Frame Synchronization FSM in User Guide are Incorrec | t. 6–8 |

|-----|--------------------------------------------------------------------------------------------|--------|

|     | Cannot Simulate CPRI MegaCore Function in Verilog HDL                                      |        |

|     | Timing Violations in Some Device Families, Speed Grades, and Line Rates                    | 6–9    |

|     | Erroneous File Names in CPRI 10.1 Testbench Description in User Guide                      |        |

|     | PRBS is Not Supported in Cyclone IV GX Devices                                             |        |

|     | Auto-Rate Negotiation Does Not Support 614.4 Mbps Line Rate in Cyclone IV GX Devices       |        |

|     | Wrong Extended Rx Delay Measurement Clock Period                                           |        |

|     | Simulation Testbench Does Not Support Cyclone IV GX Variations                             |        |

|     | Cannot Simulate Auto-Rate Negotiation in Verilog HDL With ModelSim 6.4b or Later           | . 6–12 |

|     | Warning Messages from Transceiver While Generating and Compiling CPRI MegaCore Functi      | on     |

|     | 6-13                                                                                       |        |

|     | CPRI MegaCore Function v10.0 User Guide Does Not Contain Complete Instructions for Runn    | ing    |

|     | v10.0 Simulation Testbench                                                                 |        |

|     | CPU Interrupt Bit Always Set When Interrupts are Enabled                                   |        |

|     | MII Interface Description in v9.1SP1 User Guide Contains Errors                            |        |

|     | CPRI MegaCore Function User Guide Unavailable From MegaWizard Interface Info Link          |        |

|     | MegaWizard Plug-In Manager Does Not Recognize Transceiver Instances                        |        |

|     | CPRI Frame Synchronization Machine Unable to Return to XACQ1 from XSYNC1                   |        |

|     | Setup Time Violations Might Occur in Arria II GX 3072 Mbps Designs                         | . 6–18 |

|     | CPRI MegaCore Function Does Not Support HardCopy IV GX Devices                             | . 6–18 |

|     | CPRI MegaCore Function v9.1SP1 User Guide Does Not Contain Complete Instructions for Ru    | nning  |

|     | v9.1SP1 Simulation Testbench                                                               | . 6–18 |

|     |                                                                                            |        |

|     | pter 7. CRC Compiler                                                                       |        |

|     | Revision History                                                                           |        |

| E   | Errata                                                                                     |        |

|     | Testbench Directory Generated When You Create a Simulation Model                           | 7–1    |

| Cha | ntor 9 DDD and DDD2 SDDAM Controllor Compiler                                              |        |

|     | pter 8. DDR and DDR2 SDRAM Controller Compiler Revision History                            | Q 1    |

|     | Errata                                                                                     |        |

| Ľ   | Quartus Compilation Error                                                                  |        |

| Quartus Compilation Error                      | . 8–1 |

|------------------------------------------------|-------|

| Partitioned Design Compilation Error           | . 8–2 |

| Error: Can't Find the Clock Output Pins. Stop. |       |

| ODT Launches Off System Clock                  |       |

| Error Message When Recompiling a Project       |       |

| Pin Planner HDL Syntax Error                   |       |

| •                                              |       |

### Chapter 9. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP

| 9–9  |

|------|

| 9–9  |

| 9–10 |

| 9–10 |

| 9–11 |

| 9–12 |

| 9–12 |

| 9–14 |

| 9–15 |

| 9–15 |

| 9–16 |

| 9–16 |

| 9–17 |

| 9–17 |

| 9–18 |

| 9–18 |

| 9–19 |

| 9–20 |

| 9–20 |

| 9–21 |

| 9–21 |

|      |

#### Chapter 10. DDR2 and DDR3 SDRAM Controller with UniPHY

| Revision History                                                           | 10–1  |

|----------------------------------------------------------------------------|-------|

| Errata                                                                     | 10–1  |

| Error in Graphical Display of DQ Calibration Margin in EMIF Toolkit        | 10–2  |

| NativeLink Simulation fails for VHDL Output                                | 10–3  |

| NativeLink Simulation fails for VHDL Output                                | 10–3  |

| Timing-related Warning Messages When Sharing PLLs on Stratix V Devices     | 10–4  |

| Half Rate Bridge Not Supported                                             |       |

| Devices Faster than 533MHz Require Manual Derating                         | 10–5  |

| Reset Synchronizer May Cause Design to Fail Timing                         |       |

| Compilation Fails if Synthesis Fileset is Mixed with Example Project Files |       |

| Warning Messages Displayed When Compiling for Stratix V Devices            | 10–6  |

| Cannot Launch MegaWizard Plug-In Manager by Opening Example Design         | 10–7  |

| Example Design May Not Compile for IP Cores from Earlier Versions          |       |

| SOPC Builder-generated Systems Cannot Serve as Top-Level Design            | 10–8  |

| Higher Delays and Skews Expected for Corner I/Os in Stratix V Devices      | 10–9  |

| Incorrect Clock Uncertainty                                                |       |

| User Guide Contains Incorrect Clock Information                            | 10–10 |

| Using Burst Merging Feature                                                | 10–11 |

| Autoprecharge Feature is Not Available                                     | 10–11 |

| Global Signal Assignments Not Applied                                      | 10–11 |

| BSF File Not Generated                                                     |       |

| Selecting VHDL Gives a Verilog HDL IP Core                                 | 10–12 |

| Designs Without Leveling Fail in Stratix V Devices                         |       |

| Quartus II Software Cannot Read .mif File for PLL                          | 10–14 |

| Example Design Fails as a Slave                                            |       |

| Simulation Fails in Riviera                                                |       |

| Simulation Fails—PLL Clocks Out of Synchronization                         |       |

| SOPC Builder Designs Suffer Low Efficiency                                 | 10–18 |

### Chapter 11. DDR3 SDRAM Controller with ALTMEMPHY IP

V

| Revision History                                                                | 11–1  |

|---------------------------------------------------------------------------------|-------|

| Errata                                                                          | 11–1  |

| Resynchronization Registers Incorrectly Placed in Core instead of I/O           | 11–2  |

| Half Rate Bridge Not Supported                                                  |       |

| Devices Faster than 533MHz Require Manual Derating                              | 11–3  |

| pin_assignments.tcl Contains Incorrect Pin Names in Qsys Systems                |       |

| Warning Messages Reporting Ignored SDC Constraints                              |       |

| Error in Board Settings GUI                                                     |       |

| Using Merging Feature                                                           |       |

| Memory Controller Returns Wrong Data                                            | 11–5  |

| Refresh to Precharge Command Timing Violation                                   | 11–6  |

| Power-Down Entry Command Timing Violation                                       |       |

| Failure to Regenerate 9.0 Designs in Silent Mode                                |       |

| csr_waitrequest Signal Exhibits "X" in Simulation                               | 11–8  |

| Wrong or Corrupted Data on Reads                                                | 11–8  |

| CSR Address 0×005 and 0×006 Contents Cannot be Accessed                         | 11–9  |

| Memory Timing Violation During Activate Read Auto-Precharge to Refresh/Activate | 11–10 |

| Half-Rate Clock Not Connected When Clock Sharing is Enabled                     | 11–10 |

| Timing Violation In Half-Rate Bridge Enabled Designs                            | 11–12 |

| Generate Simulation Model Option Gets Disabled                                  | 11–12 |

| Designs with Eight Chip Selects Fail Compilation                                | 11–13 |

| Address Mirroring Not Supported By Memory Simulation Model                      | 11–13 |

| Memory Preset Parameters Do Not Get Updated                                     | 11–15 |

| Designs with Error Correction Coding (ECC) Do Not Work After Subsequent Reset   | 11–15 |

|                                                                                 |       |

# Chapter 12. FFT

| Revision History                                                                                  |

|---------------------------------------------------------------------------------------------------|

| Errata                                                                                            |

| Compilation Targeting a Stratix V Device Fails                                                    |

| Variable Streaming Floating Point Variations Cannot SImulate Inverse FFT Computation 12–2         |

| Variable Streaming Floating Point Variations Might Produce ±1 Errors in Simulation                |

| Simulation Errors—MATLAB Model Mismatch                                                           |

| Some Variations with VHDL Output Files Generate Incorrect Simulation Models for Stratix V Devices |

| 12–4                                                                                              |

| Example Design Fails Compilation                                                                  |

| Simulation Errors—Incorrect Results                                                               |

#### **Chapter 13. FIR Compiler**

| Revision History                                                                           | 13–1      |

|--------------------------------------------------------------------------------------------|-----------|

| Errata                                                                                     | 13–1      |

| Compilation Targeting a Stratix V Device Fails                                             | 13–2      |

| Compilation Targeting a HardCopy Device Requires Removal of .hex Files                     | 13–2      |

| Half-Band Decimation Filters That Use MLABs for Coefficient Storage in Stratix V Devices   | Fail 13–3 |

| Symmetric Interpolation Filters That Use M20K Blocks for Data Storage in Stratix V Devices | s Fail    |

| 13–3                                                                                       |           |

| FIR Filters With Large Numbers of Coefficients and Non-Symmetric Structure Do Not Gene     | erate     |

| Netlist and IPFS Model Correctly                                                           | 13–4      |

| Simulation Fails for the Coefficient Reloadable Filters                                    | 13–4      |

| FIR Compiler Functional Simulation Model Is Not Generated                                  | 13–5      |

| FIR Compiler Does Not Support OpenCore Plus for Cyclone IV E Devices                       | 13–5      |

| Incorrect Results for Multi-Bit Serial or Interpolation with Signed Binary Fractional      | 13–6      |

| Block Memory Incorrectly Used When Logic Storage Selected                                  | 13–6      |

| Simulation Result Incorrect Using MCV Interpolation Filters                                | 13–7      |

| Reloadable Coefficient Filters Fail for Some MCV Filters | <br>7  |

|----------------------------------------------------------|--------|

| Quartus II Simulation Vector File Not Generated          | <br>-8 |

#### Chapter 14. FIR Compiler II

| Errata                                                                                |     |

|---------------------------------------------------------------------------------------|-----|

|                                                                                       |     |

| Unable to Run FIR Compiler II                                                         | 4–2 |

| NativeLink is Not Supported                                                           | 4–2 |

| Simulation Fails with Single-Language Simulator14                                     | 4–3 |

| M144K Memories Output X's in the ModelSim-Altera Software14                           |     |

| Incorrect Testbench Result When Interpolation Factor Is Greater Than The TDM Factor14 | 4–4 |

| Incorrect Results for a Decimation Configuration14                                    | 4–4 |

| Incorrect Results Might Be Produced When Input Bit Width is Greater Than 17 bits      | 4–5 |

| Simulation fails with the NCSim/Riviera-Pro/ActiveHDL Simulator14                     | 4–5 |

| Compiler Does Not Create a Block Symbol File14                                        | 4–6 |

#### Chapter 15. Interlaken

| Revision History                                                        | . 15–1 |

|-------------------------------------------------------------------------|--------|

| Errata                                                                  | . 15–1 |

| rxt_rxd Warning for 10- and 20-lane Variations With Transceivers        | . 15–1 |

| Compiler Warnings When Transceivers are Excluded                        | . 15–2 |

| Critical Warnings for 12- and 20-lane Variations Without Transceivers   |        |

| C106 Warnings for 10- and 20-lane Variations With Transceivers          |        |

| Aldec Riviera-PRO Simulator Cannot Simulate Interlaken 8-lane Variation |        |

| 10.3125-Gbps Variation with Transceivers Runs at Incorrect Lane Rate    | . 15–4 |

|                                                                         |        |

### Chapter 16. Interlaken PHY

| Revision History                                        | . 16–1 |

|---------------------------------------------------------|--------|

| Errata                                                  | . 16–1 |

| Mixed Language Simulation Fails when Optimization Is On | . 16–1 |

### Chapter 17. NCO

| Revision History                                                                   | 17–1 |

|------------------------------------------------------------------------------------|------|

| Errata                                                                             | 17–1 |

| Compilation Targeting a Stratix V Device Fails                                     | 17–1 |

| Mismatches Between Multiplier-Based MATLAB and RTL Models With Throughput One Half | 17–2 |

| Mismatches Between Some Serial CORDIC MATLAB and RTL Models                        | 17-3 |

| Mismatches Between Some Small ROM MATLAB and RTL Models                            | 17–3 |

| Warning Message Displayed Twice                                                    | 17–4 |

| Mismatches Between Multiplier-Based MATLAB and RTL Models With Throughput One      | 17–4 |

|                                                                                    |      |

#### **Chapter 18. Nios II Processor**

| Revision History                                                                     |  |

|--------------------------------------------------------------------------------------|--|

| Errata                                                                               |  |

| Cannot Remove EIC Interface from Nios II Processor                                   |  |

| Error: Debug Slave <slave interface="" name=""> Not Connected to data_master</slave> |  |

| The cpu_resetrequest and cpu_resettaken Signals Do Not Export                        |  |

| Custom Instruction Import Fails and Freezes GUI                                      |  |

| HardCopy III and HardCopy IV Support Incorrectly Stated                              |  |

| Error Running Nios II Project: 'Downloading ELF Process failed'                      |  |

| Cannot Implement Multiplier as DSP Block in Cyclone IV Devices                       |  |

| Design Assistant Error on Clock Signal Source in HardCopy Designs                    |  |

| Nios II Ports Created Incorrectly                                                    |  |

|                                                                                      |  |

| hapter 19. PCI Compiler                                                                                        |        |

|----------------------------------------------------------------------------------------------------------------|--------|

| Revision History                                                                                               | 19_1   |

| Errata                                                                                                         |        |

| Configuration Write to Invalid Address Repeats Continuosly                                                     |        |

| Designs With Cyclone III LS Devices Fail to Meet Timing                                                        |        |

| F1152 Packages for HardCopy III and HardCopy IV-E Not Supported                                                |        |

| Wirebond Packages for HardCopy III and HardCopy IV-E Not Supported                                             |        |

| Designs With Stratix IV Devices Fail to Meet Timing                                                            |        |

| hapter 20. PCI Express Compiler                                                                                |        |

| Revision History                                                                                               | 20-1   |

| Errata                                                                                                         |        |

| User Guide and Parameter Editor Allow Incorrect Application Clock Frequency                                    |        |

| Hold Time Violations for Hard IP Variations on Arria II GZ Devices                                             |        |

| PCI Express IP Core Cannot Negotiate to Gen 2 Data Rate on Some Devices                                        |        |

| Memory Read Requests Hang in the SOPC Builder Soft IP Implementation                                           |        |

| Incorrect Arria II GZ Device Support in PCI Express Compiler User Guide                                        |        |

| PCI Express Compiler User Guide Incorrectly Includes an ALTGXB Reset Signal                                    |        |

| Incorrect Numbering of 256-Bit Interface in PCI Express Compiler User Guide                                    |        |

| Posted Requests and Completions May Be Blocked if rx_st_mask Is Asserted                                       |        |

| Root Port Example Design Simulation Fails for Some Versions of ModelSim                                        |        |

| VCS Simulation Script Fails for PCIe Root Port Design Example                                                  |        |

| SOPC Builder Hard IP Implementation Hangs when Entering L1 State                                               | . 20–8 |

| The Transceiver May Be Incorrectly Reset Leading to Unreliable Link Behavior                                   | . 20–8 |

| Timing Analysis for Cyclone IV GX ×1 Variants                                                                  |        |

| PCI Express Compliance Test Does Not Generate Gen2 Compliance Pattern                                          |        |

| Arria II GX Missing PLL_powerdown Signal when Using Custom Quartus II Installation                             | 20–10  |

| Compilation Fails for Hard IP PCI Express MegaCore Function in Stratix IV GT Devices                           |        |

| PCI Express Hard IP Compilation Is Disabled for Gen1 ×4 and ×8 in Some Devices                                 |        |

| PCI Express Design Example Does Always Not Close Timing in Stratix V GX and HardCopy IV                        |        |

| in 250 MHz Modes                                                                                               |        |

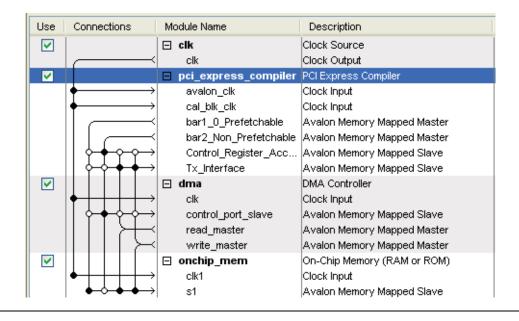

| Incorrect Connections Shown in SOPC Builder Illustration                                                       |        |

| Incorrect HardCopy IV GX PCIe Gen2 ×8 Buffer Size Restriction Implementation                                   |        |

| refclk Cannot Be Used to Generate reconfig_clk                                                                 |        |

| Connecting r2c_err0 or r2c_err1 Output Ports to Your Application Causes Quartus II Compilation                 |        |

| Fail                                                                                                           |        |

| Arria II GX Does Not Report ECC Error Correction and ECC Uncorrectable Error Detection?                        |        |

| Link Training or Down Training Hardware Issues with Gen2 ×4 or ×8 in Stratix IV GX Hard IP 20–14               |        |

| MSI Requests not Supported in Completer Only Mode                                                              | 20–14  |

| Incorrect <variation>_serdes.v(hd) File Produced When Editing an Older PCI Express Variation 20–15</variation> | ۱ File |

| Compilation Fails when Working Directory Name Has a Space                                                      | 20–15  |

| MSI-X Capability Structure Not Working in Hardware                                                             |        |

| PCI Express Compiler User Guide, Version 9.1 Error in Table 1-4, Hard IP Configurations                        |        |

| Revision History                                         | 21–1 |

|----------------------------------------------------------|------|

| Errata                                                   | 21–1 |

| Compilation Targeting a Stratix V Device Fails           | 21–2 |

| Import PLL Frequency Launches Incorrect Parameter Editor | 21–2 |

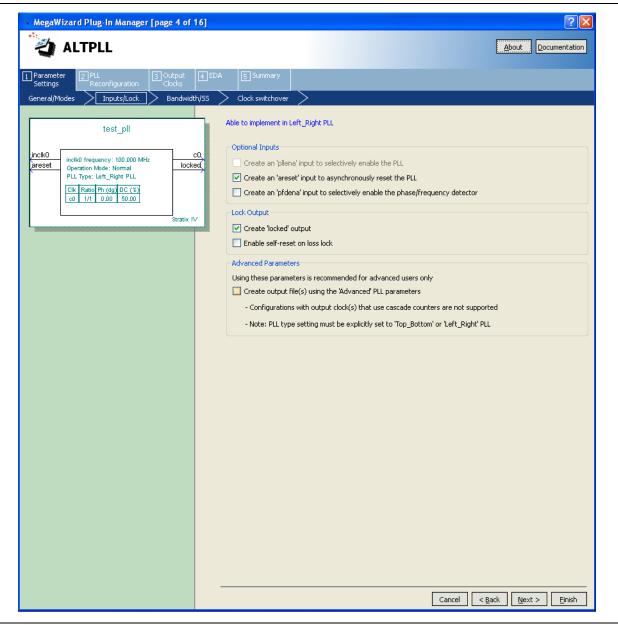

| Cannot Edit ALTPLL Megafunction for Stratix V Devices                                      | 21–3     |

|--------------------------------------------------------------------------------------------|----------|

| Incorrect LVDS Frequencies in Quartus II Compilation                                       | 21–3     |

| Errors when Editing Transmitters v7.2 or Earlier in v8.0                                   | 21–4     |

| Training Interval is Greater than Specified                                                | 21–4     |

| Irrelevant Signals: err_ry_msop* & err_ry_meop*                                            |          |

| Warning Message: Pin "err_rd_dpa" Stuck at GND                                             |          |

| The Calendar Length Value Cannot Equal 256                                                 | 21–5     |

| IP Toolbench Error After Changing the Device Family                                        | 21–6     |

| IP Toolbench Fails to Generate IP Functional Simulation Models for HardCopy Stratix Device | ces 21–7 |

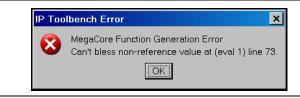

| IP Toolbench Generation Fails if the Generation Is Cancelled and Restarted                 | 21–7     |

### Chapter 22. QDRII SRAM

| Revision History                                                  |  |

|-------------------------------------------------------------------|--|

| Errata                                                            |  |

| Termination Error When Compiling Design                           |  |

| Incorrect IP Toolbench Latency Behavior                           |  |

| Simulating with the VCS Simulator                                 |  |

| TimeQuest Timing Analyzer Failure                                 |  |

| PLL Placement                                                     |  |

| Constraints Errors With Companion Devices                         |  |

| Supported Device Families                                         |  |

| Compilation Error (Stratix II Series & HardCopy II Devices Only)  |  |

| Gate-Level Simulation Filenames                                   |  |

| The ModelSim Simulation Script Does Not Support Companion Devices |  |

|                                                                   |  |

#### Chapter 23. QDR II and QDR II+ SRAM Controller with UniPHY

| Revision History                                                           |       |

|----------------------------------------------------------------------------|-------|

| Errata                                                                     |       |

| VHDL-only Simulation Not Supported                                         |       |

| NativeLink Simulation fails for VHDL Output                                |       |

| NativeLink Simulation fails for VHDL Output                                |       |

| Timing-related Warning Messages When Sharing PLLs on Stratix V Devices     |       |

| Reset Synchronizer May Cause Design to Fail Timing                         | 23–4  |

| Compilation Fails if Synthesis Fileset is Mixed with Example Project Files |       |

| Warning Messages Displayed When Compiling for Stratix V Devices            |       |

| Cannot Launch MegaWizard Plug-In Manager by Opening Example Design         |       |

| Example Design May Not Compile for IP Cores from Earlier Versions          |       |

| Calibration Failure in Earlier Versions                                    |       |

| SOPC Builder-generated Systems Cannot Serve as Top-Level Design            |       |

| Higher Delays and Skews Expected for Corner I/Os in Stratix V Devices      |       |

| Simulation Fails—PLL Clocks Out of Synchronization                         |       |

| Selecting VHDL Gives a Verilog HDL IP Core                                 |       |

| BSF File Not Generated                                                     | 23–10 |

| Global Signal Assignments Not Applied                                      | 23–11 |

| Simulation Error                                                           | 23–11 |

| Incorrect Clock Uncertainty                                                | 23–12 |

| IP Core May Not Operate Below 167MHz                                       | 23–13 |

| UniPHY DQS Clock Buffer Location                                           |       |

| IP Functional Simulation Model                                             |       |

| No Link to User Guide from Wizard                                          |       |

| Incorrect Operation of Waitrequest Signal                                  |       |

| QDR II SRAM Emulated Mode                                                  |       |

### Chapter 24. RapidIO

| Revision History                                                                       | 24–1      |

|----------------------------------------------------------------------------------------|-----------|

| Errata                                                                                 | 24–1      |

| Receive Buffer Can Overflow                                                            | 24–3      |

| Migration from SOPC Builder to Qsys Changes Port Names                                 | 24–3      |

| Warning Message Indicates Preliminary Support for Arria II GX Devices                  | 24–4      |

| Parameter Values Modified in SOPC to Qsys Conversion                                   |           |

| Generation Stalls in Arria GX and Stratix II GX Designs                                |           |

| Cannot Regenerate RapidIO MegaCore Function with Read-only .qip File                   | 24–5      |

| Device and Assembly Register Values Might Lose MSBs                                    | 24–6      |

| Qsys Appears to Allow Larger Revision IDs Than are Implemented                         | 24–7      |

| Some MegaCore Variations Return Incorrect Read Data                                    | 24–8      |

| Some Cyclone III Designs Fail Hold Time Requirements in TimeQuest Timing Analyzer .    | 24–8      |

| Migrated Designs Automatically Set to Seven link-request Attempts                      | 24–9      |

| Stratix II GX Transceiver Transmitter Buffer Power Does Not Regenerate Correctly       | 24–9      |

| Unsupported Input Clock Frequencies Available in RapidIO MegaWizard Interface          | 24–10     |

| MegaWizard GUI Does Not Warn That Small Cyclone IV GX Devices Are Not Supported        | 24–11     |

| The Demonstration Testbench May Fail for Some RapidIO Variations                       | 24–11     |

| Incorrect cmu_pll_inclock_period in Stratix II GX and Arria GX Designs                 |           |

| Critical Warning Displays if System Clock and Reference Clock Have Same Source         | 24–13     |

| Doorbell Response Packets are not Sent if Master Enable Bit is not Set                 |           |

| A link-request reset-device Sequence Can Be Ignored                                    |           |

| Specific Variation With Transaction Ordering Enabled Requires Additional Logical Layer | Modules . |

| 24–15                                                                                  |           |

| Some Variations Do Not Meet Timing Requirements                                        | 24–15     |

| Certain Changes Made in the RapidIO MegaWizard Interface are Ignored                   |           |

| Changes Made to the Reference Clock in the ALTGX MegaWizard Interface are Ignored .    |           |

| Starting Channel Number Resets When SOPC Builder is Closed                             | 24–17     |

| Reception of a Small Packet Can Cause Counter Overflow in the Transport Layer Module   | 24–18     |

| Some Variations With High Reference Clock Frequency Generate Critical Timing Warning   | s 24–19   |

| Stratix IV Simulations May Fail With ModelSim 6.3g Compiler Optimizations Enabled      | 24–20     |

|                                                                                        |           |

#### **Chapter 25. Reed-Solomon Compiler**

| Revision History                                                      |  |

|-----------------------------------------------------------------------|--|

| Errata                                                                |  |

| Compilation Targeting a Stratix V Device Fails                        |  |

| Verilog HDL Simulation Fails                                          |  |

| RS Decoder Fails When Number of Check Symbols and Symbols are Similar |  |

### Chapter 26. Reed-Solomon II

| Revision History                            |  |

|---------------------------------------------|--|

| Errata                                      |  |

| Backpressure Feature is Not Supported       |  |

| Unsupported Variants                        |  |

| Unable to Support Invalid Avalon-ST Packets |  |

### Chapter 27. RLDRAM II

| Revision History                                                         |  |

|--------------------------------------------------------------------------|--|

| Errata                                                                   |  |

| The Quartus II Design Assistant Reports Critical Warning                 |  |

| Hold Timing Violation                                                    |  |

| NativeLink Fails with the ModelSim Simulator                             |  |

| Add an RLDRAM II Controller to a Project with Other Memory Controllers . |  |

| Simulating with the NCSim Software                                          |  |

|-----------------------------------------------------------------------------|--|

| Simulating with the VCS Simulator                                           |  |

| Multiple Instances of the auk_ddr_functions.vhd File                        |  |

| Gate-Level Simulation Filenames                                             |  |

| Unpredictable Results for Gate-Level Simulations (HardCopy II Devices Only) |  |

| Editing the Custom Variation (non-DQS Mode)                                 |  |

### Chapter 28. RLDRAM II Controller with UniPHY

| Revision History                                                           |       |

|----------------------------------------------------------------------------|-------|

| Errata                                                                     |       |

| VHDL-only Simulation Not Supported                                         |       |

| NativeLink Simulation fails for VHDL Output                                |       |

| NativeLink Simulation fails for VHDL Output                                |       |

| Timing-related Warning Messages When Sharing PLLs on Stratix V Devices     |       |

| Reset Synchronizer May Cause Design to Fail Timing                         |       |

| Compilation Fails if Synthesis Fileset is Mixed with Example Project Files |       |

| Warning Messages Displayed When Compiling for Stratix V Devices            |       |

| Cannot Launch MegaWizard Plug-In Manager by Opening Example Design         |       |

| Example Design May Not Compile for IP Cores from Earlier Versions          |       |

| Calibration Failure in Earlier Versions                                    |       |

| SOPC Builder-generated Systems Cannot Serve as Top-Level Design            |       |

| Higher Delays and Skews Expected for Corner I/Os in Stratix V Devices      |       |

| Simulation Fails—PLL Clocks Out of Synchronization                         |       |

| Selecting VHDL Gives a Verilog HDL IP Core                                 |       |

| Incorrect Clock Uncertainty                                                |       |

| BSF File Not Generated                                                     |       |

| Global Signal Assignments Not Applied                                      |       |

| UniPHY DQS Clock Buffer Location                                           |       |

| IP Functional Simulation Model                                             |       |

| No Link to User Guide from Wizard                                          | 28–13 |

| Incorrect Operation of Waitrequest Signal                                  | 28–13 |

| User Guide States Support for ×72 Devices                                  | 28–13 |

| –18 Presets Give Errors                                                    |       |

| tQKH Parameter Incorrect                                                   |       |

### Chapter 29. SDI

| Revision History                                                                          | 29–1       |

|-------------------------------------------------------------------------------------------|------------|

| Errata                                                                                    |            |

| Duplex Operation Mode Does Not Support Spread Spectrum Clocking Feature                   | 29–2       |

| HD-SDI Dual Link RX Data Misaligns When Cable Connection is Interrupted                   |            |

| rx_status Signal Not Reliable in HD-SDI Dual Link Receiver                                | 29–3       |

| The Quartus II Fitter Reports Error When Separate TX and Duplex TX Are Assigned in the    | Same       |

| Transceiver Quad                                                                          | 29–3       |

| Pulse Width Violation in TimeQuest Report                                                 | 29–3       |

| Quartus II Fitter Reports Error When Multiple Channels in One Transceiver Quad Use More   | e than One |

| Reference Clock                                                                           | 29–4       |

| The Quartus II Design Assistant Reports Critical Warning                                  | 29–5       |

| Quartus II Fitter Reports Error When PLL-Generated Clock of 67.5 MHz Is Used in Stratix G | X Devices  |

| 29–5                                                                                      |            |

| NativeLink Fails With ModelSim Simulator                                                  | 29–6       |

| Timing Not Met in C5 Speed Grade Stratix II GX Devices                                    | 29–6       |

#### Chapter 30. SerialLite II

| Revision History                                                          |  |

|---------------------------------------------------------------------------|--|

| Errata                                                                    |  |

| The Quartus II Software Indicates Support for Arria II GX as Preliminary  |  |

| Designs with Frequency Offset Tolerance Enabled Fail Testbench Simulation |  |

| The Quartus II Design Assistant Reports Critical Warning                  |  |

### Chapter 31. Triple Speed Ethernet

| Revision History                                                   |  |

|--------------------------------------------------------------------|--|

| Errata                                                             |  |

| Late Collision in Half-Duplex 10/100-Mbps Ethernet MAC             |  |

| Packet Loss in 8-bit Internal FIFO Buffer                          |  |

| Speed Change Causes Corrupt Packet                                 |  |

| Statistics Counters Issues                                         |  |

| Continuous Data Transmission from MAC Function                     |  |

| Half-Duplex Mode Post Collision Issues                             |  |

| Transceiver Quad Sharing Failure                                   |  |

| PLL Sharing Problem for LVDS Channels                              |  |

| Reset Synchronization Problem                                      |  |

| MII Local Loopback Failure                                         |  |

| Compilation Targeting a Stratix V Device Fails                     |  |

| Simulation Fails for Hardcopy IV GX Designs                        |  |

| Corrupted Packets in 10/100-Mbps Designs with GXB Transceiver      |  |

| Serial Loopback is Enabled by Default in Cyclone IV GX Devices     |  |

| Unstable Designs with LVDS in Hardware                             |  |

| Timing Not Met in Cyclone III Devices                              |  |

| Non-Compliant Implementation of Bit PAGE_RECEIVE in PCS Register   |  |

| Non-Compliant Implementation of aAlignmentError Statistics Counter |  |

|                                                                    |  |

### Chapter 32. Video and Image Processing Suite

| Revision History                                                                          |       |

|-------------------------------------------------------------------------------------------|-------|

| Errata                                                                                    | 32–2  |

| Compilation Targeting a Stratix V Device Fails                                            | 32–2  |

| Signed Vertical Coefficients and Unsigned Horizontal Coefficients (or Vice Versa) with Su | um of |

| Coefficients More Than 1 Cause Scaler II to Generate Incorrect Output                     | 32–3  |

| Scaler II Generates Incorrect Output When Vertical Filter Taps is 3                       | 32–4  |

| Scaler II Generates Incorrect Output When Receiving Empty Packets                         |       |

| Deinterlacer and Frame Buffer Connected to DDR3 May Not Work Properly                     |       |

| Compilation Fails on the Windows 7 or Vista Operating System                              | 32–5  |

| Compilation Errors with the Frame Buffer                                                  |       |

| Frame Buffer and Deinterlacer are Missing Entry in .sdc File                              | 32–6  |

| Clocked Video Output Incorrectly Aligns Start of Frame (vid_sof)                          | 32–7  |

| Scaler: Number of Colour Planes Incorrect                                                 | 32–7  |

| RTL Simulation Reports Errors When Using Verilog HDL                                      |       |

| Incorrect Simulation Models Created for Deinterlacer and Frame Buffer                     | 32–8  |

| Deinterlacer and Test Pattern Generator May Not Upgrade                                   | 32–9  |

| The 2D Median Filter Does Not Support 7×7 Filter Size                                     | 32–9  |

| Packets Sent to VIP Cores Must Have Non-Empty Payload                                     | 32–10 |

| SOPC Builder Avalon-ST Adapter Does Not Support Avalon-ST Video                           |       |

| Scalar Coefficients Preview Window Cannot be Closed                                       |       |

| Precision Must be Set When Using Lanczos Coefficients in Scaler                           | 32–11 |

| Cyclone II M4K Fails in Alpha Blending Mixer and Gamma Corrector                          | 32–12 |

|                                                                                           |       |

#### Chapter 33. Viterbi Compiler

| Revision History                                                           | 33–1   |

|----------------------------------------------------------------------------|--------|

| Errata                                                                     | 33–1   |

| Compilation Targeting a Stratix V Device Fails                             |        |

| Testbench ber_clear Signal is Not Connected                                |        |

| Gate-Level Simulation Fails                                                |        |

| Chapter 34. XAUI PHY                                                       |        |

| Revision History                                                           | 34–1   |

| Errata                                                                     | 34–1   |

| Mixed Language Simulation Fails when Optimization Is On                    |        |

| TimeQuest Timing Analyzer Might Improperly Report Setup Violations         |        |

| Incorrect Addresses for XAUI Reset, RX and TX Control and Status Registers |        |

| Additional Information                                                     |        |

| How to Contact Altera                                                      | Info-1 |

| Typographic Conventions                                                    |        |

# **About These Release Notes**

These release notes cover versions 9.1 through 10.1 of the Altera<sup>®</sup> MegaCore<sup>®</sup> IP Library. The chapters in these release notes describe the revision history and errata for each product in the MegaCore IP Library.

From v8.0 onwards, this document replaces all individual IP product release notes and errata sheets that Altera previously published.

Errata are functional defects or errors, which may cause the product to deviate from published specifications. Documentation issues include errors, unclear descriptions, or omissions from current published specifications or product documents.

The product errata tables use the following indicators:

- A checkmark "✓" indicates an issue is applicable to that version

- "Fixed" indicates the issue was fixed in that version

- A dash "—" indicates the issue is not applicable to that version

- **For the most up-to-date errata for this release, refer to the latest version of the** *MegaCore IP Library Release Notes* on the Altera website.

**For more information about Quartus**<sup>®</sup> II issues, refer to the *Quartus II Software Release Notes*.

# **Trademarks**

These release notes use the following Altera trademarks:

- Arria<sup>®</sup> devices

- Avalon<sup>®</sup> interface

- Cyclone<sup>®</sup> devices

- HardCopy<sup>®</sup> devices

- MegaCore function

- MegaWizard<sup>™</sup> Plug-In

- ModelSim<sup>®</sup> simulator

- Nios<sup>®</sup> II processor

- Quartus II software

- SignalTap<sup>®</sup> II logic analyzer

- Stratix<sup>®</sup> devices

# **System Requirements**

The MegaCore IP Library is distributed with the Quartus II software and downloadable from the Altera website, www.altera.com.

For system requirements and installation instructions, refer to *Altera Software Installation and Licensing*.

# **Revision Dates**

The chapters in this document, MegaCore IP Library Release Notes and Errata, were revised on the following dates.

| Chapter 1.  | 8B10B Encode<br>Revised:  | er/Decoder<br>15 December 10                            |

|-------------|---------------------------|---------------------------------------------------------|

| Chapter 2.  | 10GBASE-R P<br>Revised:   | PHY<br>15 January 2011                                  |

| Chapter 3.  | 10-Gbps Ether<br>Revised: | rnet MAC<br>15 December 2010                            |

| Chapter 4.  | ASI<br>Revised:           | 15 February 2011                                        |

| Chapter 5.  | CIC<br>Revised:           | 15 March 2011                                           |

| Chapter 6.  | CPRI<br>Revised:          | 15 March 2011                                           |

| Chapter 7.  | CRC Compile<br>Revised:   | r<br>15 December 10                                     |

| Chapter 8.  | DDR and DD<br>Revised:    | R2 SDRAM Controller Compiler<br>15 December 10          |

| Chapter 9.  | DDR and DD<br>Revised:    | R2 SDRAM Controllers with ALTMEMPHY IP 15 December 2010 |

| Chapter 10. | DDR2 and DI<br>Revised:   | DR3 SDRAM Controller with UniPHY 15 January 2011        |

| Chapter 11. | DDR3 SDRAM<br>Revised:    | M Controller with ALTMEMPHY IP<br>15 December 2010      |

| Chapter 12. | FFT<br>Revised:           | 15 March 2011                                           |

| Chapter 13. | FIR Compiler<br>Revised:  |                                                         |

| Chapter 14. | FIR Compiler              | Π                                                       |

|             | Revised:                   | 15 December 2010                                 |

|-------------|----------------------------|--------------------------------------------------|

| Chapter 15. | Interlaken<br>Revised:     | 15 January 2011                                  |

| Chapter 16. | Interlaken PH<br>Revised:  |                                                  |

| Chapter 17. | NCO<br>Revised:            | 15 March 2011                                    |

| Chapter 18. | Nios II Proces<br>Revised: |                                                  |

| Chapter 19. | PCI Compiler<br>Revised:   | 15 February 2011                                 |

| Chapter 20. | PCI Express C<br>Revised:  | Compiler<br>15 March 2011                        |

| Chapter 21. | POS-PHY Lev<br>Revised:    |                                                  |

| Chapter 22. | QDRII SRAM<br>Revised:     |                                                  |

| Chapter 23. | QDR II and Q<br>Revised:   | DR II+ SRAM Controller with UniPHY 15 March 2011 |

| Chapter 24. | RapidIO<br>Revised:        | 15 March 2011                                    |

| Chapter 25. | Reed-Solomo<br>Revised:    | n Compiler<br>15 March 2011                      |

| Chapter 26. | Reed-Solomo<br>Revised:    | n II<br>15 December 2010                         |

| Chapter 27. | RLDRAM II<br>Revised:      | 15 December 10                                   |

| Chapter 28. | RLDRAM II C<br>Revised:    | Controller with UniPHY<br>15 March 2011          |

| Chapter 29. | SDI<br>Revised:            | 15 February 2011                                 |

| Chapter 30. | SerialLite II<br>Revised:  | 15 February 2011                                 |

| Chapter 31  | Triple Speed 1             | Ethernet                                         |

Chapter 31. Triple Speed Ethernet Revised: 15 March 2011

Chapter 32. Video and Image Processing Suite

| Chapter 33. | Viterbi Comp<br>Revised: | iler<br>15 March 2011 |

|-------------|--------------------------|-----------------------|

| Chapter 34. | XAUI PHY<br>Revised:     | 15 December 2010      |

15 March 2011

Revised:

# **Revision History**

Table 1–1 shows the revision history for the 8B10B Encoder/Decoder MegaCore function.

**For more information about the new features, refer to the** *8B10B Encoder/Decoder* MegaCore Function User Guide.

| Table 1–1. 8B10B Encoder/ | Decoder MegaCore Function | Revision History |

|---------------------------|---------------------------|------------------|

|---------------------------|---------------------------|------------------|

| Version | Date          | Description                                                     |

|---------|---------------|-----------------------------------------------------------------|

| 10.1    | December 2010 | Final support for Stratix IV GT devices.                        |

| 10.0    | July 2010     | Maintenance release.                                            |

| 9.1     | November 2009 | Preliminary support for Cyclone III LS and Cyclone IV devices.  |

| 9.0 SP1 | May 2009      | Preliminary support for HardCopy III and HardCopy IV E devices. |

| 9.0     | March 2009    | Preliminary support for Arria II GX device family.              |

# **Errata**

No known issues in v10.1, v10.0, and 9.1.

# **Revision History**

Table 2–1 shows the revision history for the 10GBASE-R PHY IP core.

**For more information about the new features, refer to the "10GBASE-R PHY IP Core"** chapter in the *Altera Transceiver PHY IP Core User Guide*.

Table 2–1. 10GBASE-R PHY Revision History

| Version  | Date           | Description               |

|----------|----------------|---------------------------|

| 10.1     | December 2010  | Added Stratix V support.  |

| 10.0 SP1 | September 2010 | Added simulation support. |

| 10.0     | July 2010      | First release.            |

# Errata

Table 2–2 shows the issues that affect the 10GBASE-R PHY IP core versions 10.1 and 10.0.

Table 2–2.

10GBASE-R PHY Errata

| Added or   | Issue                                                                  |              | Affected Version |  |

|------------|------------------------------------------------------------------------|--------------|------------------|--|

| Updated    |                                                                        |              | 10.0             |  |

| 15 Jan 11  | FIFO Full Signals Are Swapped                                          | $\checkmark$ | $\checkmark$     |  |

| 10 Jali 11 | rx_ready Bit Does not Update When Synchronization Is Lost              | $\checkmark$ | $\checkmark$     |  |

| 15 Dec 10  | Incorrect Device Support Listed 10GBASE-R PHY IP Core User Guide Fixed |              | $\checkmark$     |  |

| 15 Dec 10  | Mixed Language Simulation Fails when Optimization Is On                |              | _                |  |

# **FIFO Full Signals Are Swapped**

The TX\_FIFO\_FULL and RX\_FIFO\_FULL status bits are swapped.

### **Affected Configurations**

This issue affects Stratix IV and Stratix V implementations of the 10GBASE-R PHY.

#### Workaround

The workaround is to note that for the 10.1 release  $RX\_FIFO\_FULL$  is actually stored as bit 3 of address 0x82 and  $TX\_FIFO\_FULL$  is stored as bit 4 of address 0x82.

#### **Solution Status**

This issue will be fixed in a future version of the 10GBASE-R PHY IP core.

# rx\_ready Bit Does not Update When Synchronization Is Lost

The RX\_DATA\_READY which is bit 7 of the PCS status register (0x82) does not deassert when synchronization is lost.

#### **Affected Configurations**

This issue affects both Stratix IV and Stratix V implementations of the 10GBASE–R PHY.

#### Workaround

The workaround is to monitor the internal signals that indicate lock status and perform a digital reset of the channel when synchronization is lost.

#### **Solution Status**

This issue will be fixed in a future version of the 10GBASE-R PHY IP core.

# **Incorrect Device Support Listed 10GBASE-R PHY IP Core User Guide**

The 10GBase-R PHY IP Core chapter of the Altera Transceiver PHY IP Core User Guide states that the 10GBASE-R IP Core provides final support for the Stratix IV E device family; however, the 10GBASE-R PHY IP core provides no support for Stratix IV E devices.

#### **Affected Configurations**

This is a documentation error only.

#### Workaround

No workaround is required.

#### **Solution Status**

This issue is fixed in version 10.1 of the Altera Transceiver PHY IP Core User Guide.

### **Mixed Language Simulation Fails when Optimization Is On**

Simulation fails when using ModelSim with mixed-languages.

#### **Affected Configurations**

This issue affects mixed language simulation including Verilog modules and VHDL entities when optimization is on.

#### Workaround

The work around is to turn ModelSim optimization off by using the <code>-novpt</code> option to the <code>vsim</code> command.

#### **Solution Status**

This issue may be fixed in a future version of ModelSim.

# **Revision History**

Table 3–1 shows the revision history for the 10-Gbps Ethernet MAC MegaCore function.

For more information about the new features, refer to the 10-*Gbps Ethernet MAC MegaCore Function User Guide*.

Table 3–1. 10-Gbps Ethernet MAC MegaCore Function Revision History

| Version            | Date                                                                           | Description                                                               |

|--------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 10.1 December 2010 | <ul> <li>Preliminary support for Arria Ii GZ and Stratix V devices.</li> </ul> |                                                                           |

| 10.1               | December 2010                                                                  | <ul> <li>Final support for Arria II GX and Stratix IV devices.</li> </ul> |

| 10.0               | July 2010                                                                      | Initial release.                                                          |

# Errata

Table 3–2 shows the issues that affect the 10-Gbps Ethernet MAC MegaCore function v10.0.

#### Table 3–2. 10-Gbps Ethernet MAC MegaCore Function Errata

| Added or   | Issue                                               | Affected Version |  |

|------------|-----------------------------------------------------|------------------|--|

| Updated    | 13500                                               | 10.0             |  |

| 15 July 10 | No Length Checking for VLAN and Stacked VLAN Frames |                  |  |

| 15 July 10 | Simulation Not Supported for Stratix V Designs      | $\checkmark$     |  |

# **No Length Checking for VLAN and Stacked VLAN Frames**

The IP core does not perform length checking on all VLAN and stacked VLAN frames.

### **Affected Configuration**

All configurations.

#### Workaround

None.

#### **Solution Status**

This issue will be fixed in a future version of the 10-Gbps Ethernet MAC MegaCore function.

<sup>....</sup>

# **Simulation Not Supported for Stratix V Designs**

The IP core does not support simulation for designs that target Stratix V devices.

### **Affected Configuration**

All configurations.

#### Workaround

None.

#### **Solution Status**

This issue will be fixed in a future version of the 10-Gbps Ethernet MAC MegaCore function.

# **Revision History**

Table 4–1 shows the revision history for the ASI MegaCore function.

**For more information about the new features, refer to the** *ASI MegaCore Function User Guide*.

| Version  | Date          | Description                                                                  |

|----------|---------------|------------------------------------------------------------------------------|

| 10.1 SP1 | February 2011 | Maintenance release.                                                         |

| 10.1     | December 2010 | <ul> <li>Preliminary support for Arria II GZ devices.</li> </ul>             |

| 10.1     | December 2010 | <ul> <li>Final support for Arria II GX devices.</li> </ul>                   |

| 10.0     | July 2010     | Maintenance release.                                                         |

| 9.1      | November 2009 | Preliminary support for Cyclone III LS and Cyclone IV (soft SERDES) devices. |

| 9.0 SP2  | July 2009     | Maintenance release.                                                         |

| 9.0 SP1  | May 2009      | Maintenance release.                                                         |

| 9.0      | March 2009    | Preliminary support for Arria II GX devices.                                 |

| 8.1      | November 2008 | Maintenance release.                                                         |

Table 4–1. ASI MegaCore Function Revision History

# Errata

Table 4–2 shows the issues that affect the ASI MegaCore function v10.1, 10.0, and 9.1.

Not all issues affect all versions of the ASI MegaCore function.

| Table 4–2. | ASI MegaCore Function E | rrata |

|------------|-------------------------|-------|

|------------|-------------------------|-------|

| Added or  | Issue                                                                   |   | Affected Version |              |  |

|-----------|-------------------------------------------------------------------------|---|------------------|--------------|--|

| Updated   |                                                                         |   | 10.0             | 9.1          |  |

| 15 Feb 11 | ASI Does Not Support VHDL Functional Simulation Model for Cyclone IV GX |   | —                | _            |  |

| 15 Dec 10 | ASI 10.1 Does Not Support Qsys                                          |   | —                | _            |  |

| 01 Dec 06 | NativeLink Does Not Support Gate-Level Simulation                       | ~ | $\checkmark$     | $\checkmark$ |  |

# **ASI Does Not Support VHDL Functional Simulation Model for Cyclone IV GX**

Serial loopback designs that target Cyclone IV GX devices using the VHDL functional simulation model fail to simulate.

### **Affected Configurations**

This issue only affects designs that target Cyclone IV GX devices using the VHDL functional simulation model.

#### **Design Impact**

The design fails to simulate using the VHDL functional simulation model.

#### Workaround

Use the Verilog HDL functional simulation model instead.

#### **Solution Status**

This issue will be fixed in a future version of the ASI MegaCore function.

# **ASI 10.1 Does Not Support Qsys**

You will not be able to generate the ASI MegaCore function v10.1 using Qsys. Adding the ASI MegaCore function in a Qsys system triggers the following warning message: ASI does not support Qsys-compatible generation.

### **Affected Configurations**

This issue affects all configurations.

#### **Design Impact**

The design will not generate successfully in Qsys.

#### Workaround

Use SOPC Builder instead.

#### **Solution Status**

This issue will be fixed in a future version of the ASI MegaCore function.

# **NativeLink Does Not Support Gate-Level Simulation**

When using the NativeLink simulation example, the gate-level simulation design fails.

#### **Affected Configurations**

This issue affects all simulators supported by NativeLink.

#### **Design Impact**

This issue only affects simulation and does not affect the design compilation.

#### Workaround

Perform an RTL simulation of the NativeLink simulation example.

#### **Solution Status**

This issue will be fixed in a future version of the ASI MegaCore function.

# **Revision History**

Table 5–1 shows the revision history for the CIC MegaCore function.

**For information about the new features, refer to the** *CIC MegaCore Function User Guide*.

Table 5–1. CIC MegaCore Function Revision History

| Version            | Date          | Description                                                                                         |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------|

| 10.1               | December 2010 | <ul> <li>Preliminary support for Arria II GZ devices.</li> </ul>                                    |

| TU.I December 2010 | December 2010 | <ul> <li>Final support for Stratix IV GT devices.</li> </ul>                                        |

| 10.0               | July 2010     | Preliminary support for Stratix V devices.                                                          |

| 9.1 SP2            | March 2010    | Maintenance release.                                                                                |

| 9.1 SP1            | February 2010 | Maintenance release.                                                                                |

| 0.1                | November 2009 | <ul> <li>Preliminary support for HardCopy IV GX, Stratix IV, and Cyclone III LS devices.</li> </ul> |

| 9.1                | November 2009 | <ul> <li>Withdrawn support for HardCopy family of devices.</li> </ul>                               |

# **Errata**

Table 5–2 shows the issues that affect the CIC MegaCore function v10.1, v10.0, v9.1 SP2, v9.1 SP1, and v9.1.

Table 5–2. CIC MegaCore Function Errata

| Added or<br>Updated | Issue                                                                           | Affected Version |       |            |            |     |  |

|---------------------|---------------------------------------------------------------------------------|------------------|-------|------------|------------|-----|--|

|                     |                                                                                 | 10.1             | 10.0  | 9.1<br>SP2 | 9.1<br>SP1 | 9.1 |  |

| 15 Mar 11           | Compilation Targeting a Stratix V Device Fails                                  | $\checkmark$     | —     | _          |            | —   |  |

| 15 July 10          | Error Generating HDL for Decimator with More Than 9 Stages and 11<br>Interfaces | _                | Fixed | ~          | ~          | ~   |  |

| 1 Apr 10            | OpenCore Plus Feature Not Supported for Cyclone IV E and Cyclone IV GX Devices  |                  | _     | Fixed      | ~          |     |  |

# **Compilation Targeting a Stratix V Device Fails**

Designs that include a CIC IP core and target a Stratix V device, do not compile even if you have a valid license for the IP core. Refer to Altera solution rd03082011\_116 at www.altera.com/support/kdb/solutions/rd03082011\_116.html.

### **Affected Configurations**

CIC IP core designs that target a Stratix V device.

#### **Design Impact**

Designs that include this IP core and target a Stratix V device cannot compile.

#### Workaround

To fix this issue, if you have a valid license for this IP core, follow these steps:

- 1. Upgrade your Quartus II software installation to the 10.1 Service Pack 1 version.

- 2. Apply Patch 1.19 to your Quartus II software installation.

- 3. Regenerate your IP core and any others in your design that are affected by this issue.

- 4. Recompile your design.

#### **Solution Status**

This issue will be fixed in a future version of the Quartus II software.

# Error Generating HDL for Decimator with More Than 9 Stages and 11 Interfaces

An error is issued when you generate HDL after selecting a **Decimator** filter with **Number of Stages** set to more than **9** and **Number of Interface** to more than **11**.

### **Affected Configurations**

Decimator filters with more than 9 stages and more than 11 interfaces.

#### **Design Impact**

An error is issued when you generate HDL.

#### Workaround

If you want more than 9 stages you must select 11 interfaces or fewer. If you want more than 11 interfaces you must choose 9 stages or fewer.

#### **Solution Status**

This issue is fixed in version 10.0 of the CIC MegaCore function.

### **OpenCore Plus Feature Not Supported for Cyclone IV E and Cyclone IV GX Devices**

When using the OpenCore Plus evaluation feature, the CIC MegaCore function does not generate a functional simulation model for Cyclone IV E and Cyclone IV GX devices.

#### **Affected Configurations**

All CIC variations that target a Cyclone IV E device or a Cyclone IV GX device.

#### **Design Impact**

This issue has no design impact.

#### Workaround

To avoid this issue, purchase a license for the CIC MegaCore function.

#### **Solution Status**

This issue is fixed in version 9.1 SP2 of the CIC MegaCore function.

# 6. CPRI

# **Revision History**

Table 6–1 shows the revision history for the CPRI MegaCore function.

**For information about the new features, refer to the** *CPRI MegaCore Function User Guide.*

| Version  | Date          | Description                                                                                                                                                               |  |  |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10.1 SP1 | February 2011 | Maintenance release.                                                                                                                                                      |  |  |

| 10.1     | December 2010 | <ul> <li>Added support for Arria II GZ devices.</li> </ul>                                                                                                                |  |  |

|          |               | <ul> <li>Added support for additional CPRI data rates in Arria II GX devices.</li> </ul>                                                                                  |  |  |

|          |               | <ul> <li>Added scrambler/descrambler support.</li> </ul>                                                                                                                  |  |  |

|          |               | <ul> <li>Added CPU interrupt for remote hardware reset.</li> </ul>                                                                                                        |  |  |

| 10.0     | July 2010     | <ul> <li>Added support for Cyclone IV GX devices.</li> </ul>                                                                                                              |  |  |

|          |               | <ul> <li>Added GUI parameter to enable auto-rate negotiation and two signals to support visibility<br/>of the feature status.</li> </ul>                                  |  |  |

|          |               | <ul> <li>Enhanced testbench suite to include two new testbenches, to demonstrate operation with<br/>no MAP interface and to demonstrate auto-rate negotiation.</li> </ul> |  |  |

| 9.1 SP2  | March 2010    | Maintenance release.                                                                                                                                                      |  |  |

| 9.1 SP1  | February 2010 | Initial release.                                                                                                                                                          |  |  |

Table 6-1. CPRI MegaCore Function Revision History

# Errata

Table 6–2 shows the issues that affect the CPRI MegaCore function v10.1 SP1, v10.1, v10.0, and v9.1 SP2. Issues that affect v9.1 SP1 are available in a **readme.txt** file that accompanies the CPRI MegaCore function v9.1 SP1 patch.

Not all issues affect all versions of the CPRI MegaCore function. Altera recommends upgrading to the latest available version of the MegaCore IP Library.

Table 6-2. CPRI MegaCore Function Errata (Part 1 of 2)

| Added or<br>Updated | Issue                                                         | Affected Version |              |      |         |  |  |

|---------------------|---------------------------------------------------------------|------------------|--------------|------|---------|--|--|

|                     |                                                               | 10.1 SP1         | 10.1         | 10.0 | 9.1 SP2 |  |  |

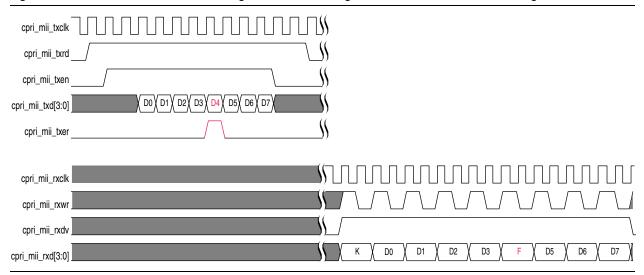

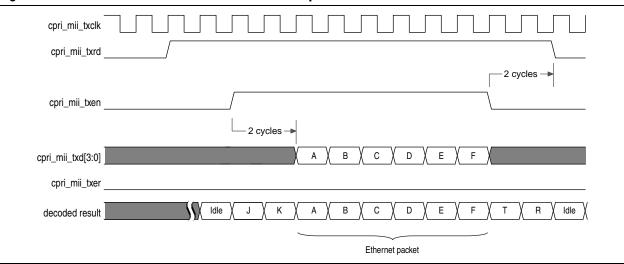

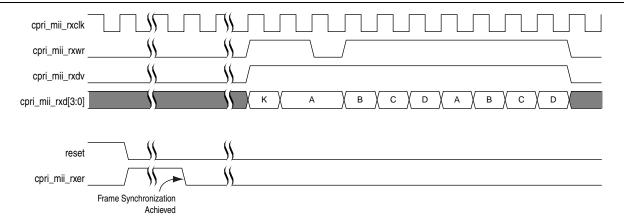

| 15 Mar 11           | MII Interface Description in v10.1 User Guide Contains Errors | $\checkmark$     | $\checkmark$ |      |         |  |  |

| Added or<br>Updated | Issue                                                                                                                        | Affected Version |              |              |              |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|--------------|--------------|--|

|                     |                                                                                                                              | 10.1 SP1         | 10.1         | 10.0         | 9.1 SP2      |  |

|                     | CPRI Protocol Version Default Value is Invalid                                                                               | $\checkmark$     | $\checkmark$ | —            | —            |  |

|                     | CPU Interface Deadlocks After Attempt to Access Ethernet or HDLC<br>Registers When MII Interface Enabled                     | Fixed            | ~            | $\checkmark$ | ~            |  |

| 15 Feb 11           | Errors in .mif File Names in Auto-rate Negotiation Testbenches                                                               | Fixed            | $\checkmark$ |              | —            |  |

|                     | Testbench tb_altera_cpri.vhd Does Not Simulate                                                                               | Fixed            | $\checkmark$ | —            | —            |  |