# Using Differential I/O Standards in MAX V Devices

AN-636-1.0 Application Note

This application note describes using differential I/O standards in MAX® V devices.

High-speed differential I/O standards have become popular in high-speed interfaces because of their significant advantages over the single-ended I/O standards. The Altera® MAX V device family supports the emulated LVDS output (LVDS\_E\_3R) and emulated reduced swing differential signaling (RSDS) output (RSDS\_E\_3R) I/O standards using two single-ended outputs and external resistor networks, with the second output programmed as an inverted output.

This application note contains the following sections:

- "Emulated LVDS Output (LVDS\_E\_3R) I/O Standard" on page 1

- "Emulated RSDS Output (RSDS\_E\_3R) I/O Standard" on page 2

- "I/O Resources" on page 3

- "Software Overview" on page 4

## Emulated LVDS Output (LVDS\_E\_3R) I/O Standard

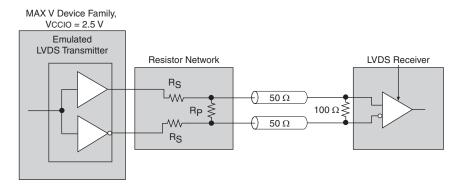

MAX V devices support the emulated LVDS transmitter with a data rate up to 304 Mbps using two single-ended output buffers with external resistors. One of the single-ended output buffers is programmed to have an opposite polarity. The LVDS receiver requires an external  $100~\Omega$  termination resistor between the two signals at the input buffer.

Figure 1 shows a point-to-point LVDS interface with a MAX V device using two single-ended output buffers and external resistors.

Figure 1. LVDS Interface with the External Resistor Network for MAX V Devices (Note 1)

#### Note to Figure 1:

(1)  $R_S = 120 \Omega$ ;  $R_P = 170 \Omega$

101 Innovation Drive San Jose, CA 95134 www.altera.com © 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera acustomers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

MAX V devices meet the ANSI/TIA/EIA-644 requirement standard.

For more information about the emulated LVDS output electrical specifications for MAX V devices, refer to the *DC and Switching Characteristics for MAX V Devices* chapter in the *MAX V Device Handbook*.

## Emulated RSDS Output (RSDS\_E\_3R) I/O Standard

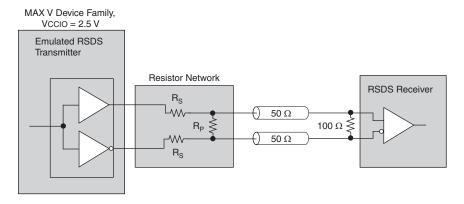

MAX V devices support emulated RSDS transmitter with a data rate up to 200 Mbps using two single-ended output buffers with external resistors. The two single-ended output buffers are programmed to have an opposite polarity.

Figure 2 shows a point-to-point RSDS interface with a MAX V device using two single-ended output buffers and external resistors.

Figure 2. RSDS Interface with the External Resistor Network for MAX V Devices (Note 1)

#### Note to Figure 2:

(1)  $R_S = 120 \Omega$ ;  $R_P = 170 \Omega$

MAX V devices meet the National Semiconductor Corporation RSDS Interface Specification.

For more information about the emulated RSDS output electrical specifications for MAX V devices, refer to the *DC and Switching Characteristics for MAX V Devices* chapter in the *MAX V Device Handbook*.

When using emulated transmitters, you must use a resistor network to attenuate the output voltage swing to meet RSDS specifications. You can modify the resistor network values to reduce power or improve the noise margin.

The resistor values chosen must satisfy Equation 1.

#### Equation 1.

$$\frac{Rs \times \frac{Rp}{2}}{Rs + \frac{Rp}{2}} = 50\Omega$$

I/O Resources Page 3

Altera recommends performing simulations using MAX V devices IBIS models to validate that custom resistor values meet the RSDS specifications.

## I/O Resources

The number of differential output channels varies across device densities and packages. Table 1 lists the number of emulated LVDS and RSDS channels in MAX V devices across various device densities and packages.

Table 1. LVDS and RSDS Channels Supported in MAX V Devices (Note 1)

| Device  | 64-Pin<br>MBGA | 64-Pin<br>EQFP | 68-Pin<br>MBGA | 100-Pin<br>TQFP | 100-Pin<br>MBGA | 144-Pin<br>TQFP | 256-Pin<br>FBGA | 324-Pin<br>FBGA |

|---------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 5M40Z   | 10 eTx         | 20 eTx         | _              | _               | _               | _               | _               | _               |

| 5M80Z   | 10 eTx         | 20 eTx         | 20 eTx         | 33 eTx          | _               | _               | _               | _               |

| 5M160Z  | _              | 20 eTx         | 20 eTx         | 33 eTx          | 33 eTx          | _               | _               | _               |

| 5M240Z  | _              | _              | 20 eTx         | 33 eTx          | 33 eTx          | 49 eTx          | _               | _               |

| 5M570Z  | _              | _              | _              | 28 eTx          | 28 eTx          | 49 eTx          | 75 eTx          | _               |

| 5M1270Z | _              | _              | _              | _               | _               | 42 eTx          | 90 eTx          | 115 eTx         |

| 5M2210Z | _              | _              |                | _               | _               | _               | 83 eTx          | 115 eTx         |

#### Note to Table 1:

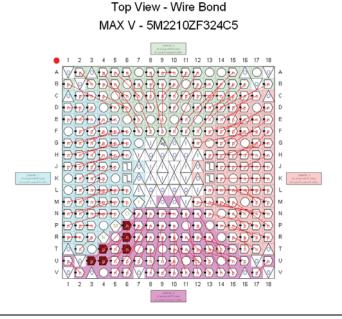

Emulated differential output channels are identified as the DIFFIO\_<channel\_number>[p/n] pins in the **Emulated LVDS Output Channel** column in the MAX V Device Pin-Out.

You can also use the Quartus<sup>®</sup> II Pin Planner Package view to ease differential I/O assignment planning. On the View menu, click **Show Differential Pin Pair Connections** to highlight the differential pin pairing. The differential pin pairs are connected with red lines. For the differential pins, you only need to assign the signal to a positive pin. If the positive pin is assigned with a differential I/O standard, the negative pin is automatically assigned by the Quartus II software.

<sup>(1)</sup> eTX = emulated LVDS output buffers (LVDS\_E\_3R) or emulated RSDS output buffers (RSDS\_E\_3R).

Page 4 Software Overview

Figure 3 shows the differential pin pair connections in the Quartus II Pin Planner for MAX V devices.

Figure 3. Differential Pin Pair Connections in the Quartus II Pin Planner for MAX V Devices

### **Software Overview**

MAX V devices high-speed I/O system interfaces are created in the core logic by the Quartus II software megafunction. The Quartus II software allows you to design your high-speed transmitter using the ALTLVDS\_TX megafunction. This megafunction is optimized to use the MAX V device family resources to create high-speed I/O interfaces in the most effective manner.

When you are using MAX V devices with the ALTLVDS\_TX megafunction, the interface always sends the MSB of your parallel data first.

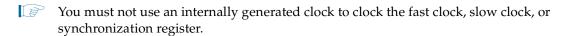

In MAX V devices, one ALTLVDS\_TX instance can support up to 18 channels with a deserialization factor of 1 to 10. The ALTLVDS\_TX instance in MAX V devices is supported in external phase-locked loop (PLL) mode. A synchronization register must be added before the transmitter megafunction.

Software Overview Page 5

Table 2 lists the details of clock generated by the external PLL.

Table 2. Clock Generated by the External PLL

| Clock Name                                     | Clock Frequency                        |                                    |  |  |

|------------------------------------------------|----------------------------------------|------------------------------------|--|--|

| GIUCK NAME                                     | Odd Deserialization Factor             | <b>Even Deserialization Factor</b> |  |  |

| Fast clock, connected to the tx_inclk port (1) | Data rate/2                            |                                    |  |  |

| Slow clock, connected to the tx_syncclock port | Data rate/(2 × Deserialization factor) | Data rate/Deserialization factor   |  |  |

| Clock for synchronization register             | Data rate/Deserialization factor       |                                    |  |  |

#### Note to Table 2:

(1) When the descrialization factor of 1 is selected, the tx\_inclk port is not generated. Therefore, the fast clock is not required.

The slow clock requirement is different for the even and odd deserialization factors. All the clock signals must originate from the dual-purpose clock pins, CLK [0..3], that connects to the global clock network.

To remove the board skew between the clock signals, Altera recommends having an equal trace length on the clock path from the external PLL to the CLK pin for MAX V devices.

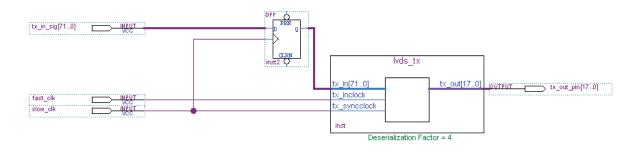

Figure 4 shows an example setup for the ALTLVDS\_TX megafunction in MAX V devices for an even deserialization factor.

Figure 4. Example Setup for an Even Deserialization Factor Using the ALTLVDS TX Megafunction in MAX V Devices

Page 6 Software Overview

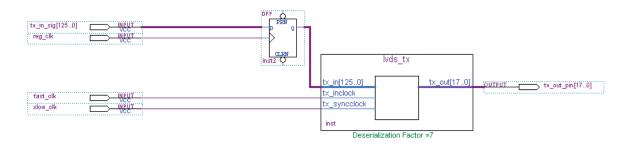

Figure 5 shows an example setup for the ALTLVDS\_TX megafunction in MAX V devices for an odd deserialization factor.

Figure 5. Example Setup for an Odd Deserialization Factor Using the ALTLVDS\_TX Megafunction in MAX V Devices

You can customize several transmitter settings using the MegaWizard™ Plug-In Manager for MAX V devices, as listed in Table 3.

Table 3. Transmitter Settings Using the MegaWizard Plug-In Manager for MAX V Devices

| Option                          | Description                                                                                                                                                                                                                                                     |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                 | Number of output channels available for the LVDS transmitter.                                                                                                                                                                                                   |  |

| What is the number of channels? | For example, if the number of channels is <b>18</b> , a tx_out [170] port is created.                                                                                                                                                                           |  |

|                                 | One ALTLVDS_TX instance can support up to 18 channels.                                                                                                                                                                                                          |  |

|                                 | Determines the number of parallel bits from the core which the transmitter serializes and sends out.                                                                                                                                                            |  |

| What is deserialization factor? | For example, if the deserialization factor is <b>10</b> and the number of output channels is <b>1</b> , the transmitter serializes every 10 parallel bits into a single output channel.                                                                         |  |

|                                 | If the descrialization factor is $\bf 5$ and the number of output channels is $\bf 18$ , a tx_in[890] port is created.                                                                                                                                          |  |

| Use tx_data_reset input port    | This option is selectable when the LVDS is implemented in the logic. When you select this option, it adds an input port to the ALTLVDS_TX megafunction, which, when asserted, performs an asynchronous reset for all the logics in the ALTLVDS_TX megafunction. |  |

## **Constraining the Transmitter Channel-to-Channel Skew**

In the TimeQuest Timing Analyzer tool, the report\_tccs and report\_rskm commands are not available for MAX V devices. You can use the set\_max\_skew command in the Synopsys Design Constraints File (.sdc) to constrain the transmitter channel-to-channel skew. After compilation completes, check the timing report in the TimeQuest Timing Analyzer to ensure your design is able to achieve the maximum skew you have specified in the .sdc file and there are no timing violations on the clock setup and hold paths.

For more information about the set\_max\_skew command, refer to *The Quartus II TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook*.

Document Revision History Page 7

## **Document Revision History**

Table 4 lists the revision history for this application note.

**Table 4. Document Revision History**

|     | Date       | Version | Changes          |

|-----|------------|---------|------------------|

| Jai | nuary 2011 | 1.0     | Initial release. |

Page 8 Document Revision History