# **External Memory Interface Handbook**

# Volume 1: Altera Memory Solution Overview and Design Flow

101 Innovation Drive San Jose, CA 95134 www.altera.com

EMI\_GS-1.0

Document last updated for Altera Complete Design Suite version: 11.1 Document publication date: November 2011

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and service at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or services are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter Revision Dates |

|------------------------|

|------------------------|

### Section I. Altera Memory Solution Overview and Design Flow

#### **Chapter 1. Introduction to Altera Memory Solution**

| Soft and Hard Memory IP   | . 1–1 |

|---------------------------|-------|

| Memory Solutions          | . 1–2 |

| Low Latency               | . 1–4 |

| Efficiency                | . 1–5 |

| Document Revision History | . 1–6 |

#### **Chapter 2. Recommended Design Flow**

| Select Your Memory                        | 2–3 |

|-------------------------------------------|-----|

| Select Your FPGA                          | 2–3 |

| Planning Pin and FPGA Resources           | 2–3 |

| Determine Board Layout                    | 2–3 |

| Implementing and Parameterizing Memory IP | 2–3 |

| Simulating Memory IP                      |     |

| Analyzing Timing of Memory IP             | 2–4 |

| Perform Post-Fit Timing Simulation        | 2–4 |

| Debugging Memory IP                       | 2–4 |

| Design Checklist                          | 2–5 |

| Document Revision History                 | 2–8 |

|                                           |     |

# **Chapter Revision Dates**

The chapters in this document, External Memory Interface Handbook, Volume 1: Altera Memory Solution Overview and Design Flow, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

- Chapter 1. Introduction to Altera Memory Solution Revised: November 2011 Part Number: EMI\_GS\_001

- Chapter 2. Recommended Design Flow Revised: November 2011 Part Number: EMI\_GS\_002

## Section I. Altera Memory Solution Overview and Design Flow

This section provides an overview of Altera memory solutions and the recommended memory IP design flow.

This section includes the following chapters:

- Chapter 1, Introduction to Altera Memory Solution

- Chapter 2, Recommended Design Flow

• For information about the revision history for chapters in this section, refer to "Document Revision History" in each individual chapter.

## 1. Introduction to Altera Memory Solution

This chapter describes the memory solutions that Altera provides.

Altera provides the fastest, most efficient, and lowest latency memory controllers. The controllers are designed to allow you to easily interface with today's higher speed memories.

Altera supports a wide variety of memory interfaces suitable for applications ranging from routers and switches to video cameras. You can easily implement Altera's intellectual property (IP) using the memory MegaCore functions through the Quartus II software. The Quartus II software also provides an external memory toolkit that helps you test the implementation of the IP in the FPGA device.

Refer to the External Memory Interface Spec Estimator page for the maximum speed that supported by Altera FPGAs.

### **Soft and Hard Memory IP**

Altera's latest devices, the 28-nm FPGAs provide two types of memory solutions: soft memory IP and hard memory IP. Arria V and Cyclone V devices offer both soft and hard memory IP, while Stratix V devices offer only soft memory IP.

The soft memory IP gives you the flexibility to design your own interfaces to meet your system requirements and still benefit from the industry leading performance. The hard memory IP is designed to give you a complete out-of-the-box experience when designing a memory controller.

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 1–1 lists the features of the soft and hard memory IP.

Table 1–1. Features of the Soft and Hard Memory IP

| Soft Memory IP                                                                                                                                                                                                                                                                                                                                                                                                                       | Hard Memory IP                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Consists of a DDR2 or DDR3 SDRAM<br/>high-performance memory controller with<br/>UniPHY IP.</li> </ul>                                                                                                                                                                                                                                                                                                                      | <ul> <li>Consists of a DDR2 or DDR3 SDRAM<br/>high-performance memory controller with a<br/>hard UniPHY IP, and a multiport front-end</li> </ul>                                                                                                                                                                                                                                                                                                    |

| <ul> <li>Has hardened read and write data paths to ensure your design meets timing at the highest speeds. The data paths include I/O, phase-locked loops (PLLs), delay-locked loop (DLL), and read and write FIFO buffers.</li> <li>Allows you to choose the location to place the memory controller and the ability to size the memory controller based on the system requirements, especially in the Stratix V devices.</li> </ul> | <ul> <li>block.</li> <li>Has a fixed location on the die and a fixed maximum width; ×32 for Arria V devices and ×16 for Cyclone V devices.</li> <li>Runs at full rate to allow decreased latency and to minimize the required bus width of signals going into the core of the device.</li> <li>Simplifies the overall memory design in Arria V and Cyclone V devices, and provides a truly out-of-the-box experience for every designer.</li> </ul> |

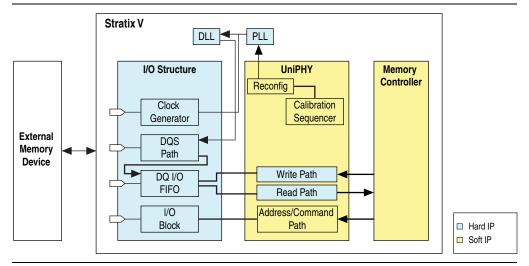

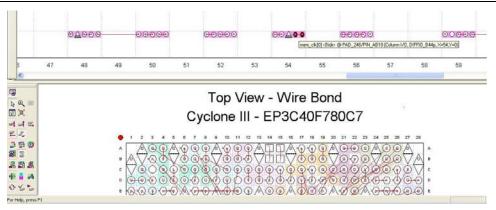

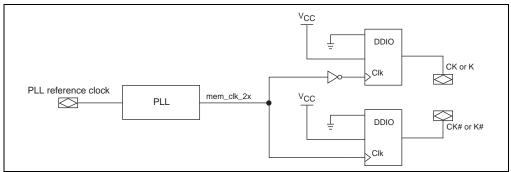

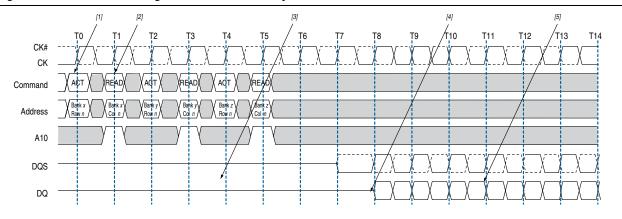

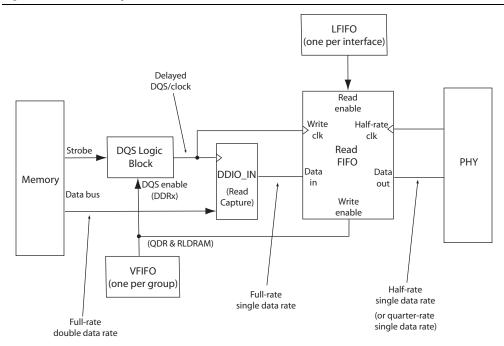

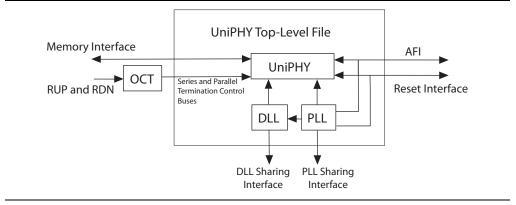

Figure 1–1 shows the hardened data paths in the soft memory IP of a Stratix V device.

### **Memory Solutions**

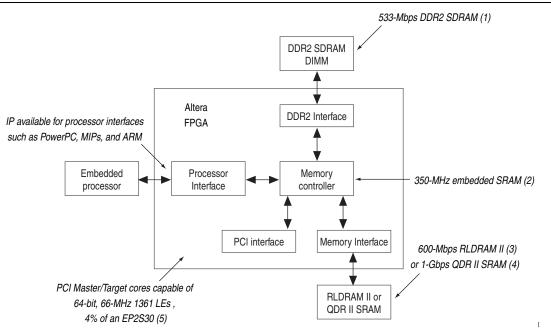

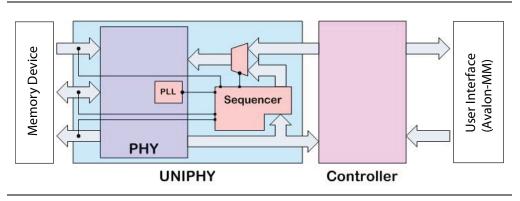

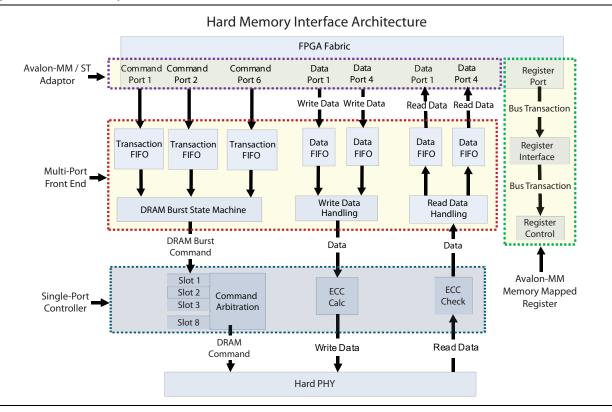

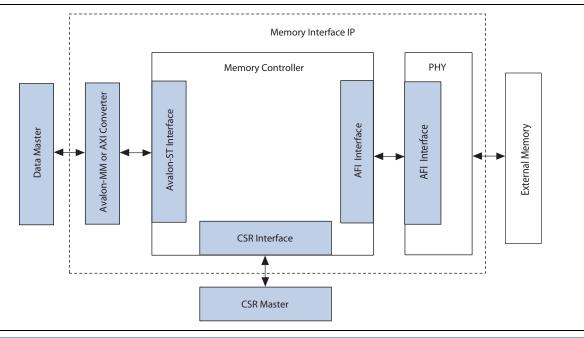

Altera FPGAs achieve optimal memory interface performance with external memory IP. The IP provides the following components:

- Physical layer interface (PHY) which handles the timing on the data path itself.

- Memory controller block which implements all the memory commands and addresses.

- Multiport front-end (MPFE) block which allows multiple processes inside the FPGA device to share a common bank of memory. The MPFE block is a new feature in Arria V and Cyclone V devices.

These blocks are critical to the design and the use of the memory interface block.

Altera provides modular memory solutions that allow you to customize your memory interface design to any of the following configurations:

- PHY with your own controller

- PHY with Altera controller

- PHY with Altera controller and the MPFE block

You can also build a custom PHY, a custom controller, or both, as desired.

Table 1–2 shows the recommended memory types and controllers that Altera offers with the PHY IP.

Table 1–2. Altera Memory Types, PHY, and Controllers in the Quartus II Software (Part 1 of 2)

| <b>Quartus II Version</b> | Memory         | PHY IP                         | Controller IP         |

|---------------------------|----------------|--------------------------------|-----------------------|

|                           | DDR/DDR2/DDR3  | ALTMEMPHY (AFI) <sup>(1)</sup> | HPC II                |

|                           | DDR2/DDR3      | UniPHY                         | HPC II                |

|                           | QDR II/QDR II+ | UniPHY                         | QDR/RLD II controller |

| 11.1                      | RLDRAM II      | UniPHY                         | QDR/RLD II controller |

|                           | Other          | ALTDQ_DQS <sup>(2)</sup>       | Custom                |

|                           | Other          | ALTDQ_DQS2 <sup>(3)</sup>      | Custom                |

|                           | DDR/DDR2/DDR3  | ALTMEMPHY (AFI)                | HPC II                |

|                           | DDR2/DDR3      | UniPHY                         | HPC II                |

| 11.0                      | QDR II/QDR II+ | UniPHY                         | QDR/RLD II controller |

| 11.0                      | RLDRAM II      | UniPHY                         | QDR/RLD II controller |

|                           | Other          | ALTDQ_DQS <sup>(2)</sup>       | Custom                |

|                           | Other          | ALTDQ_DQS2 <sup>(3)</sup>      | Custom                |

|                           |                | HPC                            |                       |

|                           | DDR/DDR2/DDR3  | ALTMEMPHY (AFI)                | HPC II                |

|                           | DDR2/DDR3      | UniPHY Nios-based Sequencer    | HPC II                |

| 10.1                      | QDR II/QDR II+ | UniPHY RTL Sequencer           | QDR/RLD II controller |

|                           | RLDRAM II      | UniPHY RTL Sequencer           | QDR/RLD II controller |

|                           | Other          | ALTDQ_DQS <sup>(2)</sup>       | Custom                |

|                           | Other          | ALTDQ_DQS2 <sup>(3)</sup>      | Custom                |

|                           | DDR/DDR2/DDR3  |                                | HPC                   |

|                           | υυκ/υυκ2/υυΚ3  | ALTMEMPHY (AFI)                | HPC II                |

|                           | DDR2/DDR3      | UniPHY Nios-based Sequencer    | HPC II                |

| 10.0                      | QDR II/QDR II+ | UniPHY RTL Sequencer           | QDR/RLD II controller |

|                           | RLDRAM II      | UniPHY RTL Sequencer           | QDR/RLD II controller |

| F                         | Other          | ALTDQ_DQS <sup>(2)</sup>       | Custom                |

| F                         | Other          | ALTDQ_DQS2 <sup>(3)</sup>      | Custom                |

| Quartus II Version | Memory         | PHY IP                   | Controller IP        |

|--------------------|----------------|--------------------------|----------------------|

| 9.1                | DDR/DDR2/DDR3  | ALTMEMPHY (AFI)          | HPC                  |

|                    | υυη/υυηζ/υυης  |                          | HPC II               |

|                    | QDR II/QDR II+ | UniPHY                   | QDR II controller    |

|                    | RLDRAM II      | UniPHY                   | RLDRAM II controller |

|                    | Other          | ALTDQ_DQS <sup>(2)</sup> | Custom               |

Table 1–2. Altera Memory Types, PHY, and Controllers in the Quartus II Software (Part 2 of 2)

Note to Table 1-2:

(1) AFI = Altera PHY interface

(2) Applicable for Arria II, Stratix III, and Stratix IV devices.

(3) Applicable only for Arria V and Stratix V devices.

For more information about the controllers with the UniPHY or the ALTMEMPHY IP, refer to the *Functional Descriptions* section in Volume 3 of the *External Memory Interface Handbook*.

For more information about the ALTDQ\_DQS megafunction, refer to the *ALTDLL and ALTDQ\_DQS Megafunctions User Guide*.

For more information about the ALTDQ\_DQS2 megafunction, refer to the *ALTDQ\_DQS2 Megafunction User Guide*.

For more information and design example about custom PHY, refer to the Design Example - Stratix III ALTDQ DQS DDR2 SDRAM page.

### **Low Latency**

Altera generally offers low latency solutions that are drastically better than Altera's competitors. Altera's 28-nm FPGA devices have a balanced clocked network in the periphery to reduce switching noise. The hardened read data FIFO buffer guarantees timing and makes it easier for the fitter to place the controller. Together with the latest UniPHY IP, these design changes provide drastic reduction in latency.

Table 1–3 shows latency comparison for Altera and its closest competition.

| Lotonou Tuno  | Latency (Memory           | Adventere |             |

|---------------|---------------------------|-----------|-------------|

| Latency Type  | Competitor <sup>(1)</sup> | Altera    | - Advantage |

| Write Command | 46                        | 29        | Altera      |

| Read Command  | 46                        | 29        | Altera      |

| Read Data     | 31                        | 11        | Altera      |

Table 1–3.

Latency Comparison for Quarter-Rate DDR3 SDRAM Controllers

Note to Table 1-3:

(1) Does not include AXI latency.

# Efficiency

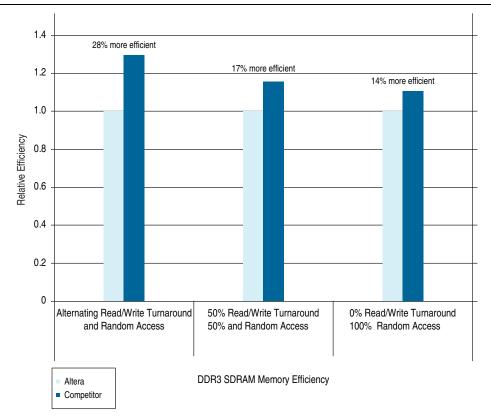

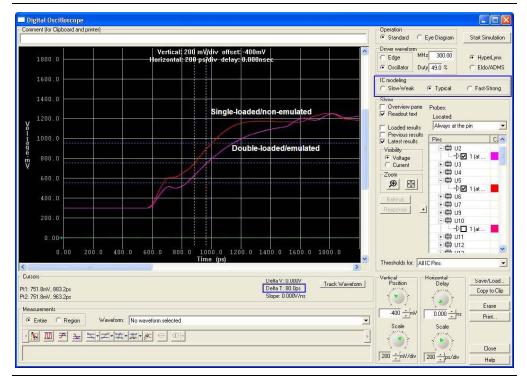

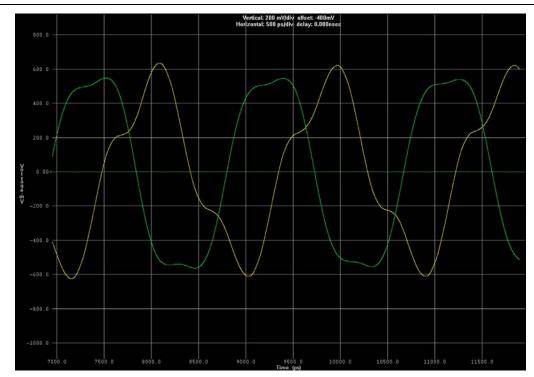

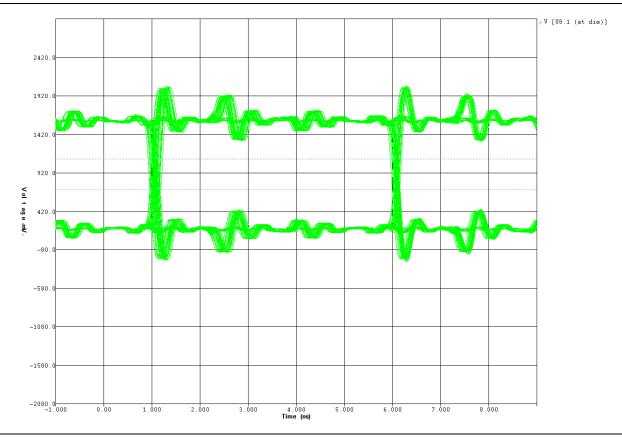

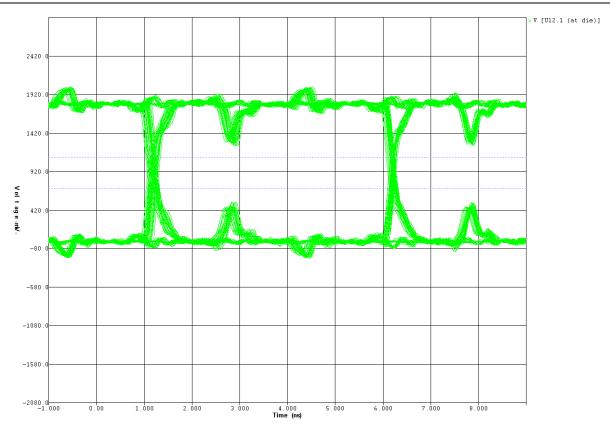

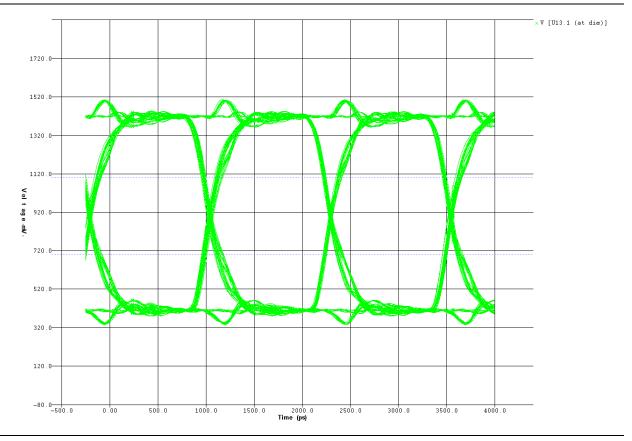

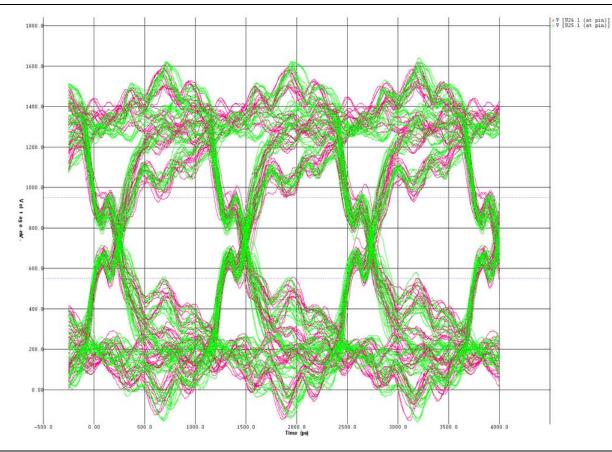

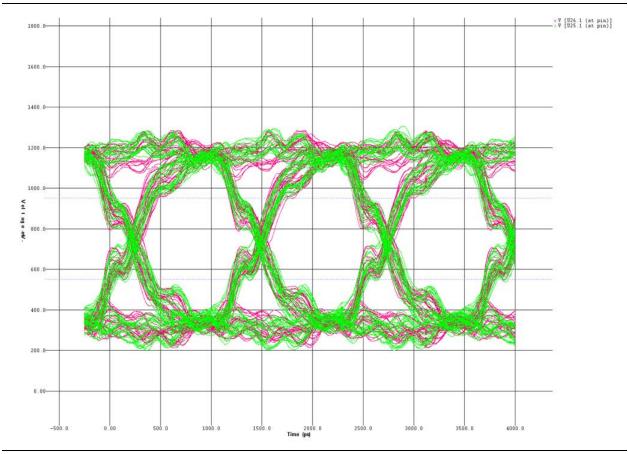

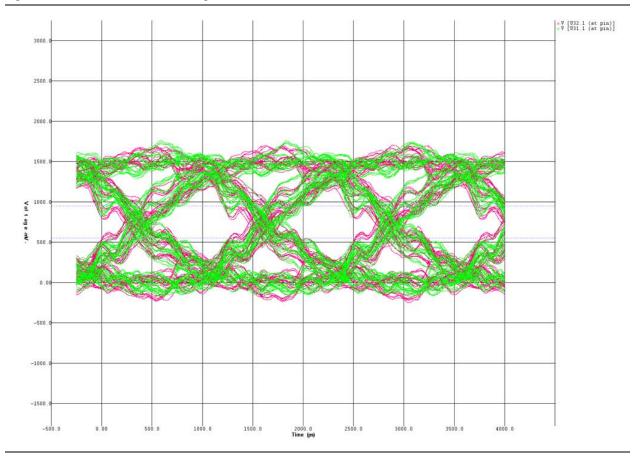

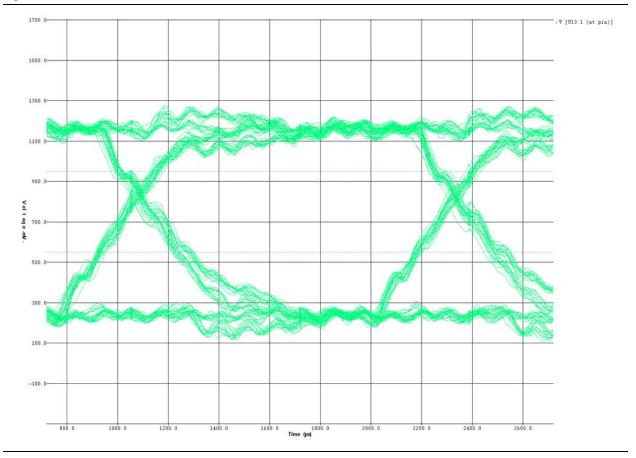

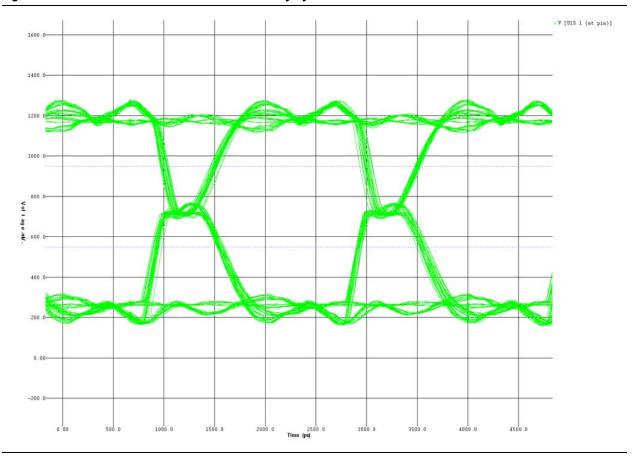

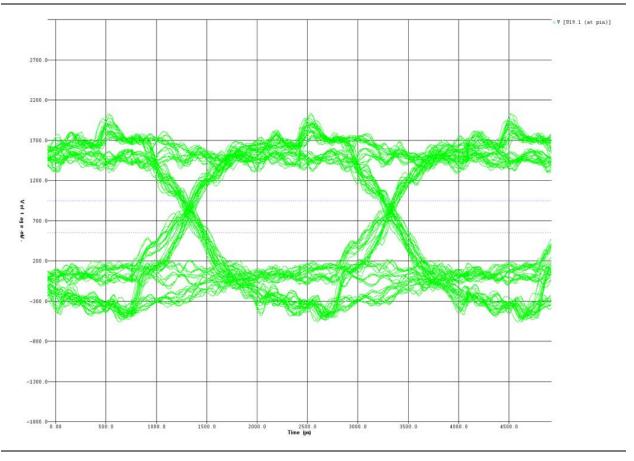

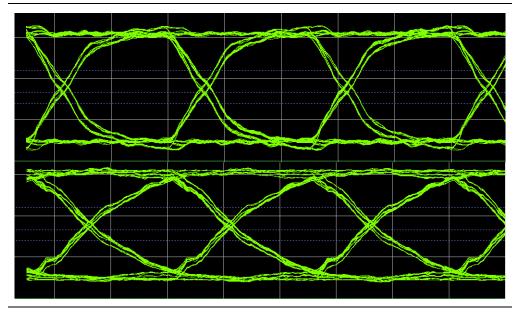

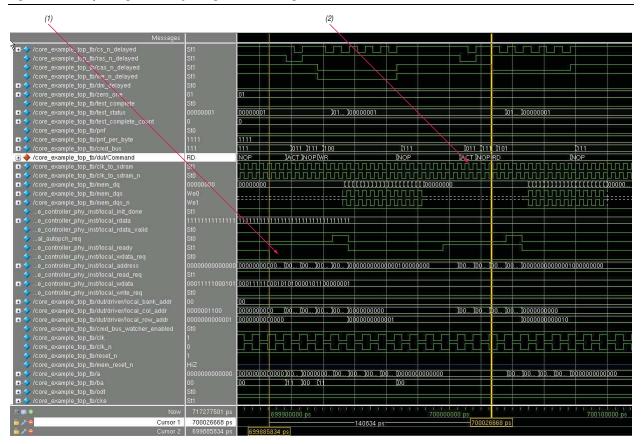

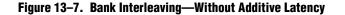

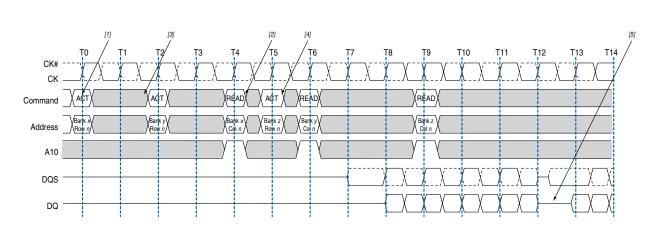

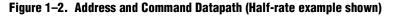

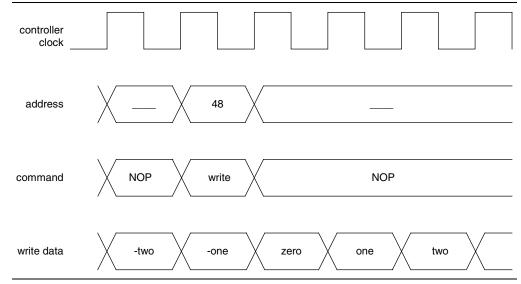

Altera memory controllers are also highly efficient. Figure 1–2 shows the memory efficiency of a DDR3 SDRAM memory controller with UniPHY IP.

Figure 1–2. Memory Efficiency of DDR3 SDRAM Memory Controllers with UniPHY

# **Document Revision History**

Table 1–4 shows the revision history for this document.

#### Table 1–4. Document Revision History

| Date          | Version | Changes          |

|---------------|---------|------------------|

| November 2011 | 1.0     | Initial release. |

# 2. Recommended Design Flow

#### EMI\_GS\_002-2.1

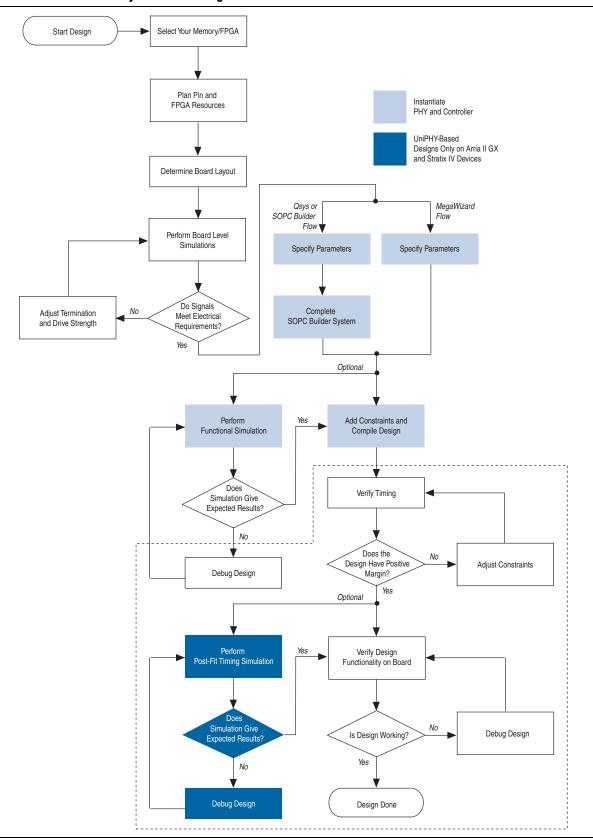

This chapter describes the Altera-recommended design flow for successfully implementing external memory interfaces in Altera<sup>®</sup> devices. Altera recommends that you create an example top-level file with the desired pin outs and all interface IP instantiated, which enables the Quartus<sup>®</sup> II software to validate your design and resource allocation before PCB and schematic sign off. Use the "Design Checklist" on page 2–5, to verify whether you have performed all the recommended steps in creating a working and robust external memory interface.

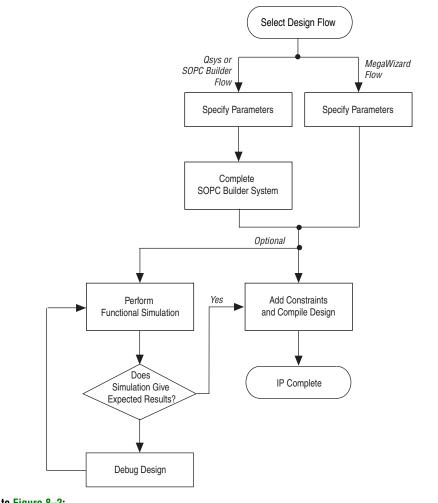

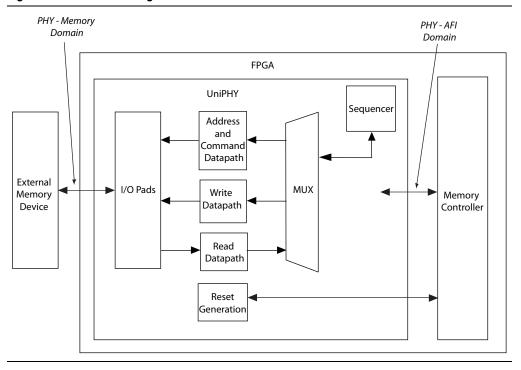

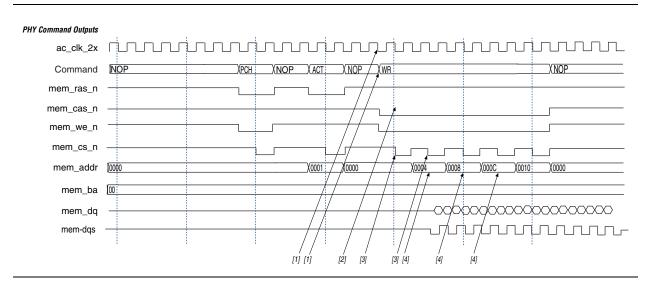

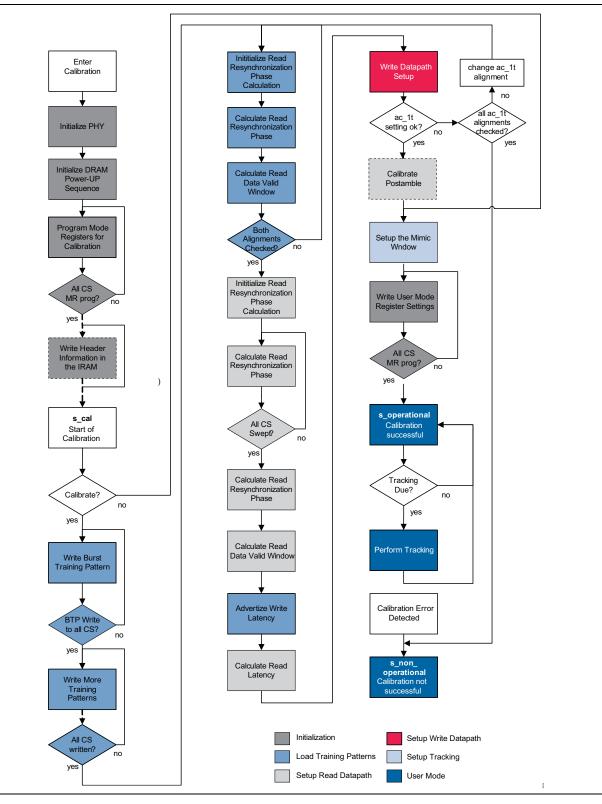

Figure 2–1 shows the design flow to provide the fastest out-of-the-box experience with external memory interfaces in Altera devices. This topic directs you where to find information on how to perform each step of the recommended design flow. The flow assumes that you are using Altera IP to implement the external memory interface.

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Figure 2–1. External Memory Interfaces Design Flowchart

### **Select Your Memory**

When you select an external memory device, you have to consider factors like bandwidth, data storage, latency and power consumption.

For more information about selecting your memory device, refer to the *Selecting Your Memory* chapter in the *External Memory Interface Handbook*.

### **Select Your FPGA**

Different Altera FPGAs support different memory types and configurations. Depending on the requirements of your design, you need to determine the appropriate FPGA.

For more information about selecting your device, refer to the *Selecting Your FPGA* chapter in the *External Memory Interface Handbook*.

### **Planning Pin and FPGA Resources**

Before determining the board layout, you need to determine the usage of FPGA pins, phase-locked loop (PLL), delay-locked loops (DLLs), and other resources.

For more information about planning pins and resources, refer to the *Planning Pin and FPGA Resources* chapter in the *External Memory Interface Handbook*.

### **Determine Board Layout**

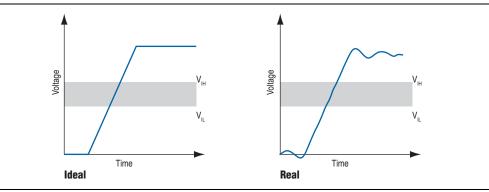

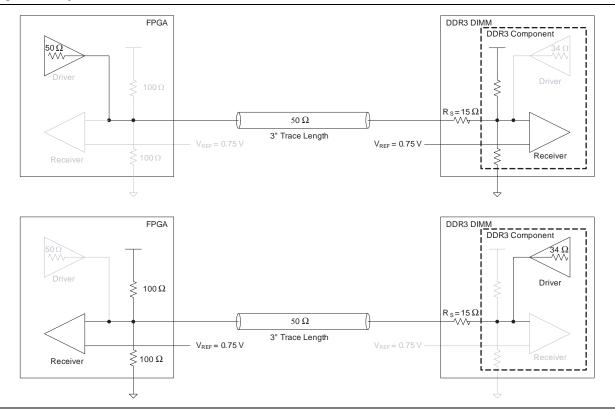

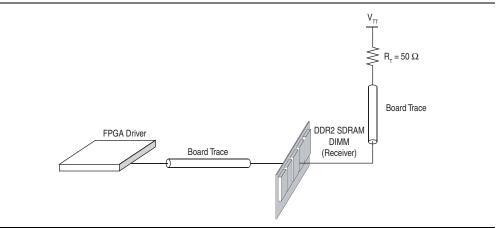

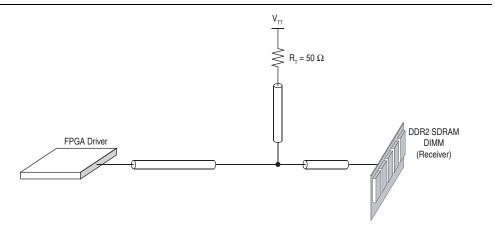

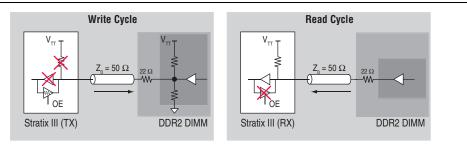

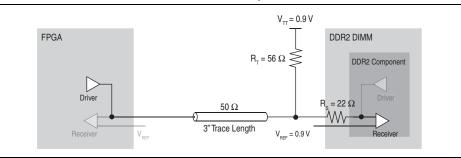

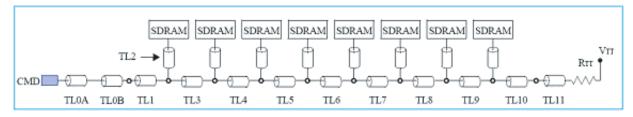

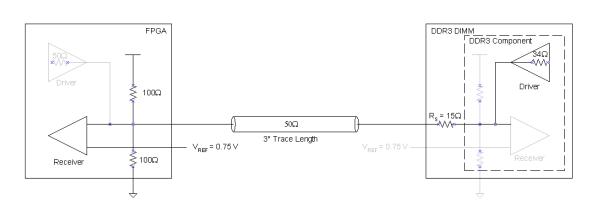

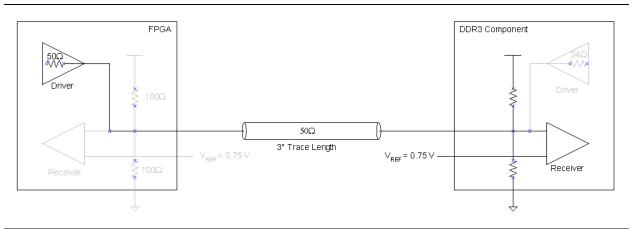

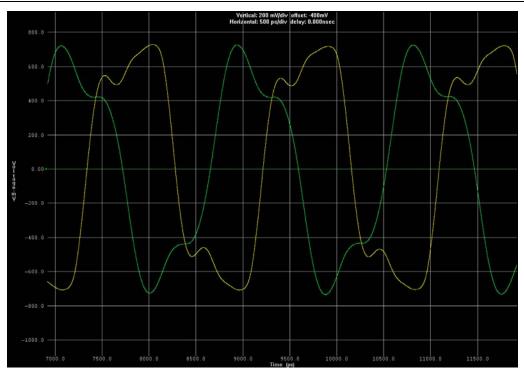

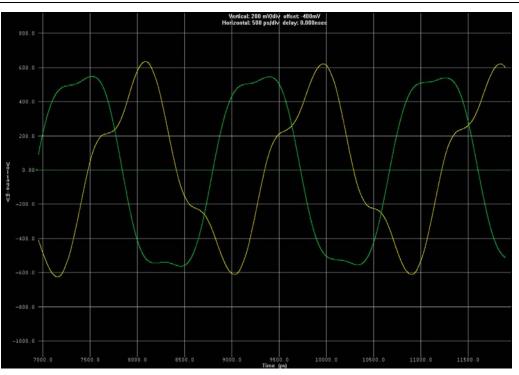

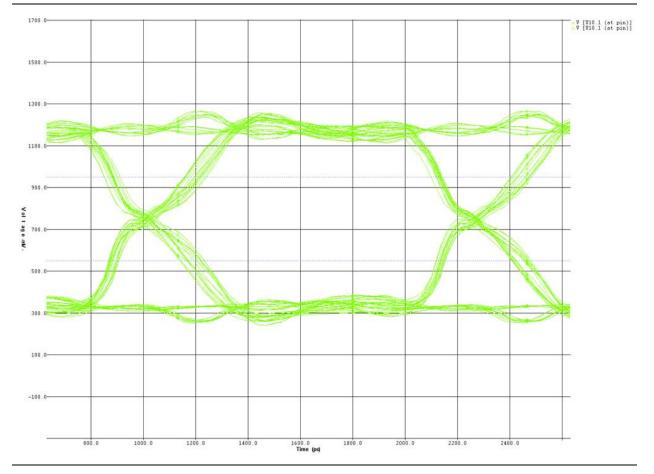

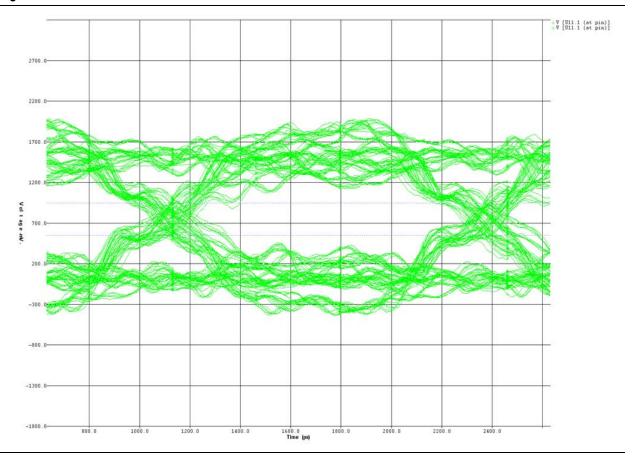

To improve the signal integrity, you have to consider the termination scheme that you use, the drive strength setting on the FPGA, and the loading seen by the driver. You must understand the tradeoffs between the different types of termination schemes and the effects of output drive strengths and loading, to choose the best possible settings for your designs.

For more information about guidelines to determine your board layout for the different memory controllers, refer to the following chapters in the *External Memory Interface Handbook*:

- DDR2 and DDR3 SDRAM Board Design Guidelines

- Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines

- RLDRAM II Board Design Guidelines

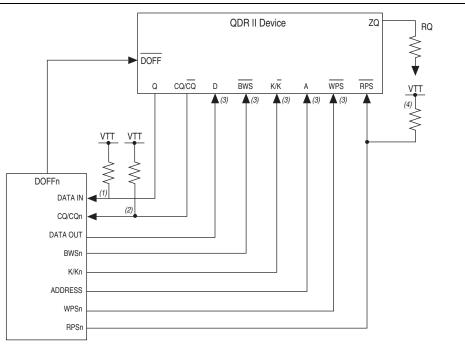

- QDR II SRAM Board Design Guidelines

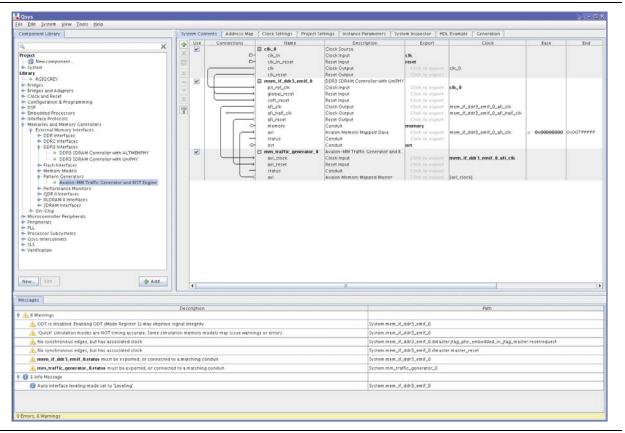

### Implementing and Parameterizing Memory IP

After selecting the appropriate device and memory type, create a project in the Quartus II software that targets the device and memory type.

When implementing and parameterizing external memory interfaces, Altera recommends that you use Altera memory interface IP, which includes a PHY that you can use with the Altera high-performance controller or with your own custom controller.

**For more information about specifying parameters, refer to the** *Implementing and* Parameterizing Memory IP chapter in the External Memory Interface Handbook.

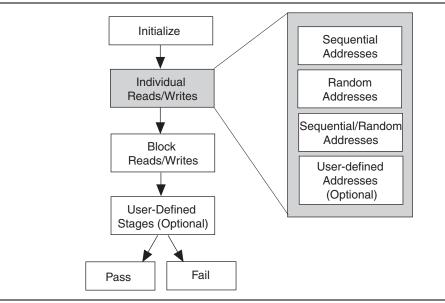

### **Simulating Memory IP**

After implementing and parameterizing the memory IP, you need to perform functional simulation.

For more information about simulation, refer to the Simulating Memory IP chapter in the External Memory Interface Handbook.

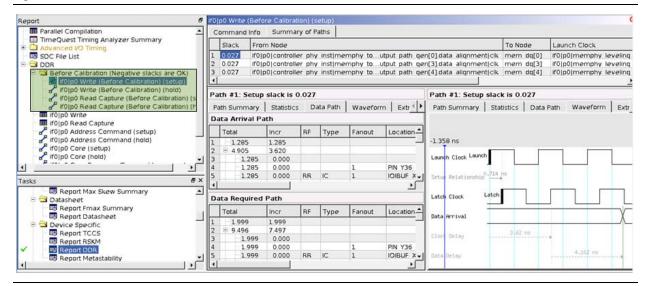

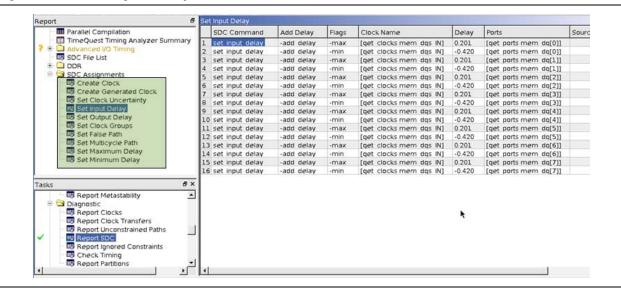

## Analyzing Timing of Memory IP

To ensure your external memory interface meets the various timing requirements, you need to analyze the timing paths, adjust constraints, and verify timing.

For more information about analyzing timing, adjust constraints, and verify timing, refer to the Analyzing Timing of Memory IP chapter in the External Memory Interface Handbook.

## **Perform Post-Fit Timing Simulation**

This step is optional. It ensures that the IP is working properly.

For more information about simulating, refer to the Simulating Memory IP chapter in the External Memory Interface Handbook.

### **Debugging Memory IP**

You need to perform system level verification to correlate the system against your design targets, using the Altera SignalTap<sup>®</sup> II logic analyzer.

For more information about using the SignalTap II analyzer, refer to the *Debugging* Memory IP chapter in the External Memory Interface Handbook.

# **Design Checklist**

This topic contains a design checklist that you can use when implementing external memory interfaces in Altera devices.

|    | Done | Action                                                                                                                                                                                                                                                           | Reference                                                                                                                              |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|    |      | Select Your Memory                                                                                                                                                                                                                                               |                                                                                                                                        |

| 1. |      | Select the memory interface frequency of operation and bus width.                                                                                                                                                                                                | <ul> <li>Selecting Your Memory chapter in the<br/>External Memory Interface Handbook.</li> </ul>                                       |

|    |      | Select Your FPGA                                                                                                                                                                                                                                                 |                                                                                                                                        |

| 2. |      | Select the FPGA device density and package combination that you want to target.                                                                                                                                                                                  | <ul> <li>Selecting Your FPGA chapter in the<br/>External Memory Interface Handbook.</li> </ul>                                         |

|    |      | Plan Pin and FPGA Resources                                                                                                                                                                                                                                      |                                                                                                                                        |

| 3. |      | Ensure that the target FPGA device supports the desired clock rate and memory bus width. Also the FPGA must have sufficient I/O pins for the DQ/DQS read and write groups.                                                                                       | For detailed device resource information,<br>refer to the relevant device handbook<br>chapter on external memory interface<br>support. |

|    |      | Determine Board Layout                                                                                                                                                                                                                                           |                                                                                                                                        |

| 4. |      | Select the termination scheme and drive strength settings for all the memory interface signals on the memory side and the FPGA side.                                                                                                                             | <ul> <li>DDR2 and DDR3 SDRAM Board Design<br/>Guidelines chapter in the External<br/>Memory Interface Handbook.</li> </ul>             |

| 5. |      | Ensure you apply appropriate termination and drive strength settings on all the memory interface signals, and verify using board level simulations.                                                                                                              | <ul> <li>Dual-DIMM DDR2 and DDR3 SDRAM<br/>Board Design Guidelines chapter in the<br/>External Memory Interface Handbook.</li> </ul>   |

| 6. |      | Use board level simulations to pick the optimal setting for best signal integrity. On the memory side, Altera recommends the use of external parallel termination on                                                                                             | <ul> <li>RLDRAM II Board Design Guidelines<br/>chapter in the External Memory<br/>Interface Handbook.</li> </ul>                       |

|    |      | input signals to the memory (write data, address, command, and clock signals).                                                                                                                                                                                   | <ul> <li>QDR II SRAM Board Design Guidelines<br/>chapter in the External Memory</li> </ul>                                             |

| 7. |      | Perform board level simulations, to ensure electrical and timing margins for your memory interface                                                                                                                                                               | Interface Handbook.                                                                                                                    |

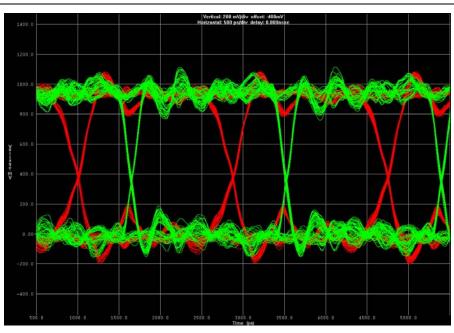

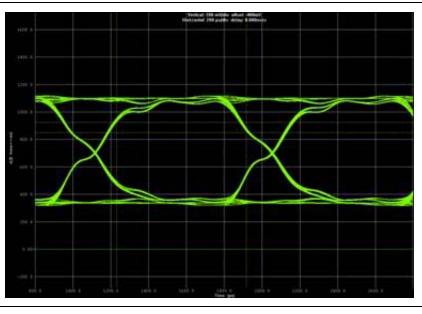

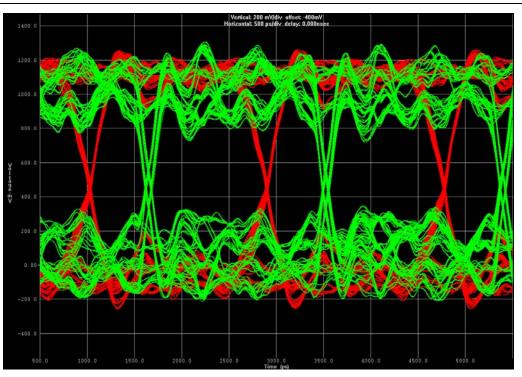

| 8. |      | Ensure you have a sufficient eye opening using simulations.<br>Use the latest FPGA and memory IBIS models, board trace<br>characteristics, drive strength, and termination settings in<br>your simulation.                                                       |                                                                                                                                        |

|    |      | Any timing uncertainties at the board level that you<br>calculate using simulations must be used to adjust the input<br>timing constraints to ensure the accuracy of Quartus II<br>timing margin reports. For example crosstalk, ISI, and slew<br>rate deration. |                                                                                                                                        |

|    | F    | Parameterize and Implement the Memory IP                                                                                                                                                                                                                         |                                                                                                                                        |

| 9. |      | Parameterize and instantiate the Altera external memory IP for your target memory interface.                                                                                                                                                                     | <ul> <li>Implementing and Parameterizing<br/>Memory IP chapter in the External<br/>Memory Interface Handbook</li> </ul>                |

|     | Done | Action                                                                                                                                                                                                                                                                                    | Reference                                                                                                                                                                                               |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10. |      | Ensure that you perform the following actions:                                                                                                                                                                                                                                            |                                                                                                                                                                                                         |

|     |      | <ul> <li>Pick the correct memory interface data rates, width, and configurations.</li> </ul>                                                                                                                                                                                              |                                                                                                                                                                                                         |

|     |      | <ul> <li>For DDR, DDR2, and DDR3 SDRAM interfaces, ensure<br/>that you derate the tIS, tIH, tDS, and tDH parameters, as<br/>necessary.</li> </ul>                                                                                                                                         |                                                                                                                                                                                                         |

|     |      | <ul> <li>Include the board skew parameters for your board.</li> </ul>                                                                                                                                                                                                                     |                                                                                                                                                                                                         |

| 11. |      | Connect the PHY's local signals to your driver logic and the PHY's memory interface signals to top-level pins.                                                                                                                                                                            | <ul> <li>Functional Description: HPC II chapter<br/>in the External Memory Interface</li> </ul>                                                                                                         |

|     |      | Ensure that the local interface signals of the PHY are<br>appropriately connected to your own logic. If the<br>ALTMEMPHY IP is compiled without these local interface<br>connections, you may encounter compilation problems,<br>when the number of signals exceeds the pins available on | <ul> <li>Handbook.</li> <li>Functional Description: QDR II and<br/>QDR II+ SRAM Controller chapter in the<br/>External Memory Interface Handbook.</li> <li>Functional Description: RLDRAM II</li> </ul> |

|     |      | your target device.<br>You may also use the example top-level file as an example                                                                                                                                                                                                          | <i>Controller</i> chapter in the <i>External Memory Interface Handbook</i> .                                                                                                                            |

|     |      | on how to connect your own custom controller to the Altera<br>memory PHY.                                                                                                                                                                                                                 |                                                                                                                                                                                                         |

|     |      | Perform Functional Simulation                                                                                                                                                                                                                                                             |                                                                                                                                                                                                         |

| 12. |      | Simulate your design using the RTL functional model.                                                                                                                                                                                                                                      | Simulating Memory IP chapter in the                                                                                                                                                                     |

|     |      | Use the IP functional simulation model with your own driver logic, testbench, and a memory model, to ensure correct read and write transactions to the memory.                                                                                                                            | External Memory Interface Handbook                                                                                                                                                                      |

|     |      | You may need to prepare the memory functional model by setting the speed grade and device bus mode.                                                                                                                                                                                       |                                                                                                                                                                                                         |

|     |      | Add Constraints                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                         |

| 13. |      | Add timing constraints. The wizard-generated <b>.sdc</b> file adds timing constraints to the interface. However, you may need to adjust these settings to best fit your memory interface configuration.                                                                                   |                                                                                                                                                                                                         |

| 14. |      | Add pin settings and DQ group assignments. The wizard-generated <b>.tcl</b> file includes I/O standard and pin loading constraints to your design.                                                                                                                                        |                                                                                                                                                                                                         |

| 15. |      | Ensure that generic pin names used in the constraint scripts<br>are modified to match your top-level pin names. The<br>loading on memory interface pins is dependent on your<br>board topology (memory components).                                                                       |                                                                                                                                                                                                         |

| 16. |      | Add pin location assignments. However, you need to assign the pin location assignments manually using the Pin Planner.                                                                                                                                                                    |                                                                                                                                                                                                         |

| 17. |      | Ensure that the example top-level file or your top-level logic is set as top-level entity.                                                                                                                                                                                                |                                                                                                                                                                                                         |

|     | Done | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reference                                                                                                   |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

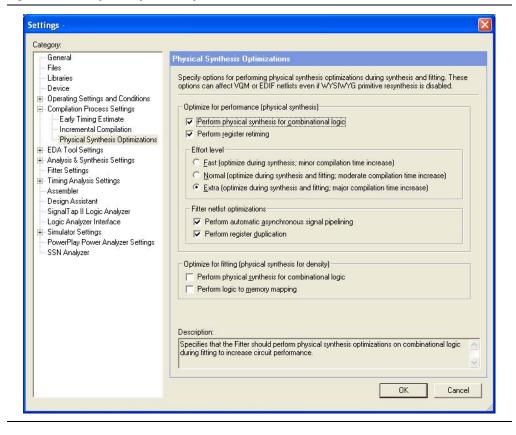

| 18. |      | Adjust optimization techniques, to ensure the remaining<br>unconstrained paths are routed with the highest speed and<br>efficiency:                                                                                                                                                                                                                                                                                                                                         |                                                                                                             |

|     |      | a. On the Assignments menu click Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                             |

|     |      | b. Select Analysis & Synthesis Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                             |

|     |      | c. Select Speed under Optimization Technique.                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                             |

|     |      | d. Expand Fitter Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                             |

|     |      | e. Turn on <b>Optimize Hold Timing</b> and select <b>All Paths</b> .                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                             |

|     |      | f. Turn on <b>Optimize Fast Corner Timing</b> .                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                             |

|     |      | g. Select Standard Fit under Fitter Effort.                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                             |

| 19. |      | Provide board trace delay model. For accurate I/O timing<br>analysis, you specify the board trace and loading<br>information in the Quartus II software. This information<br>should be derived and refined during your board<br>development process of prelayout (line) simulation and<br>finally post-layout (board) simulation. Provide the board<br>trace information for the output and bidirectional pins<br>through the board trace model in the Quartus II software. |                                                                                                             |

|     |      | Compile Design and Verify Timing                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                             |

| 20. |      | Compile your design and verify timing closure using all available models.                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                             |

| 21. |      | Run the wizard-generated<br>< <i>variation_name</i> >_ <b>report_timing.tcl</b> file, to generate a<br>custom timing report for each of your IP instances. Run<br>this process across all device timing models (slow 0°C,<br>slow 85°C, fast 0°C).                                                                                                                                                                                                                          |                                                                                                             |

| 22. |      | If there are timing violations, adjust your constraints to optimize timing                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                             |

| 23. |      | As required, adjust PLL clock phase shift settings or<br>appropriate timing and location assignments margins for<br>the various timing paths within the IP.                                                                                                                                                                                                                                                                                                                 | <ul> <li>Analyzing Timing of Memory IP chapter<br/>in the External Memory Interface<br/>Handbook</li> </ul> |

|     |      | Perform Post-Fit Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                             |

| 24. |      | Perform post-fit timing simulation to ensure that all the memory transactions meet the timing specifications with the vendor's memory model.                                                                                                                                                                                                                                                                                                                                | <ul> <li>Simulating Memory IP chapter in the<br/>External Memory Interface Handbook.</li> </ul>             |

|     |      | Verify Design Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                             |

| 25. |      | Verify the functionality of your memory interface in the system                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Debugging Memory IP chapter in the<br/>External Memory Interface Handbook</li> </ul>               |

# **Document Revision History**

Table 2–1 shows the revision history for this document.

| Date          | Version  | Changes                                                                                       |

|---------------|----------|-----------------------------------------------------------------------------------------------|

| November 2011 | 2.1      | Updated the design flow and the design checklist.                                             |

| July 2010     | 2.0      | Updated for 10.0 release.                                                                     |

| January 2010  | 2010 1.1 | <ul> <li>Improved description for Implementing Altera Memory Interface IP chapter.</li> </ul> |

|               | 1.1      | <ul> <li>Added timing simulation to flow chart and to design checklist.</li> </ul>            |

| November 2009 | 1.0      | First published.                                                                              |

Table 2–1. Document Revision History

# **External Memory Interface Handbook**

# **Volume 2: Design Guidelines**

101 Innovation Drive San Jose, CA 95134 www.altera.com

EMI\_DG-1.0

Document last updated for Altera Complete Design Suite version: 11.1 Document publication date: November 2011

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products as services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

External Memory Interface Handbook Volume 2: Design Guidelines

# **Contents**

| Chapter Revision Dates . |  | xi |

|--------------------------|--|----|

|--------------------------|--|----|

### Section I. Design Flow Guidelines

#### **Chapter 1. Selecting Your Memory**

| Memory Overview                                             |     |

|-------------------------------------------------------------|-----|

| DDR, DDR2, and DDR3 SDRAM                                   | 1–3 |

| DDR SDRAM                                                   |     |

| DDR2 SDRAM                                                  |     |

| DDR3 SDRAM                                                  | 1–3 |

| DDR, DDR2, and DDR3 SDRAM Comparison                        | 1–4 |

| QDR, QDR II, and QDR II+ SRAM                               |     |

| RLDRAM and RLDRAM II                                        | 1–6 |

| Memory Selection                                            |     |

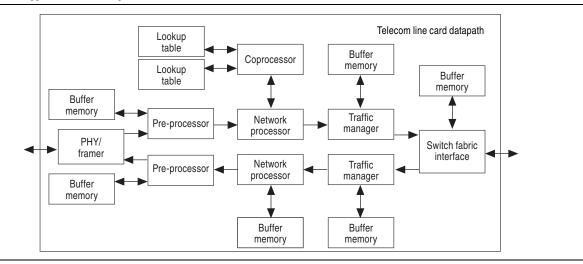

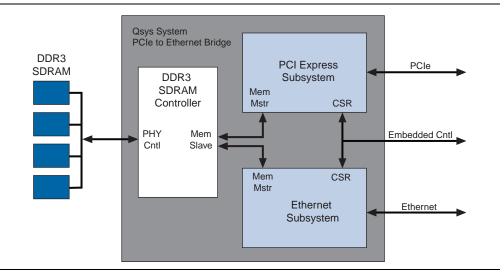

| High-Speed Memory in Embedded Processor Application Example | 1–9 |

| High-Speed Memory in Telecom Application Example            |     |

| Document Revision History                                   |     |

#### **Chapter 2. Selecting Your FPGA Device**

| Device Family Selection           | 2–1 |

|-----------------------------------|-----|

| Cost                              |     |

| Memory Standards                  | 2–2 |

| I/O Interfaces                    | 2–2 |

| Wraparound Interfaces             | 2–3 |

| Read and Write Leveling           | 2–3 |

| Dynamic OCT                       |     |

| Device Settings Selection         | 2–4 |

| Speed Grade                       | 2–4 |

| Ôperating Temperature             | 2–4 |

| Package Šize                      | 2–4 |

| Device Density and I/O Pin Counts |     |

| Device Density                    | 2–5 |

| I/O Pin Counts                    |     |

| Document Revision History         | 2–6 |

#### **Chapter 3. Planning Pin and FPGA Resources**

| Interface Pins                                   | . 3–1 |

|--------------------------------------------------|-------|

| DDR, DDR2, and DDR3 SDRAM                        | . 3–4 |

| Clock Signals                                    | . 3–4 |

| Command and Address Signals                      | . 3–5 |

| Data, Data Strobes, DM, and Optional ECC Signals | . 3–5 |

| DIMM Options                                     | . 3–7 |

| QDR II+ and QDR II SRAM                          | . 3–8 |

| Clock Signals                                    | . 3–8 |

| Command Signals                                  | . 3–9 |

| Address Signals                                  | . 3–9 |

| Data and QVLD Signals                            | 3–10  |

| RLDRAM II                                        |       |

| Clock Signals                                                                                      | . 3–11 |

|----------------------------------------------------------------------------------------------------|--------|

| Commands and Addresses                                                                             |        |

| Data, DM and QVLD Signals                                                                          | . 3–12 |

| Maximum Number of Interfaces                                                                       |        |

| OCT Support for Arria II GX, Arria II GZ, Arria V, Cyclone V, Stratix III, Stratix IV, and Stratix | V      |

| Devices                                                                                            |        |

| General Pin-out Guidelines                                                                         | . 3–24 |

| Pin-out Rule Exceptions                                                                            | . 3–26 |

| Exceptions for ×36 Emulated QDR II and QDR II+ SRAM Interfaces in Arria II, Stratix III and        |        |

| Stratix IV Devices                                                                                 | . 3–26 |

| Timing Impact on x36 Emulation                                                                     |        |

| Rules to Combine Groups                                                                            | . 3–29 |

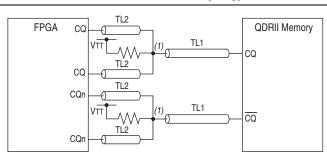

| Determining the CQ/CQn Arrival Time Skew                                                           | . 3–30 |

| Exceptions for RLDRAM II Interfaces                                                                |        |

| Interfacing with ×9 RLDRAM II CIO Devices                                                          | . 3–32 |

| Interfacing with ×18 RLDRAM II CIO Devices                                                         | . 3–32 |

| Interfacing with RLDRAM II ×36 CIO Devices                                                         | . 3–33 |

| Exceptions for QDR II and QDR II+ SRAM Burst-length-of-two Interfaces                              | . 3–33 |

| Pin Connection Guidelines Tables                                                                   | . 3–33 |

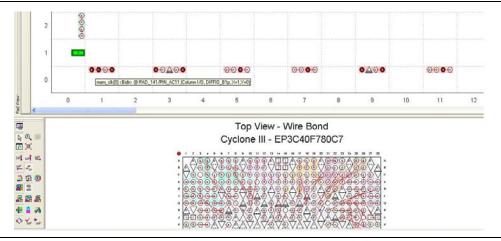

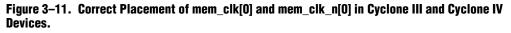

| Additional Placement Rules for Cyclone III and Cyclone IV Devices                                  |        |

| Additional Guidelines for Stratix V Devices                                                        | 3–41   |

| Performing Manual Pin Placement                                                                    |        |

| PLLs and Clock Networks                                                                            | 3–42   |

| Using PLL Guidelines                                                                               | 3–48   |

| PLL Cascading                                                                                      | . 3–49 |

| DLL                                                                                                | . 3–49 |

| Other FPGA Resources                                                                               | 3–51   |

| Document Revision History                                                                          | 3–51   |

#### Chapter 4. DDR2 and DDR3 SDRAM Board Design Guidelines

| Leveling and Dynamic ODT                          |  |

|---------------------------------------------------|--|

| Read and Write Leveling                           |  |

| Dynamic ODT                                       |  |

| Dynamic OCT in Stratix III and Stratix IV Devices |  |

| Dynamic OCT in Stratix V Devices                  |  |

| Board Termination for DDR2 SDRAM                  |  |

| External Parallel Termination                     |  |

| On-Chip Termination                               |  |

| Recommended Termination Schemes                   |  |

| Dynamic On-Chip Termination                       |  |

| FPGA Writing to Memory                            |  |

| FPGA Reading from Memory                          |  |

| On-Chip Termination (Non-Dynamic)                 |  |

| Class II External Parallel Termination            |  |

| FPGA Writing to Memory                            |  |

| FPGA Reading from Memory                          |  |

| Class I External Parallel Termination             |  |

| FPGA Writing to Memory                            |  |

| FPGA Reading from Memory                          |  |

| Class I Termination Using ODT                     |  |

| FPGA Writing to Memory                            |  |

| FPGA Reading from Memory                          |  |

| No-Parallel Termination                           |  |

| FPGA Writing to Memory                            |  |

|                                                   |  |

| FPGA Reading from Memory                                        | 4–35 |

|-----------------------------------------------------------------|------|

| Board Termination for DDR3 SDRAM                                |      |

| Single-Rank DDR3 SDRAM Unbuffered DIMM                          |      |

| DQS, DQ, and DM for DDR3 SDRAM UDIMM                            |      |

| Memory Clocks for DDR3 SDRAM UDIMM                              |      |

| Commands and Addresses for DDR3 SDRAM UDIMM                     |      |

| Stratix III, Stratix IV, and Stratix V FPGAs                    |      |

| DQS, DQ, and DM for Stratix III, Stratix IV, and Stratix V FPGA |      |

| Memory Clocks for Stratix III, Stratix IV, and Stratix V FPGA   |      |

| Commands and Addresses for Stratix III and Stratix IV FPGA      |      |

| Multi-Rank DDR3 SDRAM Unbuffered DIMM                           |      |

| DDR3 SDRAM Registered DIMM                                      |      |

| DDR3 SDRAM Components With Leveling                             |      |

| DDR3 SDRAM Components With or Without Leveling                  |      |

| Stratix III, Stratix IV, and Stratix V FPGAs                    |      |

| Drive Strength                                                  |      |

| How Strong is Strong Enough?                                    |      |

| System Loading                                                  |      |

| Component Versus DIMM                                           |      |

| FPGA Writing to Memory                                          |      |

| FPGA Reading from Memory                                        |      |

| Single- Versus Dual-Rank DIMM                                   |      |

| Single DIMM Versus Multiple DIMMs                               |      |

| Design Layout Guidelines                                        |      |

| Layout Guidelines for DDR2 SDRAM Interface                      |      |

| Layout Guidelines for DDR3 SDRAM Interface                      |      |

| Layout Guidelines for DDR3 SDRAM Wide Interface (>72 bits)      |      |

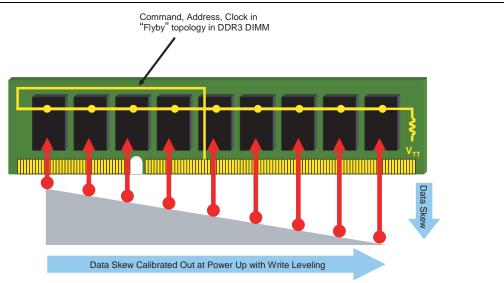

| Fly-By Network Design for Clock, Command, and Address Signals   |      |

| Document Revision History                                       |      |

|                                                                 |      |

### Chapter 5. Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines

| DDR2 SDRAM                                                          |      |

|---------------------------------------------------------------------|------|

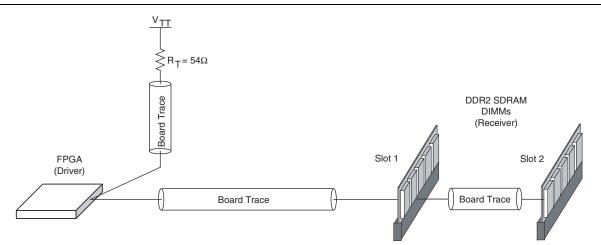

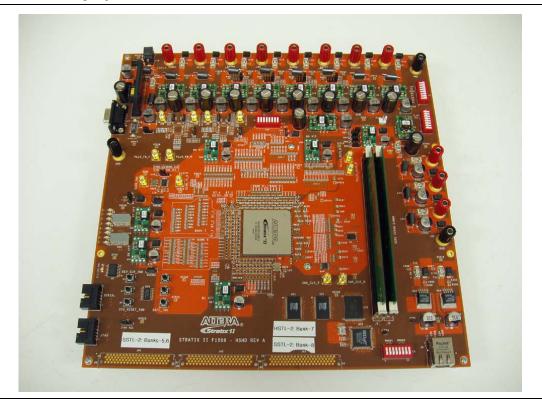

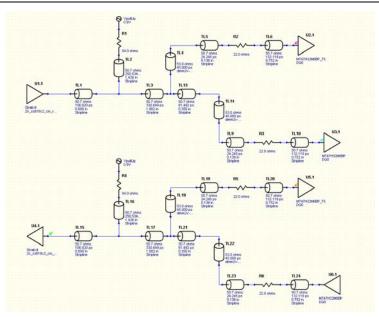

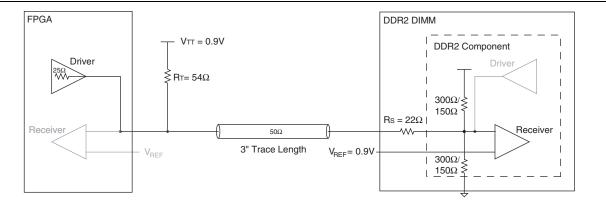

| Stratix II High Speed Board                                         |      |

| Overview of ODT Control                                             |      |

| DIMM Configuration                                                  |      |

| Dual-DIMM Memory Interface with Slot 1 Populated                    |      |

| FPGA Writing to Memory                                              |      |

| Write to Memory Using an ODT Setting of $150\Omega$                 | 5□5  |

| Reading from Memory                                                 |      |

| Dual-DIMM with Slot 2 Populated                                     |      |

| FPGA Writing to Memory                                              |      |

| Write to Memory Using an ODT Setting of $150\Omega$                 | 5□9  |

| Reading from Memory                                                 |      |

| Dual-DIMM Memory Interface with Both Slot 1 and Slot 2 Populated    |      |

| FPGA Writing to Memory                                              |      |

| Write to Memory in Slot 1 Using an ODT Setting of $75-\Omega$       | 5 12 |

| Write to Memory in Slot 2 Using an ODT Setting of 75- $\Omega$      | 5 14 |

| Reading From Memory                                                 |      |

| Dual-DIMM DDR2 Clock, Address, and Command Termination and Topology |      |

| Address and Command Signals                                         |      |

| Control Group Signals                                               |      |

| Clock Group Signals                                                 |      |

| DDR3 SDRAM                                                          |      |

| Comparison of DDR3 and DDR2 DQ and DQS ODT Features and Topology    |      |

| Dual-DIMM DDR3 Clock, Address, and Command Termination and Topology                                   | 5-23 |

|-------------------------------------------------------------------------------------------------------|------|

| Address and Command Signals                                                                           | 5-23 |

| Control Group Signals                                                                                 | 5-23 |

| Clock Group Signals                                                                                   | 5-23 |

| Write to Memory in Slot 1 Using an ODT Setting of 75 $\Omega$ With One Slot Populated                 | 5-24 |

| Write to Memory in Slot 2 Using an ODT Setting of 75 $\Omega$ With One Slot Populated                 | 5-25 |

| Write to Memory in Slot 1 Using an ODT Setting of $150 \Omega$ With Both Slots Populated              | 5–26 |

| Write to Memory in Slot 2 Using an ODT Setting of $150 \Omega$ With Both Slots Populated              | 5–27 |

| Read from Memory in Slot 1 Using an ODT Setting of 150 $\Omega$ on Slot 2 with Both Slots Populated   | 5-28 |

| Read From Memory in Slot 2 Using an ODT Setting of 150 $\Omega$ on Slot 1 With Both Slots Populated . | 5–29 |

| FPGA OCT Features                                                                                     | 5-30 |

| Arria V, Cyclone V, Stratix III, Stratix IV, and Stratix V Devices                                    | 5-30 |

| Arria II GX Devices                                                                                   | 5-30 |

| Document Revision History                                                                             | 5–31 |

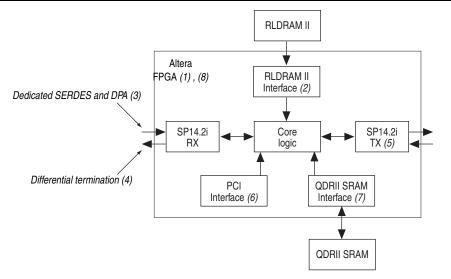

#### Chapter 6. RLDRAM II Board Design Guidelines

| I/O Standards                                    | 6–1  |

|--------------------------------------------------|------|

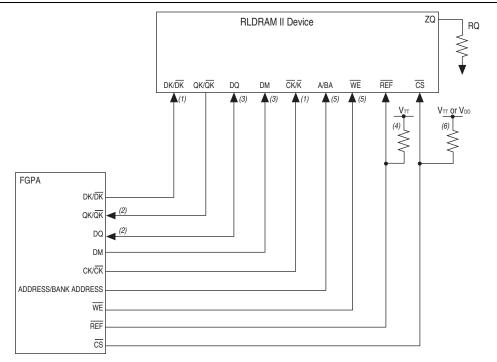

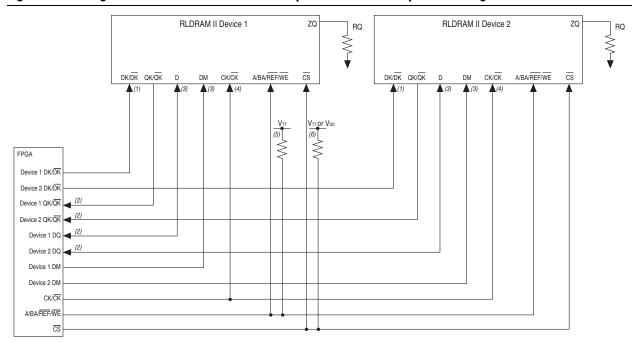

| RLDRAM II Configurations                         |      |

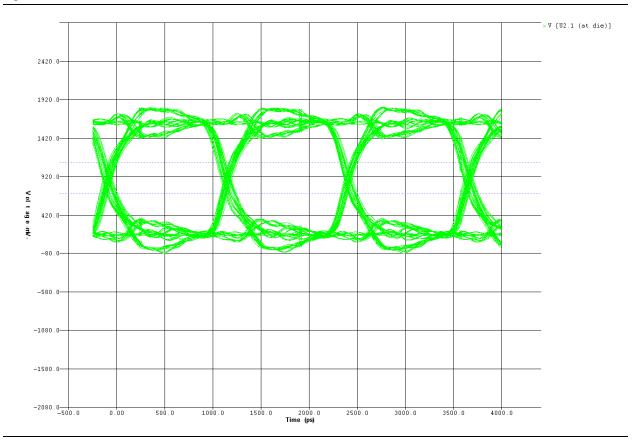

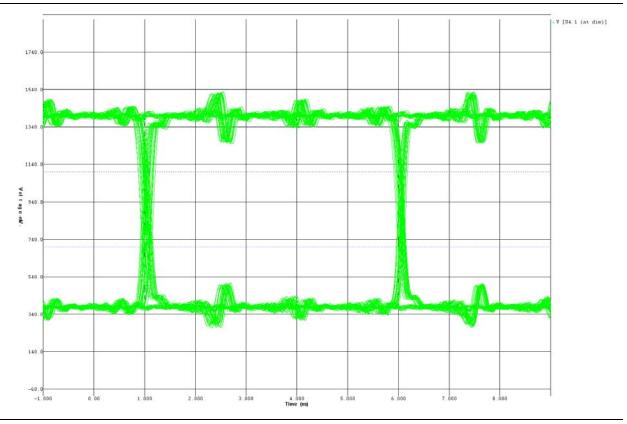

| Signal Terminations                              | 6–3  |

| Outputs from the FPGA to the RLDRAM II Component | 6–5  |

| Input to the FPGA from the RLDRAM II Component   |      |

| Termination Schemes                              | 6–11 |

| PCB Layout Guidelines                            |      |

| Document Revision History                        | 6–14 |

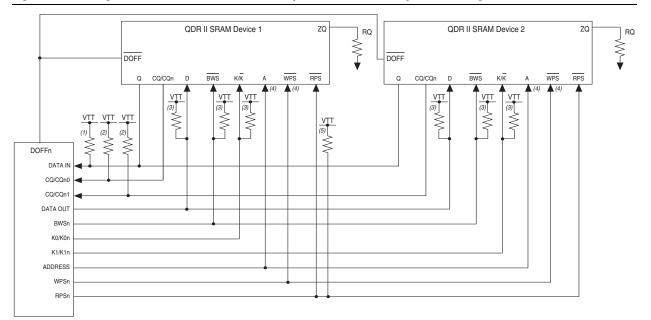

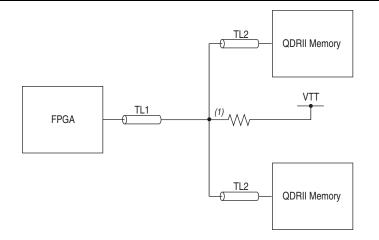

#### Chapter 7. QDR II SRAM Board Design Guidelines

| I/O Standards                                     | 7–1  |

|---------------------------------------------------|------|

| QDR II SRAM Configurations                        |      |

| Signal Terminations                               | 7–4  |

| Output from the FPGA to the QDR II SRAM Component |      |

| Input to the FPGA from the QDR II SRAM Component  |      |

| Termination Schemes                               | 7–17 |

| PCB Layout Guidelines                             |      |

| Document Revision History                         |      |

|                                                   |      |

#### **Chapter 8. Implementing and Parameterizing Memory IP**

| Installation and Licensing               |  |

|------------------------------------------|--|

| Free Evaluation                          |  |

| OpenCore Plus Time-Out Behavior          |  |

| Design Flow                              |  |

| MegaWizard Plug-In Manager Flow          |  |

| Specifying Parameters                    |  |

| Constraining the Design                  |  |

| Add Pins and DQ Group Assignments        |  |

| Compiling the Design                     |  |

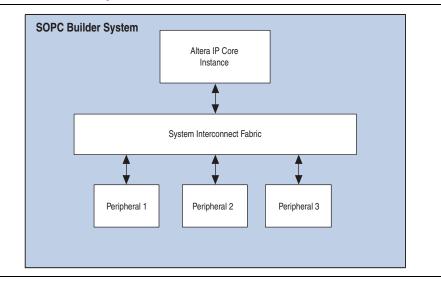

| SOPC Builder Flow                        |  |

| Specifying Parameters                    |  |

| Completing the SOPC Builder System       |  |

| Qsys System Integration Tool Design Flow |  |

| Specify Parameters                       |  |

| Complete the Qsys System                 |  |

| Qsys and SOPC Builder Interfaces         |  |

| Generated Files                          |  |

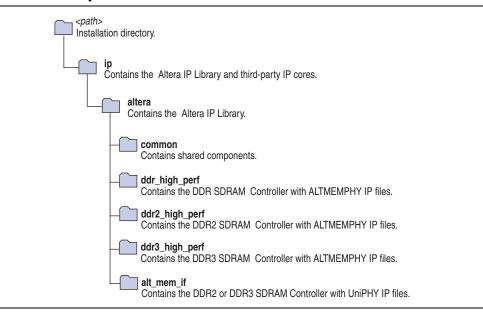

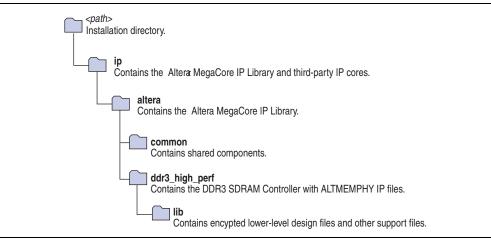

| Generated Files for Memory Controllers with the ALTMEMPHY IP | 8–30 |

|--------------------------------------------------------------|------|

| Generated Files for Memory Controllers with the UniPHY IP    | 8–34 |

| Parameterizing Memory Controllers with ALTMEMPHY IP          | 8–38 |

| Memory Settings                                              |      |

| Show in 'Memory Preset' List                                 | 8–39 |

| Memory Presets                                               | 8–39 |

| Preset Editor Settings for DDR and DDR2 SDRAM                | 8–40 |

| Preset Editor Settings for DDR3 SDRAM                        | 8–45 |

| Derating Memory Setup and Hold Timing                        |      |

| PHY Settings                                                 |      |

| Board Settings                                               | 8–54 |

| Controller Settings                                          |      |

| Parameterizing Memory Controllers with UniPHY IP             | 8–57 |

| PHY Settings                                                 | 8–57 |

| Memory Parameters                                            |      |

| DDR2 and DDR3 SDRAM                                          | 8–61 |

| QDR II and QDR II+ SRAM                                      | 8–63 |

| RLDRAM II                                                    |      |

| Memory Timing                                                | 8–65 |

| Board Settings                                               | 8–66 |

| Setup and Hold Derating                                      |      |

| Intersymbol Inteference                                      |      |

| Board Skews                                                  | 8–70 |

| Controller Settings                                          | 8–76 |

| Diagnostics                                                  |      |

| Document Revision History                                    | 8–80 |

### **Chapter 9. Simulating Memory IP**

| Memory Simulation Models                          | 9–1  |

|---------------------------------------------------|------|

| Simulation Options                                | 9–1  |

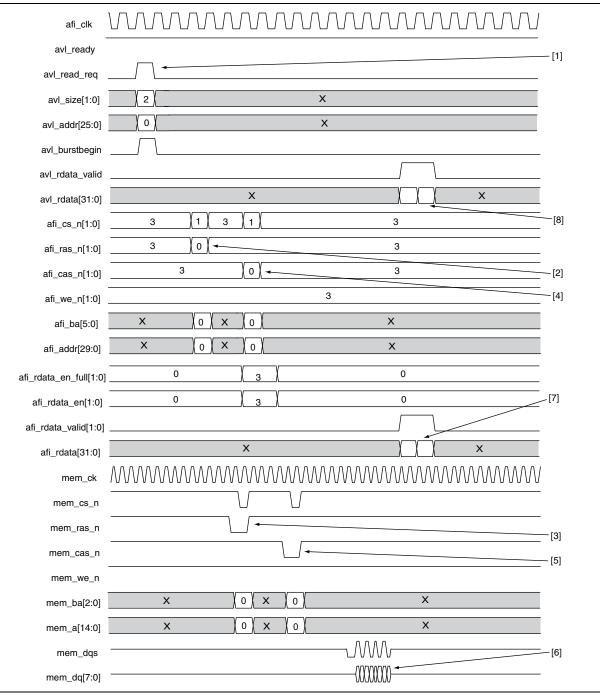

| Simulation Walkthrough with UniPHY IP             | 9–3  |

| Simulation Scripts                                |      |

| Preparing the Vendor Memory Model                 | 9–4  |

| Functional Simulations                            | 9–7  |

| Verilog HDL                                       | 9–7  |

| VHDL                                              | 9–8  |

| Simulating the Example Design                     | 9–9  |

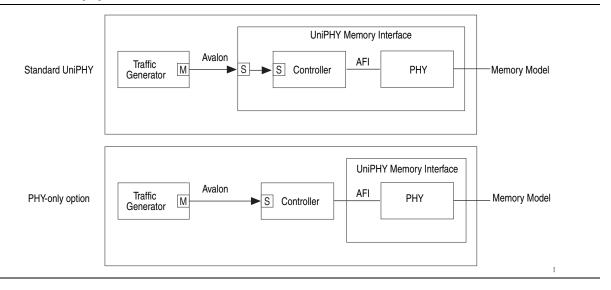

| Abstract PHY                                      | 9–9  |

| PHY-Only Simulation                               | 9–10 |

| Post-fit Functional Simulation                    | 9–11 |

| Simulation Issues                                 | 9–13 |

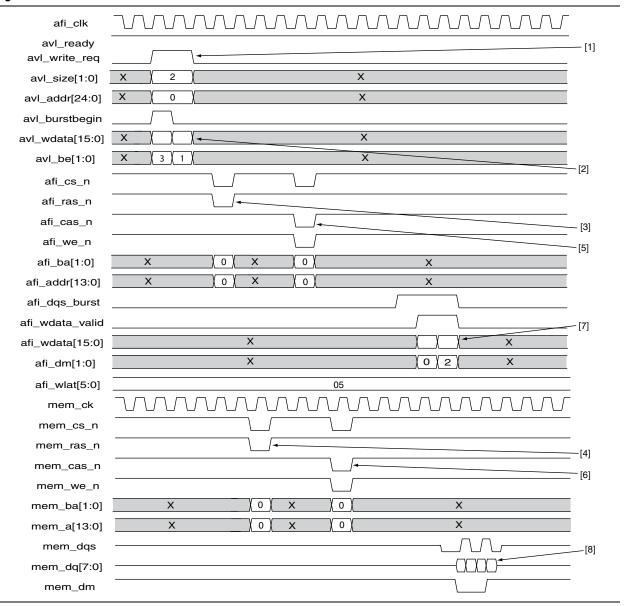

| Simulation Walkthrough with ALTMEMPHY IP          | 9–15 |

| Before Simulating                                 |      |

| Preparing the Vendor Memory Model                 | 9–17 |

| Simulating Using NativeLink                       | 9–19 |

| IP Functional Simulations                         | 9–20 |

| VHDL                                              | 9–20 |

| Verilog HDL                                       | 9–22 |

| Simulation Tips and Issues                        | 9–23 |

| Tips                                              | 9–23 |

| DDR3 SDRAM (without Leveling) Warnings and Errors | 9–24 |

| Document Revision History                         |      |

|                                                   |      |

### Chapter 10. Analyzing Timing of Memory IP

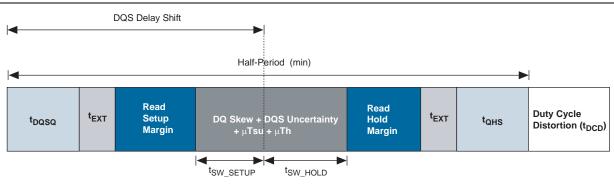

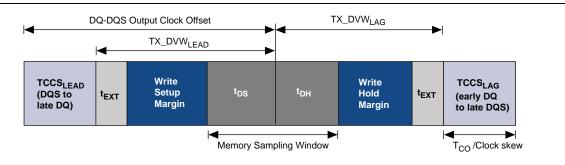

| Memory Interface Timing Components                                                        |       |

|-------------------------------------------------------------------------------------------|-------|

| Source-Synchronous Paths                                                                  |       |

| Calibrated Paths                                                                          |       |

| Internal FPGA Timing Paths                                                                |       |

| Other FPGA Timing Parameters                                                              |       |

| FPGA Timing Paths                                                                         |       |

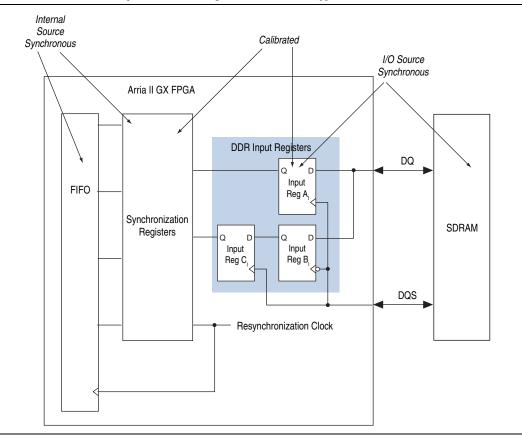

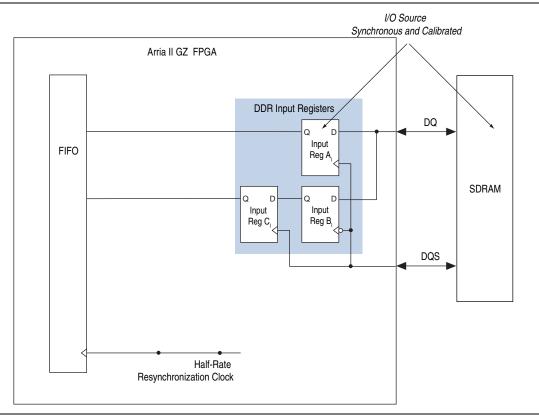

| Arria II Device PHY Timing Paths                                                          |       |

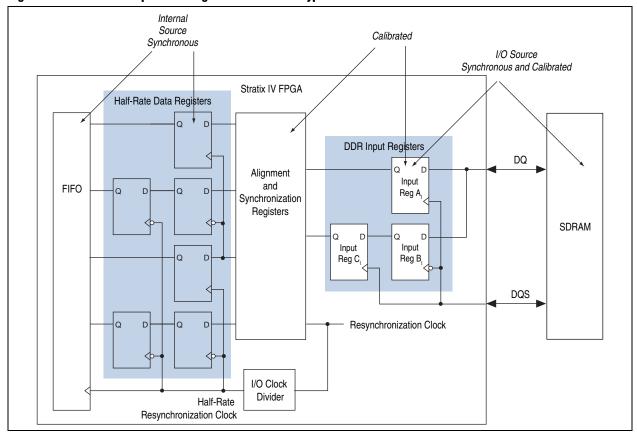

| Stratix III and Stratix IV PHY Timing Paths                                               |       |

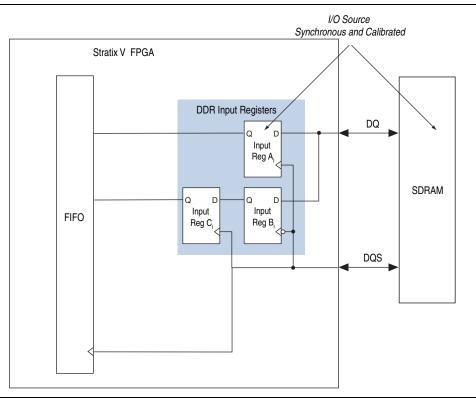

| Arria V, Cyclone V, and Stratix V Timing paths                                            |       |

| Cyclone III and Cyclone IV PHY Timing Paths                                               |       |

| Timing Constraint and Report Files                                                        |       |

| ALTMEMPHY Megafunction                                                                    |       |

| UniPHY IP                                                                                 |       |

| Timing Analysis Description                                                               |       |

| Address and Command                                                                       |       |

| PHY or Core                                                                               |       |

| PHY or Core Reset                                                                         |       |

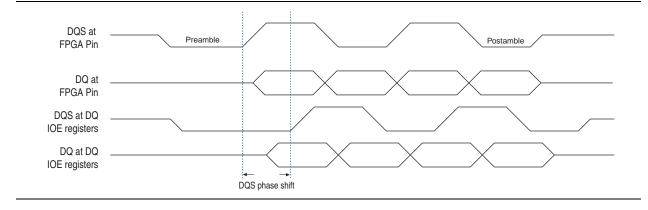

| Read Capture and Write                                                                    |       |

| Cyclone III and Stratix III                                                               |       |

| Arria II, Arria V, Cyclone IV, Cyclone V, Stratix IV and Stratix V                        |       |

| Read Resynchronization                                                                    |       |

| Mimic Path                                                                                |       |

| DQS versus CK—Arria II GX, Cyclone III, and Cyclone IV Devices                            |       |

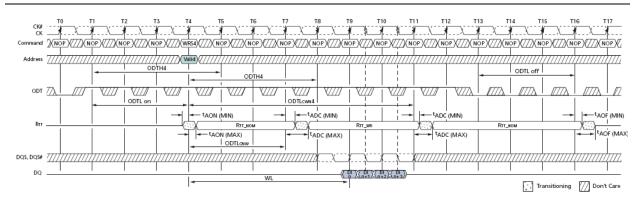

| Write Leveling t <sub>DQSS</sub>                                                          |       |

| Write Leveling toux/tace                                                                  |       |

| Write Leveling t <sub>DSH</sub> /t <sub>DSS</sub><br>DK versus CK (RLDRAM II with UniPHY) |       |

| Bus Turnaround Time                                                                       |       |

| Timing Report DDR                                                                         |       |

| Report SDC                                                                                |       |

| Calibration Effect in Timing Analysis                                                     |       |

| Calibration Emulation for Calibrated Path                                                 |       |

| Calibration Error or Quantization Error                                                   |       |

| Calibration Uncertainties                                                                 |       |

| Memory Calibration                                                                        |       |

| Timing Model Assumptions and Design Rules                                                 |       |

| Memory Clock Output Assumptions                                                           |       |

| Cyclone III Devices                                                                       |       |

| Stratix III Devices                                                                       |       |