# PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in-

formation and before placing orders for products or services.

#### **Contents**

| About this User Guide                                                | v    |

|----------------------------------------------------------------------|------|

| Revision History                                                     | V    |

| How to Contact Altera                                                | V    |

| Typographic Conventions                                              | v    |

| Chapter 1. About the Cyclone II PowerPlay Early Power Estimator      |      |

| Release Information                                                  | 1–1  |

| Device Family Support                                                | 1–1  |

| General Description                                                  | 1–1  |

| Features                                                             | 1–2  |

| Chapter 2. Setting Up the Cyclone II PowerPlay Early Power Estimator |      |

| System Requirements                                                  | 2–1  |

| Download & Install the PowerPlay Early Power Estimator Spreadsheet   | 2–1  |

| Estimating Power                                                     |      |

| Estimating Power Before Starting the FPGA Design                     |      |

| Estimating Power While Creating the FPGA Design                      |      |

| Estimating Power After Completing the FPGA Design                    |      |

| Entering Information into the PowerPlay Early Power Estimator        |      |

| Clearing All Values                                                  |      |

| Manually Entering Information                                        | 2–5  |

| Importing a File                                                     | 2–5  |

| Importing Information from Early Power Estimator Version 5.1         | 2–6  |

| Chapter 3. Using the Cyclone II PowerPlay Early Power Estimator      |      |

| Introduction                                                         | 3–1  |

| PowerPlay Early Power Estimator Spreadsheet Inputs                   |      |

| Main Input Parameters                                                | 3–1  |

| Logic                                                                |      |

| RAM Blocks                                                           |      |

| Multiplier Blocks                                                    |      |

| General I/O Pins                                                     |      |

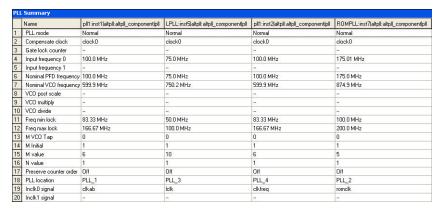

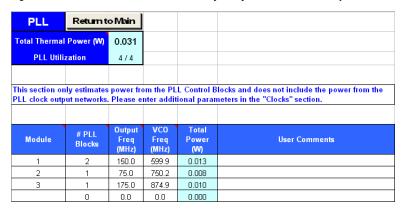

| Phase-Locked Loops                                                   | 3–20 |

| Clocks                                                               |      |

| Power Analysis                                                       | 3–23 |

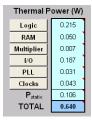

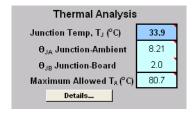

| Thermal Power                                                        |      |

| Thermal Analysis                                                     |      |

| Not Using a Heat Sink                                                |      |

| Using a Heat Sink                                                    |      |

| Power Supply Sizing (A)                                              | 3–30 |

Altera Corporation

#### **About this User Guide**

#### **Revision History**

The table below displays the revision history for the chapters in this User Guide.

| Date          | Version | Changes Made                                                            |

|---------------|---------|-------------------------------------------------------------------------|

| May 2006      | 1.1     | Updated cross references to match Quartus II 6.0 chapter title changes. |

| December 2005 | 1.0     | First publication.                                                      |

#### How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide website at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

### Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                | Meaning                                                                                                                                                                                                                                         |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                      |

| bold type                                 | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file. |

Altera Corporation

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                                                                         |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type.  Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                    |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and a., b., c., etc.            | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| •••                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                                     | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |

| A                                           | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

## Chapter 1. About the Cyclone II PowerPlay Early Power Estimator

#### Release Information

Table 1–1 provides information on the version of the PowerPlay Early Power Estimator spreadsheet documented in this User Guide.

| Table 1–1. PowerPlay Early Power Estimator Spreadsheet Versions    |               |

|--------------------------------------------------------------------|---------------|

| Device Family  PowerPlay Early Power Estimator Spreadsheet Version |               |

| Cyclone II                                                         | 6.0 and later |

## Device Family Support

The Cyclone II<sup>™</sup> PowerPlay Early Power Estimator spreadsheet provides full support for the target Altera device families listed in Table 1–2.

| Table 1–2. Device Family Support |         |

|----------------------------------|---------|

| Device Family                    | Support |

| Cyclone II                       | Full    |

## General Description

As designs grow larger and processes continue to shrink, power becomes an increasing concern. Printed circuit board (PCB) designers need an accurate estimate of the amount of power the device will consume to develop an appropriate power budget, design the power supplies, voltage regulators, heat sink and cooling system. You can calculate a Cyclone II device's power using the Microsoft Excel-based PowerPlay Early Power Estimator spreadsheet available from the Altera website or the PowerPlay power analyzer in the Quartus® II software. You need to enter the device resources, operating frequency, toggle rates, and other parameters in the PowerPlay Early Power Estimator spreadsheet.

This user guide explains how to use the Cyclone II PowerPlay Early Power Estimator spreadsheet to estimate device power consumption.

These calculations should only be used as an estimation of power, not as a specification. Be sure to verify the actual power during device operation, as the information is sensitive to the actual device design and the environmental operating conditions.

For more information about available device resources, I/O standard support, and other device features, refer to the appropriate device family handbook.

#### **Features**

The features of the PowerPlay Early Power Estimator spreadsheet include:

- Estimate your design's power usage before creating the design, during the design process, or after the design is complete

- Import device resource information from the Quartus II software into the PowerPlay Early Power Estimator spreadsheet with the use of the Quartus II-generated power estimation file

- Perform preliminary thermal analysis of your design

## Chapter 2. Setting Up the Cyclone II PowerPlay Early Power Estimator

#### System Requirements

The PowerPlay Early Power Estimator spreadsheet requires:

- A PC running the Windows NT/2000/XP operating system

- Microsoft Excel 2002 or higher

- Quartus II software version 6.0 or higher if generating a file for import

# Download & Install the PowerPlay Early Power Estimator Spreadsheet

The Cyclone II PowerPlay Early Power Estimator spreadsheet is available from the Altera website (**www.altera.com**). After reading the terms and conditions and clicking **I Agree**, you can download the Microsoft Excel file to your hard drive.

By default, the Microsoft Excel 2002 macro security level is set to High. When the macro security level is set to High, macros are automatically disabled. To change the macro security level in Microsoft Excel 2002, click Options on the Tools menu. On the Security tab of the Options window, click Macro Security. On the Security Level tab of the Security dialog box, chose Medium. When the macro security level is set to Medium, a pop-up window asks you whether to enable macros or disable macros each time you open a spreadsheet that contains macros. After changing the macro security level, you will have to close the spreadsheet and re-open it in order to use the macros.

### Estimating Power

You can estimate power at any point in your design cycle. You can use the PowerPlay Early Power Estimator spreadsheet to estimate the power consumption if you have not begun your design, or if your design is not complete. After completing your design, you can use the PowerPlay power analyzer in the Quartus II software or the PowerPlay Early Power Estimator spreadsheet to estimate the power consumption.

For more information on the power estimation feature in the Quartus II software, refer to the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

To use the PowerPlay Early Power Estimator spreadsheet, enter the device resources, operating frequency, toggle rates and other parameters in the PowerPlay Early Power Estimator spreadsheet. If you do not have

an existing design, then you need to estimate the number of device resources your design will use in order to enter the information into the PowerPlay Early Power Estimator spreadsheet.

#### Estimating Power Before Starting the FPGA Design

FPGAs provide the convenience of a shorter design cycle and faster time-to-market than ASICs or ASSPs. This means that the board design often takes places during the FPGA design cycle, and the power planning for the device can happen before any of the FPGA design is complete.

Table 2–1 shows the advantages and disadvantages of using the PowerPlay Early Power Estimator spreadsheet before you begin the FPGA design.

| Table 2–1. Power Estimation Before Designing FPGA               |                                                                                                       |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| Advantages                                                      | Disadvantages                                                                                         |  |

| Power estimation can be done before any FPGA design is complete | Accuracy depends on user input and estimate of the device resources     Process can be time consuming |  |

To estimate power usage with the PowerPlay Early Power Estimator spreadsheet if you have not started your FPGA design, perform the following steps.

- Download the PowerPlay Early Power Estimator spreadsheet from the Altera website (www.altera.com).

- Select the target device and package from the PowerPlay Early Power Estimator spreadsheet's **Device** section.

- 3. Enter values in the fields on each section of the PowerPlay Early Power Estimator spreadsheet. Different worksheets in the file display different power sections, such as clocks and PLLs. Power is calculated automatically, and subtotals are given for each section.

- The calculator displays the estimated power usage in the **Total** section.

#### Estimating Power While Creating the FPGA Design

When the FPGA design is partially complete, you can use the power estimation file (<*revision name*>\_**early\_pwr.csv**) generated by the Quartus II software to supply information to the PowerPlay Early Power Estimator spreadsheet. After importing the power estimation file

information into the PowerPlay Early Power Estimator spreadsheet, you can edit the PowerPlay Early Power Estimator spreadsheet to reflect the device resource estimates for the final design.

For more information on generating the power estimation file in the Quartus II software, refer to the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

Table 2–2 shows the advantages and disadvantages when using the PowerPlay Early Power Estimator spreadsheet for an FPGA design that is partially complete.

| Table 2–2. Power Estimation When FPGA Design Is Partially Complete                                                                                                                                                                          |                                                                                       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

| Advantages                                                                                                                                                                                                                                  | Disadvantages                                                                         |  |

| <ul> <li>Power estimation can be done early in the FPGA design cycle</li> <li>Provides the flexibility to automatically fill in the PowerPlay Early Power Estimator spreadsheet based on Quartus II software compilation results</li> </ul> | Accuracy is dependent on user input and estimate of the final design device resources |  |

Use the following steps to estimate power usage with the PowerPlay Early Power Estimator spreadsheet if your FPGA design is partially complete.

- 1. Compile the partial FPGA design in the Quartus II software.

- Generate the PowerPlay Early Power Estimator file (<revision name>\_early\_pwr.csv) in the Quartus II software by clicking Generate PowerPlay Early Power Estimator File on the Project menu.

- 3. Download the PowerPlay Early Power Estimator spreadsheet from the Altera website.

- 4. Import the PowerPlay Early Power Estimator file into the PowerPlay Early Power Estimator spreadsheet to automatically populate the entries.

- After importing the file to populate the PowerPlay Early Power Estimator spreadsheet, you can manually edit the cells to reflect final device resource estimates.

#### **Estimating Power After Completing the FPGA Design**

When you complete your FPGA design in the Quartus II software, the PowerPlay Power Analyzer provides the most accurate estimate of device power consumption. The PowerPlay power analyzer uses user mode and default assignments in addition to place-and-route information to determine power consumption. The Quartus II PowerPlay power analyzer supports power estimation for Cyclone II devices.

Table 2–3 shows the advantages and disadvantages when using the PowerPlay Early Power Estimator spreadsheet when the FPGA design is complete.

| Table 2–3. Power Estimation When FPGA Design Is Complete             |                                                                                                                                                                                               |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Advantages                                                           | Disadvantages                                                                                                                                                                                 |  |

| Provides more accurate power estimation since the design is complete | <ul> <li>Power estimation done later in the<br/>FPGA design cycle</li> <li>Results will not be as accurate as<br/>those obtained using the Quartus II<br/>PowerPlay power analyzer</li> </ul> |  |

For more information about how to use the PowerPlay Power Analyzer in the Quartus II software, refer to the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

# Entering Information into the PowerPlay Early Power Estimator

You can either manually enter power information into the PowerPlay early power estimator or load a power estimation file generated by the Quartus II software version 5.1. You can also clear all the values currently in the PowerPlay early power estimator.

#### **Clearing All Values**

All user entered values can be reset in the PowerPlay early power estimator by clicking **Reset**.

In order to use the Reset EPE feature, you must enable macros for the spreadsheet. If you have not enabled macros for the spreadsheet you will need to reset all user-entered values manually.

#### **Manually Entering Information**

You can manually enter values into the PowerPlay early power estimator in the appropriate section. White, unshaded cells are input cells and may be modified. Each section contains a column that allows you to specify a module name based on your design.

#### Importing a File

If you already have an existing design or a partially completed design, the power estimation report file generated by the Quartus II software contains the device resource information. You can import this device resource information from the Quartus II software power estimation file into the PowerPlay early power estimator. Importing a file saves you time and effort otherwise spent manually entering information into the PowerPlay early power estimator. You can also manually change any of the values after importing a file.

To generate the power estimation file, you must first compile your design in the Quartus II software. After compiling the design, click **Generate PowerPlay Early Power Estimator File** (Project menu). The Quartus II software creates a power estimation file with the name *<revision name>\_early\_pwr.csv.*

For more information on generating the power estimation file in the Quartus II software, refer to the *PowerPlay Power Analysis* chapter in the *Quartus II Handbook*.

To import data into the PowerPlay early power estimator, perform the following steps:

- Click Import Quartus II File in the PowerPlay early power estimator.

- Browse to a power estimation file generated from the Quartus II software and click Open. The file has a name <revision name>\_early\_pwr.csv.

- 3. Click **OK** in the confirmation window to proceed.

- When the file is imported, click OK. Clicking OK acknowledges the import is complete. If there are any errors during the import, an .err file is generated with details.

After importing a file, you must verify all your information.

Importing a file from the Quartus II software populates all input parameters on the main page that were specified in the Quartus II software. These parameters include:

- Device

- Package

- Temperature grade

- Power characteristics

- Ambient temperature

- Airflow

- Heat sink

- Custom θ<sub>SA</sub>

- Board thermal model

- Custom θ<sub>IB</sub>

- Board temp T<sub>B</sub>

The airflow, heat sink, custom  $\theta_{SA}$ , board thermal model, custom  $\theta_{JB}$ , and board temperature  $T_B$  parameters are optional. Refer to "Main Input Parameters" on page 3–1 for more information on these parameters.

The  $f_{MAX}$  values imported into the PowerPlay early power estimator are the same as the  $f_{MAX}$  values specified by the designer in the Quartus II software. You can manually edit the  $f_{MAX}$  and the toggle percentage in the PowerPlay early power estimator to suit your system requirements.

#### Importing Information from Early Power Estimator Version 5.1

If you already have an existing version 5.1 PowerPlay Early Power Estimator file, you can import the data directly into version 6.0 of the PowerPlay early power estimator using the Import EPE v.51 feature. This can save time and effort otherwise spent manually entering information into the PowerPlay early power estimator.

To import data from version 2.1 of the PowerPlay early power estimator, perform the following steps.

- 1. Click **Import EPE v5.1**.

- 2. Browse to the EPE and click **Open**.

- 3. Click **OK**.

Clicking OK, acknowledges that the import is complete.

Clicking OK clears any user-entered values and populates the PowerPlay early power estimator with device resource information from the specified PowerPlay early power estimator version 5.1 file.

After importing legacy Early Power Estimator spreadsheets, you must manually ensure that all the information is correct.

#### Chapter 3. Using the Cyclone II PowerPlay Early Power Estimator

#### Introduction

The PowerPlay Early Power Estimator spreadsheet provides the ability to enter information into sections based on architectural features. The PowerPlay Early Power Estimator spreadsheet also provides a subtotal of power consumed by each architectural feature and is reported in each section in Watts (W).

#### PowerPlay Early Power Estimator Spreadsheet Inputs

The following sections of the user guide explain what values you need to enter for each section of the PowerPlay Early Power Estimator spreadsheet. The different Excel worksheets of the PowerPlay Early Power Estimator spreadsheet are referred to as sections. Sections in the PowerPlay Early Power Estimator spreadsheet calculate power representing architectural features of the device, such as clocks, RAM blocks, or embedded multiplier blocks.

#### **Main Input Parameters**

Different Cyclone II devices consume different amounts of power for the same design. The larger the device, the more power it will consume because of the larger die and longer interconnects in the device.

In the **Main** section, you must enter the following parameters for the device and design:

- Device

- Package

- Temperature grade

- Power characteristics

- Ambient temperature

- Airflow

- Heat sink used

- Custom heat sink information

- Board thermal model

- Custom board thermal model information

- Board temperature

Table 3–1 describes the values that need to be specified in the **Main** section of the PowerPlay Early Power Estimator spreadsheet.

| Input Parameter                   | Description                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                            | Select the appropriate Cyclone II device.                                                                                                                                                                                                                                                                                                                          |

| Package                           | Select the appropriate package. The package options are dependant on the device selected.                                                                                                                                                                                                                                                                          |

| Temperature Grade                 | Select whether a commercial or industrial device is being used.                                                                                                                                                                                                                                                                                                    |

| Power Characteristics             | Select whether you would like to estimate typical or maximum power for the design                                                                                                                                                                                                                                                                                  |

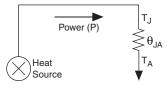

| Ambient Temp, T <sub>A</sub> (°C) | Enter the ambient temperature the device will be operating at. This value can range from -40 °C to 100 °C.                                                                                                                                                                                                                                                         |

| Airflow                           | Select an ambient airflow from the options of still air, 100 linear feet per minute (lfm, 0.5 m/s), 200 lfm (1 m/s), or 400 lfm (2 m/s).                                                                                                                                                                                                                           |

| Heat sink                         | Select the heat sink being used. You can specify no heat sink, a heat sink with set parameters or specify a custom solution. The heat sink selection will update the $\theta_{SA}$ Heatsink-Ambient parameter under Thermal Analysis. If a custom solution is selected the value will be what is entered for Custom $\theta_{SA}$ (°C/W).                          |

| Custom θ <sub>SA</sub> (°C/W)     | Enter a value for a custom heat sink setting. This value is only used if you set the Heat Sink parameter to "Custom Solution."                                                                                                                                                                                                                                     |

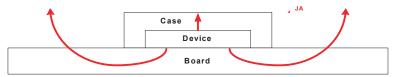

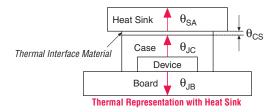

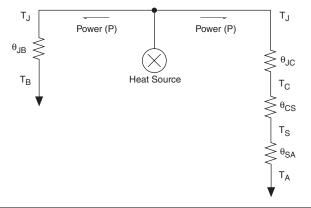

| Board Thermal Model               | Select the type of board to be used in thermal analysis. If no heat sink has been selected, the Altera-provided $\theta_{JA}$ value includes the board thermal pathway. If a board thermal model is selected, you must enter a board temperature in the <b>Board Temp</b> field. This field is only available when <b>Auto Compute T</b> <sub>J</sub> is selected. |

|                                   | Board thermal resistance is a function of device package, number of signal and power layers, % metallization at each layer, inter-layer thickness, and many other parameters. $\theta_{JB}$ values for a typical customer board stack (based on selected device and package) are provided for estimation purposes.                                                 |

|                                   | Users should perform a detailed thermal simulation of their system to determine final junction temperature. This two-resistor thermal model is for early estimation only.                                                                                                                                                                                          |

| Custom $\theta_{JB}$ (°C/W)       | Enter the junction-to-board thermal resistance obtained from thermal simulation if <b>Custom</b> is selected under Board Thermal Model. This field is only available when <b>Auto Compute T</b> <sub>J</sub> is selected.                                                                                                                                          |

| Board Temp, T <sub>B</sub> (°C)   | Enter the temperature on the PCB at the back-side of the device. This temperature is combined with the $\theta_{JB}$ value of the board to compute the junction temperature for the FPGA. This field is only available when <b>Auto Compute T<sub>J</sub></b> is selected.                                                                                         |

|                                   | If the entered board temperature is less than ambient, the tool assumes ambient temperature in its thermal analysis since it is not possible for the board to be below ambient. Similarly, board temperatures in excess of the computed junction temperature are capped to the junction temperature.                                                               |

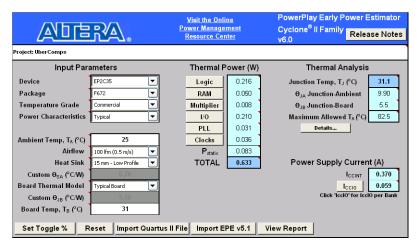

Figure 3–1 shows the **Main** section of the Cyclone II PowerPlay Early Power Estimator spreadsheet.

Figure 3–1. Cyclone II PowerPlay Early Power Estimator Spreadsheet Main Section

#### Logic

A design is a combination of several design modules operating at different frequencies and toggle rates. Each design module can have a different amount of logic. For the most accurate power estimation, partition the design into different design modules. You can partition your design by grouping modules by clock frequency, location, hierarchy, or entities.

Each row in the **Logic** section represents a separate design module. You must enter the following parameters for each design module

- Clock frequency (f<sub>MAX</sub>) in MHz

- Number of look-up tables (LUTs)

- Number of registers

- Toggle percentage

Table 3–2 describes the values that need to be entered in the **Logic** section of the PowerPlay Early Power Estimator spreadsheet.

| <b>Column Heading</b>         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module                        | Enter a name for the module in this column. This is an optional value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Clock Freq                    | Enter the clock frequency for the module in MHz. This value is limited by the maximum frequency specification for the device family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| # of LUTs                     | Enter the number of LUTs used in the whole design as reported in the Quartus II software Compilation Report in the Fitter > Resource Section > Resource Usage Summary section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                               | For the number of LUTs used, add the values from the following rows in the Fitter Resource Usage Summary:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| # of FFs                      | Enter the number of registers used in the whole design as reported in the Quartus II software Compilation Report. The number of registers used in Cyclone II devices is reported in the Total registers row in the Fitter > Resource Section > Resource Usage Summary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Toggle %                      | The average percentage of logic toggling on each clock cycle. The toggle percentage ranges from 0 to 100%. Typically, the toggle percentage is 12.5%, which is the toggle percentage of a 16-bit counter. To ensure you do not underestimate the toggle percentage, you can use a higher toggle percentage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

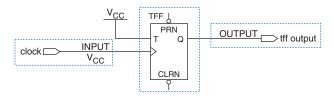

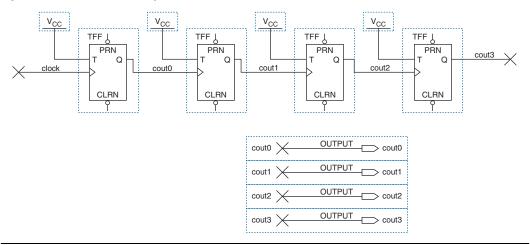

|                               | For example, a TFF with its input tied to $V_{CC}$ has a toggle rate of 100% because its output is changing logic states on every clock cycle. Refer to Figure 3–2 for an example. Figure 3–3 shows an example of a 4-bit counter. The first TFF with least significant bit (LSB) output <code>cout0</code> has a toggle rate of 100% because <code>cout0</code> toggles on every clock cycle. The toggle rate for the second TFF with output <code>cout1</code> is 50% since <code>cout1</code> only toggles on every two clock cycles. Consequently, the toggle rate for the third TFF with output <code>cout2</code> and fourth TFF with output <code>cout3</code> are 25% and 12.5%, respectively. Therefore, the average toggle percentage for this 4-bit counter is $(100 + 50 + 25 + 12.5)/4 = 46.875\%$ . |

| Thermal Power (W),<br>Routing | This shows the estimated power consumed by the routing in W. This value is calculated automatically.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Thermal Power (W), Block      | This shows the estimated power consumed by the logic elements (LEs) in W. This value is calculated automatically.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Thermal Power (W), Total      | This shows the estimated power in W, based on the inputs you entered. It is the total power consumed by logic and is equal to the routing power and the block power. This value is calculated automatically.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| User Comments                 | Enter any comments. This is an optional entry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Figure 3-2. TFF Example

Figure 3-3. 4-Bit Counter Example

Figure 3–4 shows the Resource Usage Summary in the Quartus II software Compilation Report for a design targeting the Cyclone II device family. The Compilation Report provides the total number of LUTs and registers used by the design.

Figure 3-4. Cyclone II Resource Usage Summary in Compilation Report

| Total logic elements                        | 10,595 / 33,216 ( 31 % )                        |

|---------------------------------------------|-------------------------------------------------|

| Combinational with no register              | 9391                                            |

| Register only                               | 157                                             |

| Combinational with a register               | 1047                                            |

| Logic element usage by number of LUT inputs |                                                 |

| 4 input functions                           | 1648                                            |

| 3 input functions                           | 8008                                            |

| <=2 input functions                         | 782                                             |

| Register only                               | 157                                             |

| Combinational cells for routing             | 145                                             |

| Logic elements by mode                      |                                                 |

| normal mode                                 | 5265                                            |

| arithmetic mode                             | 5173                                            |

| Total registers                             | 1,204 / 33,216 ( 3 % )                          |

| Total LABs                                  | 863 / 2,076 ( 41 % )                            |

| User inserted logic elements                | 0                                               |

| Virtual pins                                | 0                                               |

| I/O pins                                    | 131 / 475 ( 27 % )                              |

| Clock pins                                  | 4/8(50%)                                        |

| Global signals                              | 8                                               |

| M4Ks                                        | 20 / 105 (19%)                                  |

| Total memory bits                           | 90,112 / 483,840 ( 18 % )                       |

| Total RAM block bits                        | 92,160 / 483,840 ( 19 % )                       |

| Embedded Multiplier 9-bit elements          | 6/70(8%)                                        |

| Global clocks                               | 8/16(50%)                                       |

| Maximum fan-out node                        | LPLL:inst5 altpll:altpll_componentl_clk0~clkctr |

| Maximum fan-out                             | 1014                                            |

| Total fan-out                               | 35425                                           |

| Average fan-out                             | 2.96                                            |

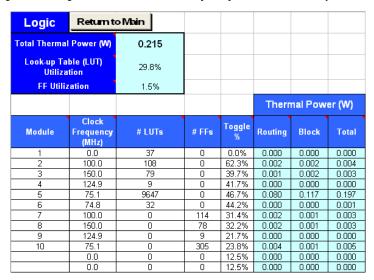

Figure 3–5 shows the Cyclone II device PowerPlay Early Power Estimator spreadsheet and the estimated power consumed by the logic in this design.

Figure 3–5. Logic Section in the PowerPlay Early Power Estimator Spreadsheet

#### **RAM Blocks**

Cyclone II devices feature M4K RAM blocks.

Each row in the **RAM** section represents a design module where the RAM block(s) have the same data width, RAM mode, port parameters and output toggle rate. If some or all of the RAM blocks in your design have different configurations, enter the information in different rows. For each design module, you need to enter the number of RAM blocks, the data width, the RAM mode and the output toggle rate. You must also enter the following parameters for each port:

- Clock frequency, in MHz

- The percentage of time the RAM clocks are enabled

- The percentage of time the port is writing compared to reading

When selecting the RAM block mode, you must know how your RAM will be implemented by the Quartus II Compiler. For example, if a ROM is implemented with two ports, it will be considered a true dual-port memory and not a ROM. Single-port and ROM implementations only use port A. Simple dual-port and true dual-port implementations will use port A and port B.

Table 3–3 describes the parameters in the **RAM** section of the PowerPlay Early Power Estimator spreadsheet.

| Column Heading      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module              | Enter a name for the RAM module in this column. This is an optional value.                                                                                                                                                                                                                                                                                                                                                                                                     |

| # RAM Blocks        | Enter the number of RAM blocks in the module that have the same data width, RAM mode, port parameters, and output toggle rate. The parameters for each port are: clock frequency in MHz, the percentage of time the RAM clocks are enabled, and the percentage of time the port is writing as opposed to reading. The number of RAM blocks reported can be found in the M4K row of the Quartus II Compilation Report under Fitter > Resource Section > Resource Usage Summary. |

| Data Width          | Enter the width of the data for the RAM block. This value must be between 1 and 18 for RAM blocks in true dual-port mode. This value must be between 1 and 36 for all other RAM modes. For RAM blocks that have different widths for port A and port B, use the larger of the two widths. The width of the RAM block can be found in the Port A Width or the Port B Width column of the Quartus II Compilation Report under Fitter > Resource Section > RAM Summary.           |

| RAM Mode            | Select from the following modes: Single-Port, Simple Dual-Port, True Dual-Port, ROM. The mode is based on how the Quartus II Compiler will implement the RAM. If you are unsure how your memory module will be implemented it is best to compile a test case in the required configuration in the Quartus II software. The RAM mode can be found in the Mode column of the Quartus II Compilation Report under Fitter > Resource Section > RAM Summary.                        |

| Port A – Clock Freq | Enter the clock frequency for port A of the RAM block(s) in MHz. This value is limited by the maximum frequency specification for the RAM type and device family.                                                                                                                                                                                                                                                                                                              |

| Port A – Enable %   | Enter the average percentage of time the input clock enable for port A is active, regardless of activity on RAM data and address inputs. The enable percentage ranges from 0 to 100%. The default is set to 25%.                                                                                                                                                                                                                                                               |

| Port A – Write %    | Enter the average percentage of time port A of the RAM block is in write mode versus read mode. This is ignored for RAM blocks in ROM mode.                                                                                                                                                                                                                                                                                                                                    |

| Port B – Clock Freq | Enter the clock frequency for port B of the RAM block(s) in MHz. This value is limited by the maximum frequency specification for the RAM type and device family. Port B is ignored for RAM blocks in ROM or single-port mode.                                                                                                                                                                                                                                                 |

| Port B – Enable %   | Enter the average percentage of time the input clock enable for port B is active, regardless of activity on RAM data and address inputs. The enable percentage ranges from 0 to 100%. The default is set to 25%. Port B is ignored for RAM blocks in ROM or single-port mode.                                                                                                                                                                                                  |

| Port B – R/W %      | For RAM blocks in true dual-port mode, enter the average percentage of time port B of the RAM block is in write mode versus read mode. For RAM blocks in simple dual-port mode, enter the percentage of time port B of the RAM block is reading. You cannot write to port B in simple dual-port mode. Port B is ignored for RAM blocks in ROM or single-port mode.                                                                                                             |

| Table 3–3. RAM Section Information (Part 2 of 2) |                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Column Heading                                   | Description                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Toggle %                                         | Average percentage of clock cycles that each block output signal changes value. Multiplied by clock frequency to determine number of transitions per second.                                                      |  |  |  |  |  |  |  |  |  |

|                                                  | 50% corresponds to a randomly changing signal. A random signal changes states only half the time.                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Valid Width/Mode                                 | This check will fail if the entered data width exceeds that allowed by the RAM mode. See the description of the data width column for details.                                                                    |  |  |  |  |  |  |  |  |  |

| Thermal Power (W),<br>Routing                    | This shows the estimated power consumed by the routing in W. This value is calculated automatically.                                                                                                              |  |  |  |  |  |  |  |  |  |

| Thermal Power (W), Block                         | This shows the estimated power consumed by the RAM blocks in W. This value is calculated automatically.                                                                                                           |  |  |  |  |  |  |  |  |  |

| Thermal Power (W), Total                         | This shows the estimated power in W, based on the inputs you entered. It is the total power consumed by RAM blocks and is equal to the routing power and the block power. This value is calculated automatically. |  |  |  |  |  |  |  |  |  |

| User Comments                                    | Enter any comments. This is an optional entry.                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

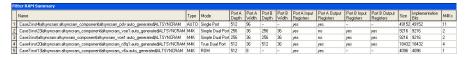

Figure 3–6 shows the Resource Usage Summary section in the Quartus II software Compilation Report for a design targeting the Cyclone II device family. The Compilation Report provides the number of RAM resources being used. Figure 3–7 shows the RAM Summary in the Quartus II software Compilation Report for a design targeting the Cyclone II device family. The Compilation Report provides the RAM mode and the data width.

Figure 3-6. Resource Usage Summary

| Total logic elements                        | 10,595 / 33,216 ( 31 % )                        |

|---------------------------------------------|-------------------------------------------------|

| Combinational with no register              | 9391                                            |

| Register only                               | 157                                             |

| Combinational with a register               | 1047                                            |

| Logic element usage by number of LUT inputs |                                                 |

| 4 input functions                           | 1648                                            |

| 3 input functions                           | 8008                                            |

| <=2 input functions                         | 782                                             |

| Register only                               | 157                                             |

| Combinational cells for routing             | 145                                             |

| Logic elements by mode                      |                                                 |

| normal mode                                 | 5265                                            |

| arithmetic mode                             | 5173                                            |

| Total registers                             | 1,204 / 33,216 ( 3 % )                          |

| Total LABs                                  | 863 / 2,076 ( 41 % )                            |

| User inserted logic elements                | 0                                               |

| Virtual pins                                | 0                                               |

| I/O pins                                    | 131 / 475 ( 27 % )                              |

| Clock pins                                  | 4/8(50%)                                        |

| Global signals                              | 8                                               |

| M4Ks                                        | 20 / 105 (19%)                                  |

| Total memory bits                           | 90,112 / 483,840 ( 18 % )                       |

| Total RAM block bits                        | 92,160 / 483,840 ( 19 % )                       |

| Embedded Multiplier 9-bit elements          | 6/70(8%)                                        |

| Global clocks                               | 8/16(50%)                                       |

| Maximum fan-out node                        | LPLL:inst5laltpll:altpll_componentl_clk0~clkctr |

| Maximum fan-out                             | 1014                                            |

| Total fan-out                               | 35425                                           |

| Average fan-out                             | 2.96                                            |

Figure 3-7. RAM Summary in Compilation Report

Figure 3–8 shows the Cyclone II device PowerPlay Early Power Estimator spreadsheet and the estimated power consumed by RAM blocks in this design.

RAM Return to Main Total Thermal Power (W) 0.050 M4K Utilization 23.8% Port A Port B Thermal Power (W) Clock Enable Enable # RAM Data RAM Write R/W Toggle Module Freq Width Routing Block Total Freq Blocks Width Mode (MHz MHz Mode 6 Single-Port 75.1 100% 50% 0.0 0% 0% 50.0% Yes 0.000 0.001 0.001 Simple Dual-Port 100% 2 18 100.0 50% 100.0 100% 100% 50.0% Yes 0.001 0.003 0.005 3 9 True Dual-Port 100.0 100% 50% 150.0 0.022 0.025 4 100% 50% 50.0% Yes 0.003 ROM 124.9 100% 50.0% 0.000 0.001 0.002 8 0% 0.0 0% 0% Yes 5 10 9 Single-Port 75.1 100% 50% 0.0 0% 0% 50.0% Yes 0.003 0.008 0.011 Simple Dual-Port 6 2 18 150.0 100% 50% 150.0 100% 100% 50.0% Yes 0.002 0.005 0.007 0 1 Simple Dual-Port 0.0 25% 50% 0.0 25% 50% 50.0% 0.000 0.000 0.000 Yes 0 Simple Dual-Port ▼ 0.000 1 0.0 25% 50% 0.0 25% 50% 50.0% Yes 0.000 0.000

Figure 3–8. RAM Section in the PowerPlay Early Power Estimator Spreadsheet

#### **Multiplier Blocks**

Cyclone II devices implement DSP functions in embedded multipliers. These embedded multiplier blocks are optimized for multiplier-intensive low-cost (DSP) applications. The **Multiplier** section in the Cyclone II PowerPlay Early Power Estimator spreadsheet provides power information for Cyclone II multiplier blocks.

Each row in the **Multiplier** section represents a multiplier design module where all instances of the module have the same configuration, clock frequency, toggle percentage and register usage. If some (or all) multiplier instances have different configurations, you need to enter the information in different rows. You must enter the following information for each multiplier module:

- Configuration

- $\blacksquare$  Clock frequency ( $f_{MAX}$ ) in MHz

- Number of instances

- Toggle percentage of the data outputs

- Whether or not the inputs and outputs are registered

For more information on Cyclone II embedded multiplier configurations, see the *Embedded Multipliers in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

Table 3–4 describes the values that need to be entered in the **Multiplier** section of the PowerPlay Early Power Estimator spreadsheet.

| Column Heading                | Description                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Module                        | Enter a name for the embedded multiplier module in this column. This is an optional value.                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Configuration                 | Select the multiplier block configuration. Cyclone II embedded multiplier blocks offer the following configurations:  9 × 9 multiplier  18 × 18 multiplier                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Clock Freq                    | Enter the clock frequency for the module in MHz. This value is limited by the maximum frequency specification for the device family.                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| # of Instances                | Enter the number of instances that have the same configuration, clock frequency, toggle percentage and register usage. This value is independent of the number of multiplier blocks being used.                                                                                  |  |  |  |  |  |  |  |  |  |

| Toggle %                      | Enter the average percentage of the multiplier block data outputs toggling on each clock cycle. The toggle percentage ranges from 0 to 50%. Typically the toggle percentage is 12.5%. For a more conservative power estimate, you can use a higher toggle percentage.            |  |  |  |  |  |  |  |  |  |

| Reg Inputs?                   | Select whether the input to the multiplier block is registered using the dedicated input registers. If the dedicated input registers in the multiplier block are being used, select <b>Yes</b> . If the inputs are registered using registers in LEs, then select <b>No</b> .    |  |  |  |  |  |  |  |  |  |

| Reg Outputs?                  | Select whether the input to the multiplier block is registered using the dedicated output registers. If the dedicated output registers in the multiplier block are being used, select <b>Yes</b> . If the outputs are registered using registers in LEs, then select <b>No</b> . |  |  |  |  |  |  |  |  |  |

| Thermal Power (W),<br>Routing | This shows the estimated power consumed by the routing in W. This value is calculated automatically.                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Thermal Power (W), Block      | This shows the estimated power consumed by the multipliers in W. This value is calculated automatically.                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Thermal Power (W), Total      | This shows the estimated power in W, based on the inputs you entered. It is the total power consumed by multiplier blocks and is equal to the routing power and the block power. This value is calculated automatically.                                                         |  |  |  |  |  |  |  |  |  |

| User Comments                 | Enter any comments. This is an optional entry.                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

Figure 3–9 shows the Cyclone II device PowerPlay Early Power Estimator spreadsheet and the estimated power consumed by the multiplier blocks in this design.

Multiplier Return to Main Total Thermal Power (W) 0.007 Estimated Multiplier Utilization Thermal Power (W) # of Reg Module Configuration Routing Block Total Freq Instances Inputs? Outputs? 18×18 Multiplier 100.0 28.3% No Yes 0.001 0.002 0.002 1 2 18x18 Multiplier 150.0 21.1% No Yes 0.001 0.002 0.003 9x9 Multiplier 100.0 34.0% Yes Yes 0.000 0.001 0.001 ▼ 9x9 Multiplier 150.0 36.4% Yes 0.001 0.001 0.001 Yes 9x9 Multiplier 0.0 0 12.5% Yes 0.000 0.000 0.000 9x9 Multiplier 0.0 0.000 0.000 0.000 0 12.5% Yes Yes 9x9 Multiplier 0.0 12.5% 0.000 0.000 0.000 0 Yes Yes

Figure 3–9. Multiplier Section in the PowerPlay Early Power Estimator Spreadsheet

#### General I/O Pins

Cyclone II devices feature programmable I/O pins that support a wide range of industry I/O standards for increased design flexibility. The **I/O** section in the PowerPlay Early Power Estimator spreadsheet allows you to estimate the I/O pin power consumption based on the pin's I/O standards.

The PowerPlay Early Power Estimator spreadsheet assumes you are using external termination resistors when you design with I/O standards that recommend termination resistors (e.g., SSTL and HSTL). If your design does not use external termination resistors, you should choose the LVTTL I/O standard with the same  $V_{\rm CCIO}$  and similar drive strength as the terminated I/O standard. For example, if you are using the SSTL-2 class II I/O standard without termination resistors (using a point-to-point connection), you should select LVTTL/LVCMOS 2.5-V as your I/O standard and 16mA as the Drive Strength in the PowerPlay Early Power Estimator spreadsheet.

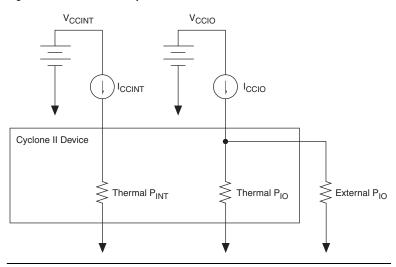

The power reported for I/O signals includes thermal and external I/O power. The total thermal power is the sum of the thermal power consumed by the device based on each power rail.

thermal power = thermal  $P_{INT}$  + thermal  $P_{IO}$

Figure 3–10 shows a graphical representation of the I/O power consumption. The  $I_{CCIO}$  rail power includes both the thermal  $P_{IO}$  and the external  $P_{IO}$ .

Figure 3-10. I/O Power Representation

The  $V_{REF}$  pins consume minimal current (less than 10  $\mu A)$  and is negligible when compared to the power consumed by the general purpose I/O pins. Therefore, the PowerPlay Early Power Estimator spreadsheet does not include the current for  $V_{REF}$  pins in the calculations.

Each row in the **I/O** section represents a design module where the I/O pins have the same frequency, toggle percentage, average capacitive load, I/O standard, data rate, and I/O bank. You must enter the following parameters for each design module:

- I/O standard

- Clock frequency (f<sub>MAX</sub>) in MHz

- Number of output, input, and bidirectional pins

- I/O bank

- Pin toggle percentage

- Output enable percentage

- Average capacitance of the load

- I/O data rate

Table 3–5 describes the I/O bank parameters in the I/O section of the PowerPlay Early Power Estimator spreadsheet.

| Table 3–5. I/O Bank Information in the I/O Section |                                                                                                                                                                                |  |  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Column Heading                                     | Description                                                                                                                                                                    |  |  |  |  |  |  |

| V <sub>CCIO</sub>                                  | Select the $V_{\text{CCIO}}$ voltage for each bank. Used to cross-check selected I/O standards in table below for warning purposes.                                            |  |  |  |  |  |  |

| I <sub>CCIO</sub> (A)                              | This shows the total supply current due to the I/O pins in each I/O bank. This may be higher than the thermal power due to current supplied to off-chip termination resistors. |  |  |  |  |  |  |