## 3. Stratix II GX Dynamic Reconfiguration

SIIGX52007-1.1

#### Introduction

The Stratix® II GX gigabit transceiver block gives you a simplified means to dynamically reconfigure:

- Transmit and receive analog settings

- Transmit data rate in the multiples of 1, 2, and 4

- One channel at a time

- Channel and clock multiplier unit (CMU) PLL

- CMU PLL only

Typically, to achieve the intended bit error rate (BER) for a system, you will take advantage of the multiple analog settings provided in the Stratix II GX device. Being able to change the analog settings is a powerful tool that you can use during link and system debug.

The following analog settings can be dynamically changed:

- Pre-emphasis settings

- Equalization settings

- DC gain settings

- Voltage output differential (V<sub>OD</sub>) settings

In addition to allowing you to change the equalization settings during runtime, the dynamic reconfiguration controller provides an option to dynamically control the adaptive equalization (AEQ) hardware present in each of the transceiver channels. The AEQ hardware continuously tunes the receiver equalization settings based on the frequency content of the incoming signal.

The dynamic data rate switch feature on the transmitter is enabled through a PLD signal. Depending on the setting of this signal, the transmitter data rate can be divided in steps of 1, 2, or 4 per channel.

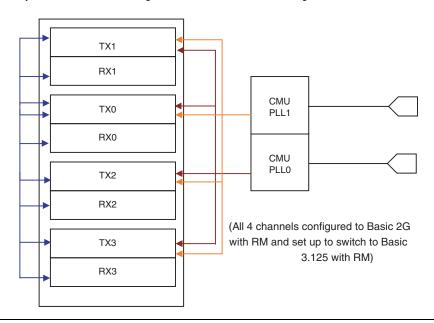

Another important feature is the ability to dynamically reconfigure from one mode to another mode. This mode reconfiguration may involve reconfiguring the transceiver data path or data rate or both. You can reconfigure the transceiver data rate either by switching to the other CMU PLL or by dynamically reconfiguring the CMU PLL. The former is enabled in the Quartus® II software version 6.1 and later, while the latter is enabled in the Quartus II software version 7.1 and later.

The dynamic reconfiguration feature facilitates mode transitions involving:

- Protocol functional mode (x1 only) to and from Basic functional mode

- Protocol functional mode (x1 only) to Protocol functional mode (x1 only)

- One Basic functional mode to other Basic functional modes

This is a very useful and powerful feature for transceiver system applications because it enables channels in a system to adapt to multiple serial data rates and system protocols.

Table 3–1 shows dynamic reconfiguration features supported in various Quartus II software versions.

| Table 3–1. Software Support for Dynamic Reconfiguration |                                                                  |                                                 |                            |                                           |                                 |

|---------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------|----------------------------|-------------------------------------------|---------------------------------|

| Version                                                 | Transmitter and<br>Receiver Analog<br>Settings<br>(PMA Controls) | Transmitter Data<br>Rate Switch<br>(×1, ×2, ×4) | Channel<br>Reconfiguration | Channel and<br>CMU PLL<br>Reconfiguration | CMU PLL-Only<br>Reconfiguration |

| Quartus II 6.0                                          | <b>✓</b>                                                         | _                                               | _                          | _                                         | _                               |

| Quartus II 6.1                                          | <b>✓</b>                                                         | <b>✓</b>                                        | ~                          | _                                         | _                               |

| Quartus II 7.1                                          | ✓                                                                | ✓                                               | ✓                          | <b>✓</b>                                  | <b>✓</b>                        |

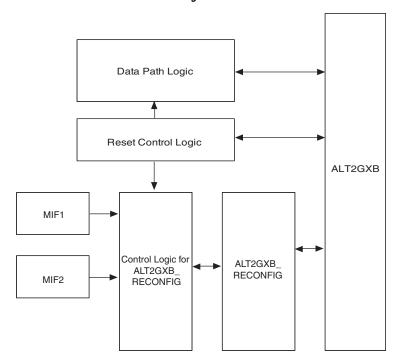

# Dynamic Reconfiguration Controller Architecture

The Stratix II GX device offers a simplified dynamic reconfiguration controller in the Quartus II ALT2GXB\_RECONFIG module to control the configurable settings of the transceiver. The dynamic reconfiguration controller is a soft IP which utilizes Stratix II GX device PLD resources. It is optimized for minimal PLD resource usage. Only one controller is allowed per transceiver block. The dynamic reconfiguration controller does not have the capability to control multiple Stratix II GX devices or any off-chip interface.

The dynamic reconfiguration capability is only intended for Stratix II GX devices, having no backward compatibility to Stratix GX devices.

Stratix II GX dynamic reconfiguration is very flexible because of the following features:

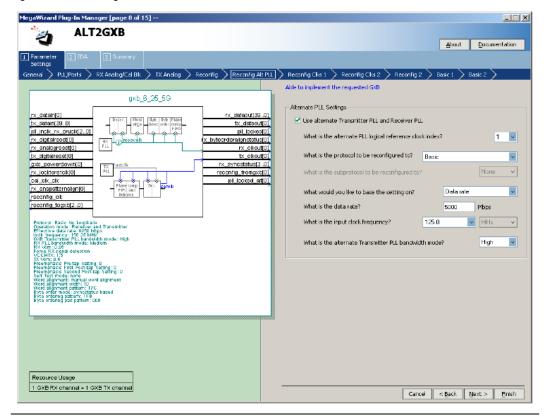

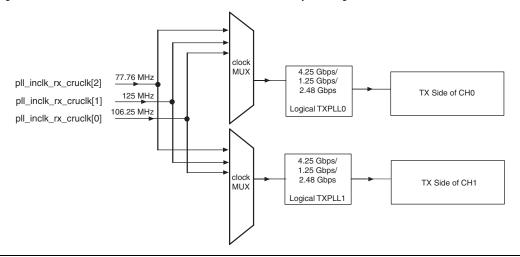

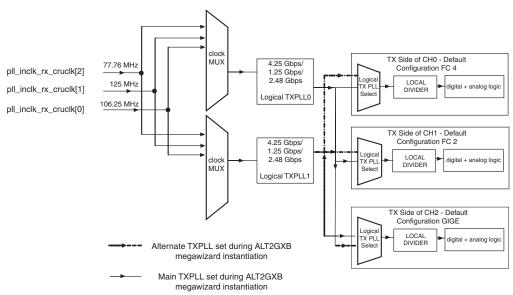

Two transmit PLLs enabled—This allows you to achieve multiple data rates and protocols in a single transceiver block.

- Basic double-width modes—The minimum data rate is lowered to 1 Gbps. This helps if you want to only switch data rates without changing the data path width.

- More optional features in Basic mode.

- PLD interface clocking of the transceiver is enhanced by introducing "Core Clocking Options". These core clocking options help you optimize clock resource usage and allows you to set up the proper PLD interface clocking on transmit and receive paths.

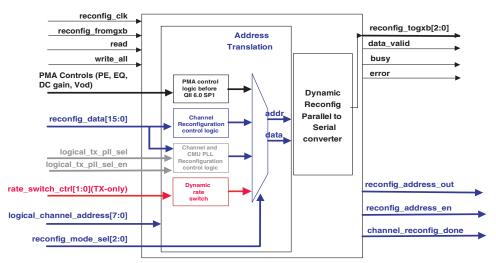

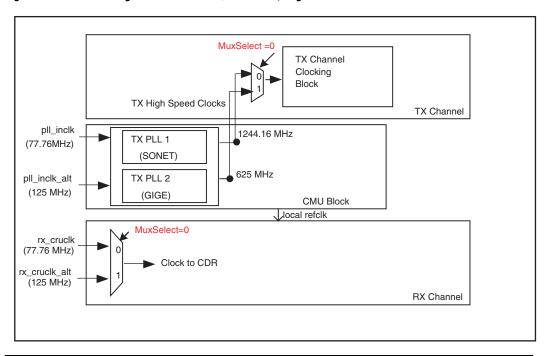

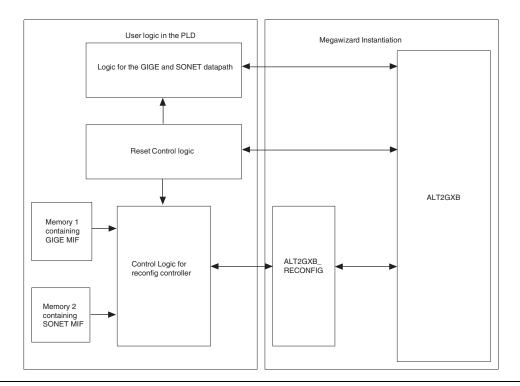

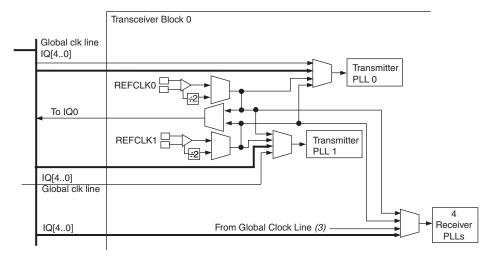

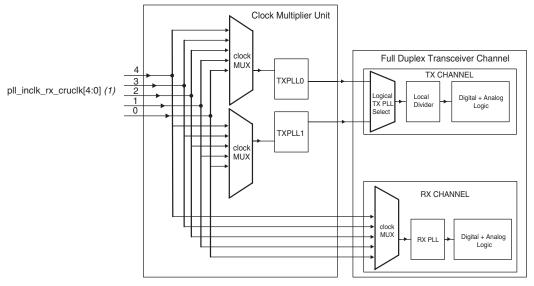

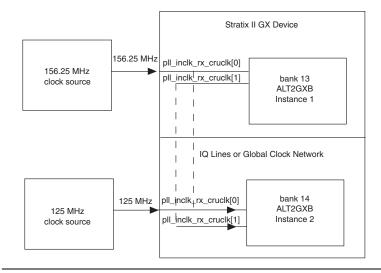

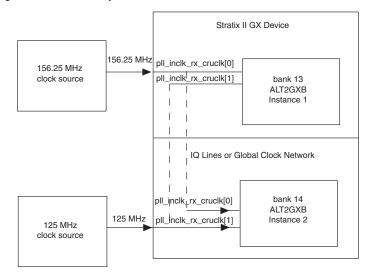

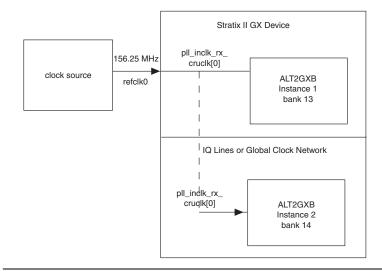

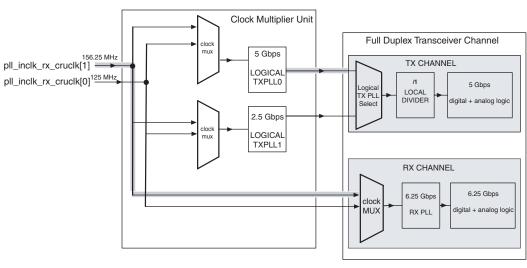

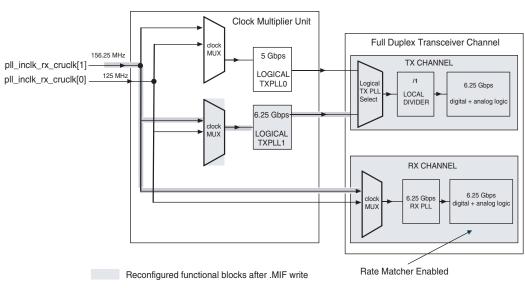

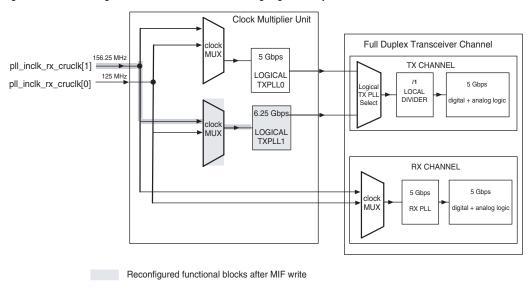

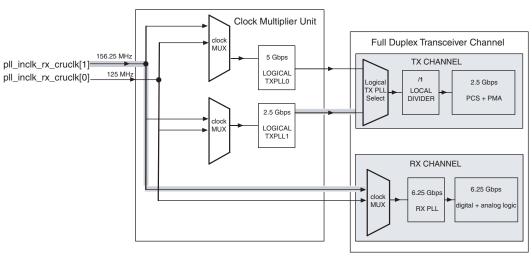

Figure 3–1 shows a conceptual view of these features.

Figure 3–1. Block Diagram of the Dynamic Reconfiguration Controller (ALT2GXB\_RECONFIG)

The following items are not supported as part of the dynamic reconfiguration feature:

- Mode switch to and from any ×4 and ×8 configurations

- Not backward compatible with Stratix GX devices

- To and from PCI Express (PIPE) mode with NFRI IP

- Testability features (pseudo-random binary sequence [PRBS] and built-in self test [BIST])

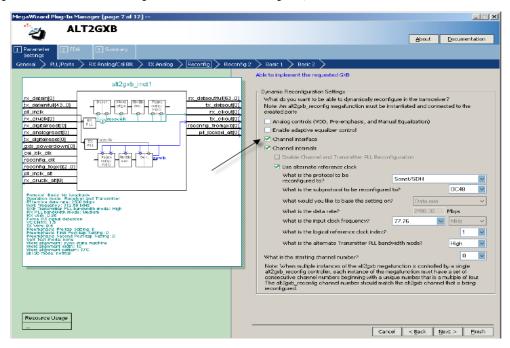

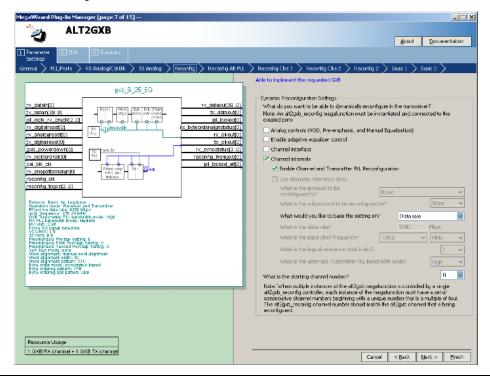

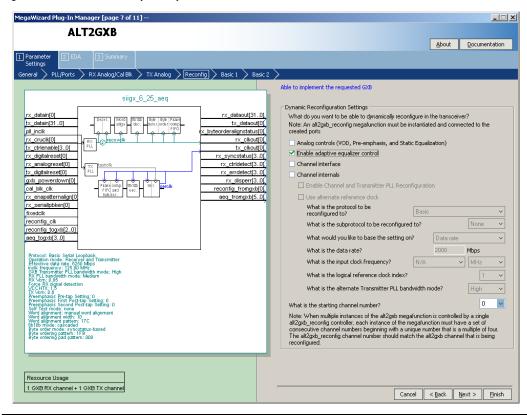

## Dynamic Reconfiguration Setup in the MegaWizard Plug-In Manager

The optional dynamic reconfiguration interface must be enabled through the MegaWizard® Plug-In Manager (dynamic reconfiguration is turned OFF by default).

The dynamic reconfiguration interface has the following signals:

- reconfig togxb[2:0] as an input signal bus

- reconfig\_fromgxb as an output signal from ALT2GXB instance. reconfig\_fromgxb is a transceiver block-based signal; for example, if the number of the channels selected in ALT2GXB are:

- 0 < Channels < 4, then signal reconfig fromgxb = 1 bit</p>

- 4 < Channels < 8, then signal reconfig from gxb = 2 bits

- 8 < Channels < 12, then signal reconfig from gxb = 3 bits

- 12 < Channels < 16, then signal reconfig from gxb = 4 bits

- 16 < Channels < 20, then signal reconfig\_fromgxb = 5 bits</p>

After the dynamic reconfiguration option is enabled in the ALT2GXB MegaWizard, you must set one more setting—the **What is the dynamic reconfig starting channel number?** option. The dynamic reconfiguration starting channel number setting range is from 0 - 156 in multiples of 4 (because the dynamic reconfiguration interface is per transceiver block). This range of 0 - 156 is the logical channel address based purely on the number of possible ALT2GXB instances.

To better understand how logical addressing works, consider the scenario of 20 separate transmit and receive instances of the ALT2GXB megafunction in a design and how to set the address of the starting channel of each instance.

The first instance of a transmit and receive channel has the starting channel number setting of **0**. The second instance of a transmit and receive channel has the starting channel number setting of **4**. And so on. The twentieth instance of the same configuration has the starting channel number of **76**.

Extending the same logic to the maximum possible instances case of 20 transmit-only and 20 receive-only configurations, targeted for a five transceiver block Stratix II GX device, the maximum starting channel number of the dynamic reconfiguration option is **156** (40 instances \* 4).

Configure the ALT2GXB\_RECONFIG and the ALT2GXB modules, depending on the number of transceiver channels that are controlled by the dynamic reconfig controller (ALT2GXB\_RECONFIG). Use the logical channel views with the above mentioned logical addressing in the

ALT2GXB instance. The Quartus II fitter errors out if the dynamic reconfiguration option is enabled in the ALT2GXB megafunction, but the reconfig\_fromgxb and reconfig\_togxb ports are NOT connected to the ALT2GXB\_RECONFIG instance.

The megafunction and pre-fitter automatically map the logical channel into the physical placements. This physical placement includes merging (automatically done by the Quartus II software). The software performs merging (packing channels into the same transceiver block) only when multiple channels of the same data rate and data path configuration are controlled by one dynamic reconfiguration (ALT2GXB\_RECONFIG) controller instance. Channels connected to multiple ALT2GXB\_RECONFIG controllers will not be merged.

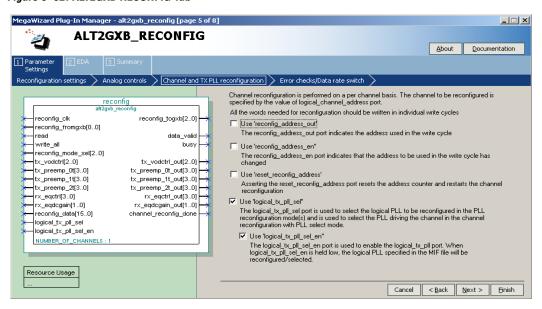

#### Dynamic Reconfiguration Controller Interface

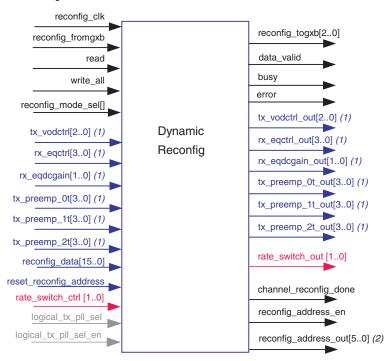

The dynamic reconfiguration controller supports write and read transactions. Figure 3–2 shows the dynamic reconfiguration interface list. The following transactions are allowed, based on the dynamic reconfiguration features:

- Analog Settings Reconfiguration—Write and Read (read is optional)

- Channel Reconfiguration—Write Transaction Only

- Dynamic Transmit Rate Switch—Write and Read (read is optional)

- Channel and CMU PLL Reconfiguration

- CMU PLL-Only Reconfiguration

Figure 3-2. Dynamic Reconfiguration Interface

#### *Notes to Figure 3–2:*

- Optional control and status signals. At least one control signal must be enabled if only analog settings reconfiguration is enabled.

- (2) If the channel reconfiguration feature is selected in the ALT2GXB\_RECONFIG MegaWizard, the reconfig\_address\_out is 5-bits wide [4..0]. If the Channel and TXPLL select/reconfig feature is selected, the reconfig\_address\_out is 6-bits wide [5..0].

The reconfig\_mode\_sel signal determines the reconfiguration mode. This control signal is 3-bits wide if the **Adaptive Equalization control** option is **not** selected. If this option is selected, the reconfig\_mode\_sel signal is 4-bits wide. Encoding of the reconfig\_mode\_sel signal (when the **Adaptive Equalization control** option is **not** selected) is as follows:

- reconfig mode sel [2:0]:

- 000 Reconfiguration of Analog controls. The Analog controls feature has been enabled in the Quartus II software version 6.0 and later

- 001 Channel Reconfiguration

- 011 Dynamic Transmit rate switch

- 100, 101, 110 Channel and CMU PLL Reconfiguration

Refer to "Channel and PMA Controls Reconfiguration" on page 3–20 and "Channel and Clock Multiplier Unit (CMU) PLL Reconfiguration" on page 3–87 for detailed reconfig\_mode\_sel [2:0] signal encoding.

As described in "Stratix II GX ALT2GXB Megafunction User Guide" on page 4–1, the signals reconfig\_togxb [2:0] and reconfig\_fromgxb are the interface signals between the ALT2GXB instance and the ALT2GXB\_RECONFIG instance. The dynamic reconfiguration controller runs at a frequency determined by the clock reconfig\_clk signal. The supported frequency range of the reconfig\_clk is 2.5 MHz – 50 MHz.

Altera recommends the reconfig\_clk signal be driven on a global clock resource.

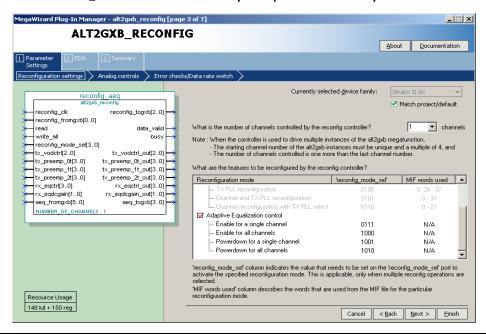

You must set the following two settings in the ALT2GXB\_RECONFIG MegaWizard:

#### 1. What is the number of channels controlled by the controller?

You must provide the number of channels for the megafunction, depending on the design setup supported. There are two ways of using dynamic reconfiguration controllers. They are:

- Single Dynamic Reconfiguration Controller—one controller controlling all the instances of the ALT2GXB in a device. When multiple instances of the ALT2GXB megafunction are controlled by a single ALT2GXB\_RECONFIG controller, the following rules should be followed for setting the "What is the number of channels controlled by the controller?" option:

- Each instance of the megafunction must have a set of the consecutive channel numbers beginning with a unique number that is a multiple of four.

- The number of channels controlled is the last channel number.

- Multiple Dynamic Reconfiguration Controllers—for multiple instances of the ALT2GXB, it is not possible to have two dynamic reconfiguration controllers controlling the same ALT2GXB instance. One controller is allowed to control multiple ALT2GXB instances or every channel will have its own dynamic reconfiguration controller. If every channel has its own dynamic reconfiguration controller, there may be problems with fitting.

- The Quartus II software cannot merge multiple transceiver channel instances into a transceiver block if multiple dynamic reconfiguration controllers are used, even if the channels are configured to the same protocol functional mode and data rate.

For example, ALT2GXB instance1 has five channels of the same data rate and functional mode; ALT2GXB instance2 has three channels of same data rate and functional mode. Both ALT2GXB instances have separate dynamic reconfiguration controllers controlling them. These two ALT2GXB instances (a total of eight channels) cannot be merged into two transceiver blocks. These two instances can be merged only if they are controlled by one dynamic reconfiguration controller. This merging will not change the behavior of the silicon compared to functional simulations.

#### 2. Use the same control signals for all channels.

Check this option when you know that the same analog control signals are used for all the channels in the design. By checking this option, the Quartus II software uses one set of analog signals to control all channels used in all transceiver blocks that are controlled by this reconfiguration controller.

Table 3–2 describes the ports for the dynamic reconfiguration controller.

| Table 3–2. Port List of the Dynamic Reconfiguration Controller (ALT2GXB_RECONFIG) (Part 1 of 6) |                                              |                                                                                                                                                                                                                                                                 |  |  |  |

|-------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port Name                                                                                       | Input/Output                                 | Description                                                                                                                                                                                                                                                     |  |  |  |

| reconfig_clk                                                                                    | Input                                        | Input reference clock for the dynamic reconfiguration controller. The frequency range of this clock is 2.5 MHz to 50 MHz. The assigned clock uses global resources by default. This same clock should be connected to ALT2GXB.                                  |  |  |  |

| ALT2GXB - ALT2GXB_RECONFIG Into                                                                 | ALT2GXB - ALT2GXB_RECONFIG Interface Signals |                                                                                                                                                                                                                                                                 |  |  |  |

| reconfig_fromgxb                                                                                | Input                                        | Interface bus signal from ALT2GXB to ALT2GXB_RECONFIG instance. The width of the signal in ALT2GXB_RECONFIG is determined by the number of channels controlled by the controller.                                                                               |  |  |  |

| reconfig_togxb[20]                                                                              | Output                                       | Fixed bus interface between ALT2GXB_RECONFIG and ALT2GXB. This signal is independent of the number of channels.                                                                                                                                                 |  |  |  |

| PLD Interface Signals                                                                           |                                              |                                                                                                                                                                                                                                                                 |  |  |  |

| write_all                                                                                       | Input                                        | Control signal to initiate a write transaction. This signal is active high. When the analog settings (V <sub>OD</sub> , equalization, etc.) are reconfigured, the reconfiguration controller writes to all the transceiver channels connected to the controller |  |  |  |

| busy                                                                                            | Output                                       | Status signal to indicate that the reconfiguration controller has not completed the read or write transaction.                                                                                                                                                  |  |  |  |

| Port Name  | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| read       | Input        | Control signal to initiate a read transaction. This signal is active high. When the analog settings ( $V_{OD}$ , equalization, etc.) are read, the reconfiguration controller reads the analog setting values from all the transceiver channels connected to the controller. When you select this signal, at least one of the output control ports (for example, $tx\_vodctrl\_out$ ) should be selected. Otherwise, when you initiate a read transaction, the reconfiguration controller may get into a deadlock state (since it cannot send data to any output). |

| data_valid | Output       | Status signal for the read transaction. If data_valid is high, the read back data is valid. That is, the current data on the output control signals after data_valid is asserted high is the valid data read out. This signal is only enabled when at least one read control port is enabled. When a read control port is enabled and a write transaction is finished, the data_valid signal goes high and the busy signal goes low.                                                                                                                               |

| error      | output       | Optional status signal to indicate that an unsupported operation is attempted. The error port can be enabled by selecting the options in the Error checks/data rate switch tab. The dynamic reconfiguration controller de-asserts the busy signal and asserts the error signal for two reconfig_clk cycles when you attempt an unsupported operation.                                                                                                                                                                                                              |

| Port Name                     | Input/Output |                                                                                                                                                                                                                                                                                                                                                                                              | Description                                                   |                                                                                                                        |

|-------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Analog Settings Control/Statu | s Signals    | •                                                                                                                                                                                                                                                                                                                                                                                            |                                                               |                                                                                                                        |

| tx_vodctrl                    | Input        | Optional transmit buffer voltage output differential control signal. It is 3-bits per channel. The number settings varies based on the transmit buffer supply and the termination resistor setting in ALT2GXB in the following shows the V <sub>OD</sub> values corresponding tx_vodctrl settings for 100-Ω termination. For values corresponding to other termination setting to Table 2–8. |                                                               | el. The number of it buffer supply setting in ALT2GXB instance. s corresponding to the ermination. For V <sub>OD</sub> |

| tx_preemp_0t (1)              | Input        | buffer. It is 4-b                                                                                                                                                                                                                                                                                                                                                                            | oits per channel. This positive and its inversory) s -7 to -1 |                                                                                                                        |

| tx_preemp_1t (1)              | Input        | 8 maps to 0                                                                                                                                                                                                                                                                                                                                                                                  | emphasis control for fi                                       | rst post tap for the                                                                                                   |

|                               | <u>'</u>     |                                                                                                                                                                                                                                                                                                                                                                                              | r. It is 4-bits per chan                                      |                                                                                                                        |

| tx_preemp_2t (1)              | Input        | Optional pre-emphasis control for second post-tap for the transmit buffer. It is 4-bits per channel. This signal controls both pre-emphasis positive and its inversion.  0 represents 0 1–7 represents -7 to -1 9–15 represents 1 to 7 8 maps to 0                                                                                                                                           |                                                               |                                                                                                                        |

| rx_eqctrl                     | Input        | Optional equalization control signal on the receive side of the PMA. It is a 4-bit bus per each channel.                                                                                                                                                                                                                                                                                     |                                                               |                                                                                                                        |

| Port Name                       | Input/Output | Description                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rx_eqdcgain (2)                 | Input        | Optional equalizer DC gain control. It supports three legal settings and is 2-bits wide per channel.                                                                                                                                                                                                              |  |

|                                 |              | 00 corresponds to 0 dB<br>01 and 10 correspond to 3 dB<br>11 corresponds to 6 dB                                                                                                                                                                                                                                  |  |

| tx_vodctrl_out                  | Output       | Optional transmit $V_{\rm OD}$ output signal. This signal reads out the value written into the $V_{\rm OD}$ control register. The signal width of this output signal is the same as its corresponding input signal.                                                                                               |  |

| tx_preemp_0t_out                | Output       | Optional pre-tap, pre-emphasis output signal. This signal reads out the value written by its input control signal. The signal width of this output signal is the same as its corresponding input control signal.                                                                                                  |  |

| tx_preemp_1t_out                | Output       | Optional first post-tap, pre-emphasis output signal. This signal reads out the value written by its input control signal. The signal width of this output signal is the same as its corresponding input control signal.                                                                                           |  |

| tx_preemp_2t_out                | Output       | Optional second post-tap pre-emphasis output signal. This signal reads out the value written by its input control signal. The signal width of this output signal is the same as its corresponding input control signal.                                                                                           |  |

| rx_eqctrl_out                   | Output       | Output signal to read the setting of equalization setting of<br>the ALT2GXB instance. The signal width of this output<br>signal is the same as its corresponding input signal.                                                                                                                                    |  |

| rx_eqdcgain_out                 | Output       | Equalizer DC gain output signal. This signal reads out the settings of the ALT2GXB instance DC gain. The signal width of this output signal is the same as its corresponding input signal.                                                                                                                        |  |

| Channel Reconfiguration Signals |              |                                                                                                                                                                                                                                                                                                                   |  |

| reset_reconfig_address          | Input        | Synchronous reset signal to the ALT2GXB_RECONFIG to reset the reconfig_address_out port to <b>0</b> . Use this signal when you want to restart the reconfiguration of a channel by initiating writing the memory initialization file (MIF) word 0.                                                                |  |

| reconfig_data[15:0]             | Input        | Sixteen bits input data word. You input it from the location that has the MIF to reconfigure the registers. This input port is only used in the Channel Reconfiguration or Channel and CMU PLL Reconfiguration feature (discussed in "Channel and Clock Multiplier Unit (CMU) PLL Reconfiguration" on page 3–87). |  |

| Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input        | Select the reconfiguration mode for the ALT2GXB_RECONFIG megafunction. The signal encoding is as follows:  000 - Reconfiguration for analog controls. This feature has been enabled in the Quartus II software version 6.0 and later versions.  001 - Channel Reconfiguration 010 - Not supported (do not attempt to read or write with this value) 011 - Dynamic Transmit data rate switch *100 - TXPLL *101 - Channel and TXPLL reconfiguration *110 - Channel reconfiguration with TXPLL select 111 - Not supported (do not attempt to read or write with this value) *The features corresponding to these values are discussed in "Channel and Clock Multiplier Unit (CMU) PLL Reconfiguration" on page 3–87. |

| Input        | Specify the logical channel address for the channel that needs to be reconfigured. The CHANNEL_ADDRESS_WIDTH parameter is determined through the NUMBER_OF_CHANNELS parameter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Output       | This signal indicates the address out and that the address read out is the current address to be reconfigured by the ALT2GXB_RECONFIG megafunction during channel reconfiguration. This signal is 5-bit wide in channel reconfiguration mode and 6-bit wide in channel and CMU PLL reconfiguration mode.                                                                                                                                                                                                                                                                                                                                                                                                          |

| Output       | This port indicates the current address to be reconfigured for the ALT2GXB_RECONFIG megafunction had already changed during channel reconfiguration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output       | This port indicates that the ALT2GXB_RECONFIG megafunction has finished writing all the words of a MIF. This is only applicable for channel reconfiguration mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| als          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Input        | This input is the control signal to write the desired division factors on a per-channel transmitter basis. This port is only applicable when reconf_mode_sel is set to 011.  The output value is listed below: 00 - Divide by 1 01 - Divide by 2 10 - Divide by 4 11 - Not supported (do not attempt to read or write with                                                                                                                                                                                                                                                                                                                                                                                        |

|              | Input Output Output Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 3–2. Port List of the Dynamic Reconfiguration Controller (ALT2GXB_RECONFIG) (Part 6 of 6) |                                     |                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Port Name                                                                                       | Input/Output                        | Description                                                                                                                                                                                                                                                                            |  |  |

| rate_switch_out[1:0]                                                                            | Output                              | This signal reads out the value that has written in for the rate switch of specified transmitter outputs. This output port is only applicable when reconf_mode_sel is set to <b>011</b> .  The output value is listed below: 00 - Divide by 1 01 - Divide by 2 10 - Divide by 4        |  |  |

| Channel and CMU PLL Reconfiguration                                                             | Channel and CMU PLL Reconfiguration |                                                                                                                                                                                                                                                                                        |  |  |

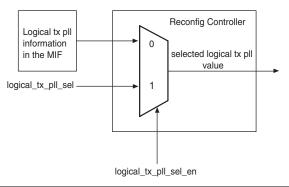

| logical_tx_pll_sel                                                                              | Input                               | This control signal allows you to select the CMU PLL that you wish to reconfigure. It also allows you to select the CMU PLL to which the channel is listening in Channel Reconfiguration with TX PLL Select mode. Refer to "Logical TX PLL Select" on page 3–105 for more information. |  |  |

| logical_tx_pll_sel_en                                                                           | Input                               | This signal validates the <code>logical_tx_pll_sel</code> signal. Refer to "Logical TX PLL Select" on page 3–105 for more information.                                                                                                                                                 |  |  |

#### Notes to Table 3-2:

- (1) Not all combinations of bits are legal values.

- (2) In PIPE mode, this input should be tied to **01** to be PCI E-compliant.

## Dynamic Configuration Controller (ALT2GXB\_RECONFIG), ALT2GXB Design Examples

The following design examples illustrate the various possible topologies of the dynamic reconfiguration controller with ALT2GXB instances. The first two design examples specifically discuss a single controller controlling multiple instances of an ALT2GXB and a single controller controlling one instance of an ALT2GXB. Design example three discusses the HDL construct needs if you are stamping the ALT2GXB instances. Each instance of an ALT2GXB in turn can have more than one transceiver channel. Also, in all the design examples, it is assumed that only the Analog (PMA) settings reconfiguration is enabled, to simplify the illustration. In the real system, you can enable other supported features along with the analog setting reconfiguration.

#### Example 1

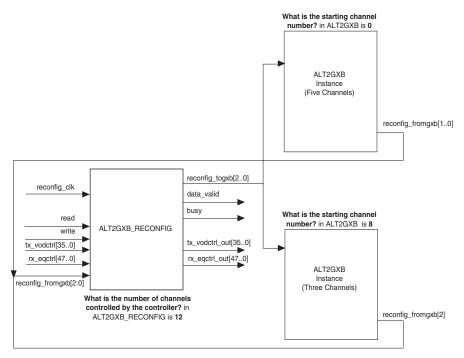

Consider a design with two instances of an ALT2XGB configuration, Instance1 with five transceiver channels and Instance2 with three transceiver channels.

Assume the following for this example:

- Instance1 and Instance2 cannot be merged due to their configurations.

- One dynamic reconfiguration controller controls all eight channels.

- Only the transmit V<sub>OD</sub> and receiver equalization controls are enabled.

The following are the typical steps that help setup the configuration:

#### **Five Channel Transceiver Instance:**

- In the ALT2GXB MegaWizard, set the **What is the number of channels?** option to **5** along with other options in the ALT2GXB MegaWizard.

- Enable the Analog controls option under the dynamic reconfiguration settings (to dynamically change equalization values, also enable the Enable equalizer settings option).

- The output signal reconfig\_fromgxb is transceiver-block based, so the number of bits for this instance is two since the number of channels is five. The input signal reconfig\_togxb is a fixed bus width of three bits.

- Set the What is the starting channel number? option to 0.

#### **Three Channel Transceiver Instance:**

- In the ALT2GXB MegaWizard, set the **What is the number of channels?** option to **3**.

- Enable the **Analog controls** option under the dynamic reconfiguration settings (to dynamically change equalization values, also enable the **Enable equalizer settings** option).

- The output signal reconfig\_fromgxb is transceiver block based, so the number of bits for this instance is one since the number of channels is three. The input signal reconfig\_togxb is a fixed bus width of three bits.

- Set the **What is the starting channel number?** option to **8**. This address of eight is warranted because the previous ALT2GXB instance has five channels which logically fits into two transceiver blocks (transceiver blocks with starting channel numbers 0 and 4), and since this case has multiple instances of the ALT2GXB controlled by one dynamic controller, the numbering is consecutive channel numbers in multiples of four.

#### **ALT2GXB\_RECONFIG Setup for PMA Controls Reconfiguration:**

- Launch the ALT2GXB\_RECONFIG MegaWizard.

- Set the What is the number of channels controlled by the controller? option to 12. The setting for this option has a number that is more than the total number of channels needed to be controlled

(eight channels) by dynamic reconfiguration. This is needed because based on this setting, the Quartus II software chooses the bus width of the signal reconfig\_fromgxb in addition to the width of the analog control signals. In this case, the design needs 3-bits wide signals so the controller can control a total of three transceiver blocks (five channels in two transceiver blocks and three channels into one transceiver block).

To make it simple, choose the channel number based on a rounded-up channel number to the nearest transceiver block multiple. In this case, it is eight channels required and since no merging is allowed, eight channels require three transceiver blocks. The three transceiver blocks round up to a transceiver block multiple channel number of 12 ( $3 \times 4 = 12$ ). Refer to the "1. What is the number of channels controlled by the controller?" option in "Dynamic Reconfiguration Controller Interface" on page 3–5 for more information about this setting.

• Select the necessary analog control signals to write in and read out for V<sub>OD</sub> and equalization from all the options available in the MegaWizard. Also note the analog control signal widths are for 12 channels since the above channel setting is 12. Control signals for unused channels 5 to 7 and channel 11 can be tied to logic low (zero/ground). In this design scenario, the V<sub>OD</sub> signal (tx\_vodctrl) width is 36 bits (12 channel × tx\_vodctrl [2:0] = tx\_vodctrl [35:0]). Tie tx\_vodctrl [35:33] and tx\_vodctrl [23:15] to ground. Use similar methods for the equalization setting.

## ALT2GXB Instances and ALT2GXB\_RECONFIG Instance Connections:

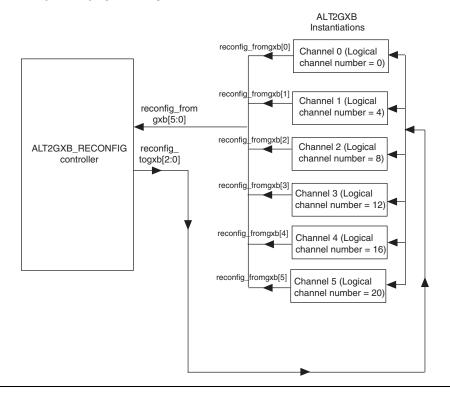

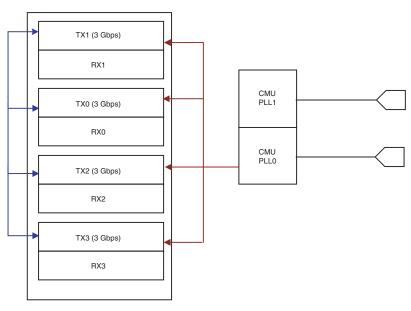

- Connect the reconfig\_fromgxb signal from the ALT2GXB instance to the same signal in the ALT2GXB\_RECONFIG instance. The lowest starting channel number transceiver block is connected to the lowest significant bit and so on. In this case, the configuration instance with five channels of the ALT2GXB instance has a starting channel of zero, which has the signal reconfig\_fromgxb[1:0] which should be connected to reconfig\_fromgxb[1:0] of the ALT2GXB\_RECONFIG instance. The other three channel instances of ALT2GXB, with a starting channel of eight, has the signal reconfig\_fromgxb which should be connected to ALT2GXB\_RECONFIG reconfig\_fromgxb[2]. Refer to Figure 3–3 for more information.

- Connect the reconfig\_togxb signal from the ALT2GXB\_RECONFIG instance to the same signal on the ALT2GXB instance.

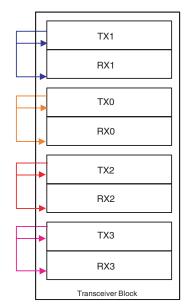

Figure 3-3. ALT2GXB Modules with One ALT2GXB\_RECONFIG Module

#### Example 2

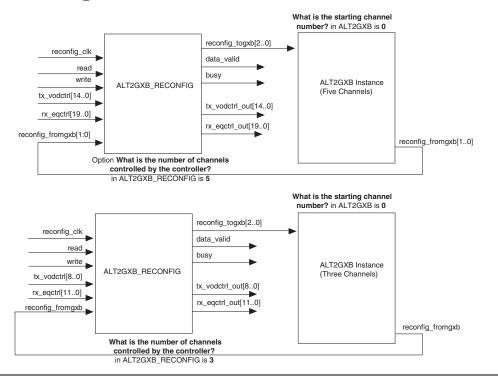

This design example has two instances of distinct configurations: Instance1 with five transceiver channels and Instance2 with three channels. This configuration requires separate dynamic reconfiguration controllers for the two instances. This scenario covers the case of multiple dynamic reconfiguration controllers controlling multiple instances of the ALT2GXB. Assume that the analog settings (transmit  $V_{\rm OD}$  and receive equalization controls) for both instances are enabled. The following are the typical steps to setup the configuration:

#### **Five Channel Transceiver Instance1:**

- In the ALT2GXB MegaWizard, set the **What is the number of channels?** option to 5 along with other options in the ALT2GXB MegaWizard.

- Enable the Analog controls option under the dynamic reconfiguration settings (to dynamically change equalization values, also enable the Enable equalizer settings option).

- The output signal reconfig\_fromgxb is transceiver-block based so the number of bits for this instance is two since the number of channels is five. The input signal reconfig\_togxb is a fixed width of three bits.

- Set the **What is the starting channel number?** option to **0**.

#### **Dynamic Reconfiguration Controller Instance1:**

- Launch the ALT2GXB\_RECONFIG MegaWizard.

- Set the What is the number of channels controlled by the controller? option to 5. This option helps the Quartus II software choose the bus width of the signal reconfig\_fromgxb in addition to the width of the analog control signals. In this case, the design needs 2-bits wide signals so the controller can control a total of two transceiver blocks (five channels in two transceiver blocks). Refer to "Introduction" on page 3–1 for more information about this setting.

- Select the necessary analog control signals to write in and read out from the V<sub>OD</sub>, pre-emphasis, equalization, and DC gain options for this setup.

#### Three Channel Transceiver Instance2:

- Set the What is the number of channels? option to 3.

- Enable the **Analog controls** option under the dynamic reconfiguration settings (to dynamically change equalization values, also enable the **Enable equalizer settings** option).

- The output signal reconfig\_fromgxb is transceiver block based so the number of bits for this instance is one since the number of channels is three. The input signal reconfig\_togxb is a fixed width of three bits.

- Set the **What is the starting channel number?** option to **0**. This address number of 0 is the same as the previous five channel ALT2GXB instance setting. You do not need to have a consecutive channel starting number (multiples of four) since these two ALT2GXB instances are controlled by different dynamic reconfiguration controllers.

#### **Dynamic Reconfiguration Controller Instance2:**

- Launch the ALT2GXB\_RECONFIG MegaWizard.

- Set the What is the number of channels controlled by the controller? option to 3. This option helps the Quartus II software choose the bus width of the signal reconfig\_fromgxb, in addition to the width of the analog control signals. In this case, the design needs a 1-bit wide signal so the controller can control a total of one transceiver block (three channels into one transceiver block) and have the option set to at least three so that the Quartus II software enables three channels of the analog control signals in the options sections.

Select the necessary analog control signals to write in and read out from the V<sub>OD</sub>, pre-emphasis, equalization, and DC gain options.

## ALT2GXB Instances and ALT2GXB\_RECONFIG Instance Connections:

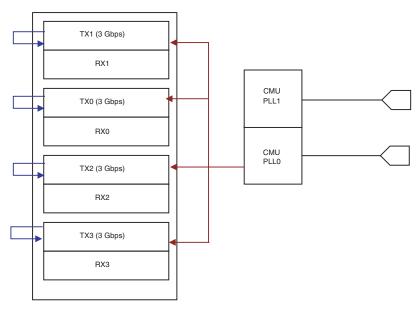

- Connect the reconfig\_fromgxb signal from the ALT2GXB instance to the same signal of the corresponding ALT2GXB\_RECONFIG instance. Refer to Figure 3–4 for more information.

- Connect the reconfig\_togxb signal from the ALT2GXB\_RECONFIG instance to the same signal of the corresponding ALT2GXB instance.

Figure 3-4. ALT2GXB\_RECONFIG Modules with Two ALT2GXB Modules

#### Example 3

This design example consists of five channels of transceivers with the same data rate and functional mode. This configuration has one dynamic reconfiguration controller to control five channels. This scenario covers the case stamping five instantiations of one channel ALT2GXB instance configuration.

#### One Channel ALT2GXB Configuration:

- Set the What is the number of channels? option to 1 along with other options in the ALT2GXB MegaWizard.

- Enable the Analog controls option under the dynamic reconfiguration settings (to dynamically change equalization values, also enable the Enable equalizer settings option).

- The output signal reconfig\_fromgxb is transceiver-block based so the number of bits for this instance is one since the number of channels is one. The input signal reconfig\_togxb is a fixed width of three bits.

- Set the option What is the starting channel number? to 0.

#### Instantiating Five Times Using the Above 1-Channel ALT2GXB:

- Instantiate the *ALT2GXB.v* file or the symbol file five times.

- Note that after instantiating five times, add the **starting channel number** parameter to the symbol file. Change the parameter option to **4**, **8**, **12**, and **16** for the instances 2, 3, 4, and 5 just created.

- If the instantiations are done in a verilog file, use the following command to force the parameter option to **4**, **8**, **12**, and **16** for the instances 2, 3, 4, and 5:

```

defparam inst2. starting_channel_number= 4;

defparam inst3. starting channel number= 8;

```

#### **Dynamic Reconfiguration Controller Instance:**

- Launch the ALT2GXB\_RECONFIG MegaWizard.

- Set the What is the number of channels controlled by the controller? option to 20 so that five interface signals are enabled (reconfig\_fromgxb[4:0]).

- Select the necessary analog control signals to write in and read out from the V<sub>OD</sub>, pre-emphasis, equalization, and DC gain options.

## ALT2GXB Instances and ALT2GXB\_RECONFIG Instance Connections:

- Connect the reconfig\_fromgxb signal from the ALT2GXB instance to the same signal in the ALT2GXB RECONFIG instance.

- Connect the reconfig\_togxb signal from the ALT2GXB\_RECONFIG instance to the same signal in the ALT2GXB instance.

## Channel and PMA Controls Reconfiguration

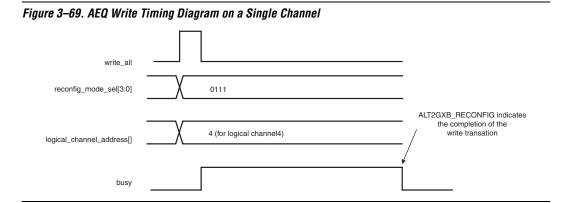

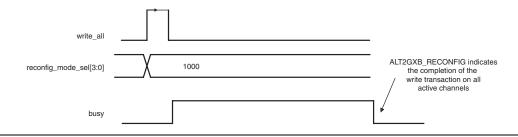

The write transaction of the controller is initiated on the assertion of the write\_all signal. In PMA reconfiguration mode, the write\_all signal writes the current state of all the selected input signals into the ALT2GXB instance channels. The write transaction involves the following sequence:

- 1. Read the control analog registers (read before write).

- 2. Write the current state of input signals of all channels into control registers.

- 3. Update the output control signals (optional read control ports if any of the read control ports are enabled).

If you select the read control port, the data\_valid signal is enabled. Reading and updating all the output control signals is part of the write transaction. Therefore, the data\_valid signal is asserted only when the write transaction is finished (busy signal is low) and all the output control ports are updated with the new data. When a write transaction is initiated and a set of values for the selected analog settings is being written, you cannot change the input values of the control ports until the transaction is completed. Otherwise, the results are unpredictable. The dynamic reconfiguration controller asserts the busy signal when you initiate a read or write transaction and is deasserted after the operation is complete.

Simultaneous write and read transactions are not allowed.

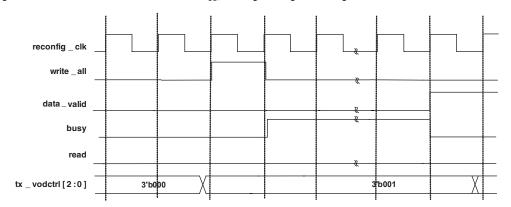

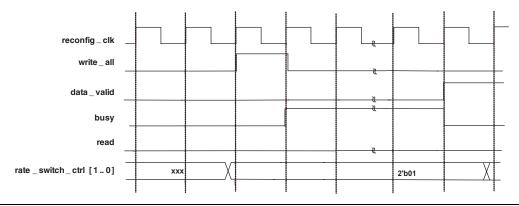

Figure 3–5 illustrates a write transaction for a transmit analog setting  $V_{\rm OD}$  (tx\_vod). The waveform shows a typical write transaction initiated by the pulsing of the write\_all signal and also shows the behavior of the status signals busy and data\_valid. Set the reconfig\_mode\_sel signal to 000 to reconfigure the analog settings of a transceiver channel.

Figure 3–5. Write Transaction Waveform -  $V_{00}$ , Analog Settings Reconfiguration

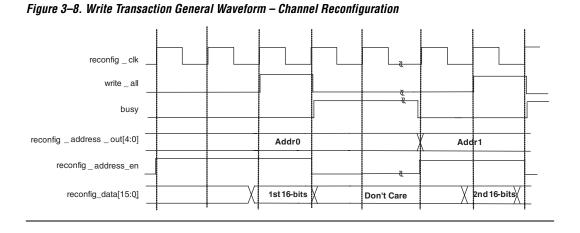

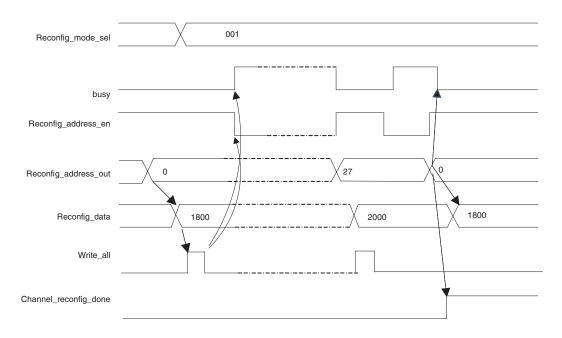

In channel reconfiguration, only a write transaction can occur—no read transactions are allowed. Set the reconfig\_mode\_sel control signal to 001 to use the channel reconfiguration feature. When you use this feature, the dynamic reconfiguration controller requires that you provide a 16-bit word (reconfig\_data[15:0]) on every write transaction, using the write\_all signal. This 16-bit word is part of a Memory Initialization File (.mif, also known as MIF) that is generated by the Quartus II software when an ALT2GXB instance is compiled. Refer to "Channel Reconfiguration" on page 3–30 for more information about the MIF.

The dynamic reconfiguration controller ignores a new 16-bit word if the previously initiated write transaction is not complete. As explained above, an on-going or active write transaction is signified by the busy signal. You can only input a new word of 16-bits when the busy signal is de-asserted.

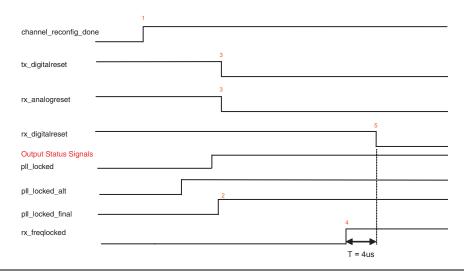

To properly initiate and complete a write transaction during channel reconfiguration, the dynamic reconfiguration controller provides additional signals. These signals are listed below and are classified into control and status signals.

The following are control signals (other than the write\_all and reconfig mode sel signals):

- logical\_channel\_address[7:0]: Use this control signal to set the logical channel number of the channel that is being reconfigured by the dynamic reconfiguration controller. This signal gets enabled when the number of channels controlled by the dynamic reconfiguration controller is more than one. Since the channel reconfiguration is done on a per-channel basis, you have to use this signal and provide the necessary logical channel address to write the MIF words so that a successful channel reconfiguration is achieved for that channel.

- reset\_reconfig\_address: Use this optional control signal to reset the reconfig\_address\_out value to 0. This reset control signal is only applicable in channel reconfiguration.

The following are status signals (other than the busy signal):

- reconfig\_address\_en: This is an optional output signal. The ALT2GXB\_RECONFIG asserts this signal to indicate the change in value on the reconfig\_address\_out port. This signal only gets asserted after the dynamic reconfiguration controller completes writing the 16-bit data.

- reconfig\_address\_out [4:0]: This is an optional output signal. It provides the address value that you can use to read the appropriate word from the MIF. Use the value in this port in combination with the reconfig\_address\_en signal to decide when to initiate a new write transaction.

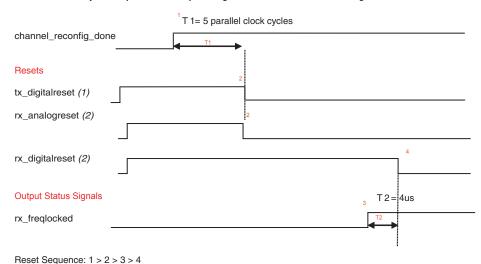

- channel\_reconfig\_done: This signal is available when you select the Channel Reconfiguration option in the dynamic reconfiguration controller. This port indicates that the ALT2GXB\_RECONFIG megafunction has finished writing all the words of a MIF in a sequence. This signal is very useful for user logic to implement reset recommendations during and after dynamic reconfiguration. Refer to "Reset Recommendations" on page 3–66 for more information about using this signal.

- Error: The ALT2GXB\_RECONFIG provides this status signal when you select the Enable illegal mode checking option or the Enable self recovery option in the Error checks/data rate switch tab. The conditions under which the error signal is asserted, when the above two options are enabled, are:

- Enable illegal mode checking option—when you select this

option, the dynamic reconfiguration controller checks whether

an attempted operation falls under one of the seven conditions

listed below. The dynamic reconfiguration controller detects

these conditions within two reconfig\_clk cycles, de-asserts

the busy signal, and asserts the error signal for two

reconfig\_clk cycles.

#### 1. PMA controls - read operation:

- None of the analog PMA read output ports

(rx\_eqctrl\_out, rx\_eqdcgain\_out,

tx\_vodctrl\_out, tx\_preemp\_0t\_out,

tx\_preemp\_1t\_out, and tx\_preemp\_2t\_out) are

selected in the ALT2GXB\_RECONFIG MegaWizard

- reconfig mode sel is set to 0

- read signal is asserted

#### 2. PMA controls - write operation:

- None of the analog PMA control write input ports

(rx\_eqctrl, rx\_eqdcgain, tx\_vodctrl,

tx\_preemp\_0t, tx\_preemp\_1t, and tx\_preemp\_2t)

are selected

- reconfig mode sel is set to 0

- write all signal is asserted

#### 3. Channel and/or TX PLL reconfiguration - read operation:

- reconfig mode sel input port is set to 1, 4, 5, or 6

- read signal is asserted

#### 4. Data rate switch - write operation with unsupported value:

- The rate switch ctrl[1:0] input port is set to 11

- reconfig\_mode\_sel input port is set to 4 (if other reconfiguration mode options are selected in the Reconfiguration settings tab)

- write all is asserted

#### 5. Data rate switch - write operation without input port:

- The rate switch ctrl input port is not used

- reconfig\_mode\_sel port is set to 4 (if other reconfiguration mode options are selected in the Reconfiguration settings tab)

- write all is asserted

#### 6. Data rate switch - read operation without output port:

- The rate switch out output port is not used

- reconfig\_mode\_sel port is set to 4 (if other reconfiguration mode options are selected in the Reconfiguration settings tab)

- read is asserted

#### 7. Adaptive Equalization - read operation:

- reconfig mode sel input port is set to 7, 8, 9, or 10

- read signal is asserted

- Enable self recovery option—When this option is selected, the dynamic reconfiguration controller waits for a pre-defined number of reconfig\_clk cycles based on the operation selected. If the busy signal does not go low within the pre-defined number of clock cycles, it asserts the error signal for two reconfig\_clk cycles.

## Example for Using Logical Channel Address to Perform Channel Reconfiguration

The dynamic reconfiguration controller provides an output port called logical\_channel\_address. This port is required for the channel reconfiguration and Channel and CMU PLL reconfiguration features to specify the logical transceiver channel that is to be reconfigured. The logical\_channel\_address value depends on how the ALT2GXB is instantiated in the design. In this section, the different ways of setting up the ALT2GXB instantiation and the corresponding logical channel address values for these transceiver channels are

shown.

#### Example 1:

Consider a design example in which the ALT2GXB instantiation has six transceiver channels:

- In the ALT2GXB MegaWizard (in the **RECONFIG** tab) set the starting channel number option to **0**.

- In the ALT2GXB\_RECONFIG MegaWizard, set the Number of channels controlled by the reconfig controller option to 6.

- The logical\_channel\_address value for channel 0 is 0 (Channel 0 is the one that is assigned to tx\_dataout [0]). Similarly, the logical\_channel\_address values for channels 1 through 5 are 1 through 5, respectively.

#### Example 2:

Consider a design example with ALT2GXB instance an that has one transceiver channel (assume the instantiation name is **instantiation0**). The **starting channel number** option value for this channel is **0**. If you use this instantiation to create five additional transceiver channels, you will need the following **defparam** parameter settings (for Verilog designs) to change the starting channel number for the stamped instantiations:

```

defparam <instantiation1>. starting_channel_number = 4

defparam <instantiation2>. starting_channel_number = 8

defparam <instantiation3>. starting_channel_number = 12

defparam <instantiation4>. starting_channel_number = 16

defparam <instantiation5>. starting_channel_number = 20

```

Therefore, the **starting channel number** option values for channels 0 through 5 are **0**, **4**, **8**, **12**, **16**, and **20**, respectively.

- In the ALT2GXB\_RECONFIG MegaWizard, set the Number of channels controlled by the reconfig controller option to 24. By setting this option, you get the reconfig\_fromgxb port with a bus width of 6.

- Connect the reconfig\_fromgxb(0 to 5) port of the ALT2GXB\_RECONFIG instantiation to the reconfig\_fromgxb ports of transceiver channels 0 to 5, respectively (as shown in Figure 3-6).

- The logical\_channel\_address values for transceiver channels 0 through 5 (tx\_dataout [0] to tx\_dataout [5]) are 0, 4, 8, 12, 16, and 20, respectively.

The logical\_channel\_address value depends on the starting channel number option value that you set in the ALT2GXB MegaWizard for the transceiver channel. However, it does not depend on the physical placements of the transceiver channel. For example, you can physically assign tx\_dataout [1] (tx\_dataout of instantiation1) in the same transceiver block or in the other transceiver block. For both these assignments, the logical\_channel\_address value is 4 for instantiation1.

Figure 3–6. Multiple Stampings of a Single Channel ALT2GXB Instantiation

#### Example 3:

Consider a design example with ALT2GXB instance an that has two transceiver channels (assume the example name is **instantiation0**). The **starting channel number** option for this instance is set to **0**. If you want to create six transceiver channels, stamp this instance three times. Modify the **starting channel number** option for the other two instances to **4** and **8** using the **defparam** setting (for verilog design):

defparam <instantiation1>. starting\_channel\_number = 4

defparam <instantiation2>. starting\_channel\_number = 8

- In the ALT2GXB\_RECONFIG MegaWizard, set the **Number of channels controlled by the reconfig controller** option to 12.

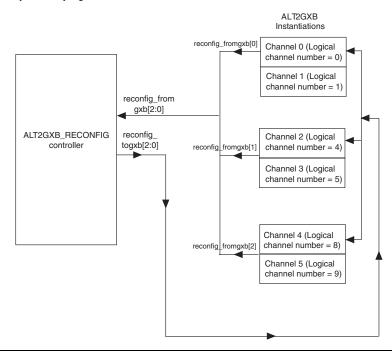

- Connect the reconfig\_fromgxb(0 to 2) port of the ALT2GXB\_RECONFIG instantiation to the reconfig\_fromgxb ports of instantiation0 to instantiation2, respectively (as shown in Figure 3–7).

- In this case, the logical\_channel\_address values for transceiver channels 0 and 1 (tx\_dataout [0] and tx\_dataout [1]) are 0 and 1. Similarly, the logical\_channel\_address values for channels 2 to 5 are 4, 5, 8, and 9, respectively. (The starting channel number option value for instantiation1 is 4. Therefore, the logical\_channel\_address value for channel 2 is 4).

Figure 3-7. Multiple Stampings of a Two Channel ALT2GXB Instantiation

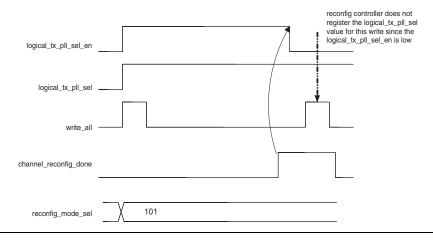

Figure 3–8 illustrates the write transaction for channel reconfiguration.

3–28

Stratix II GX Device Handbook, Volume 2

A write is allowed in dynamic transmit rate switch mode. The control signal rate\_switch\_ctrl [1:0] determines which division factor is written into the ALT2GXB transmitter (Figure 3–9).

Figure 3–9. Write Transaction General Waveform – Dynamic Transmit Rate Switch Reconfiguration (Division 2)

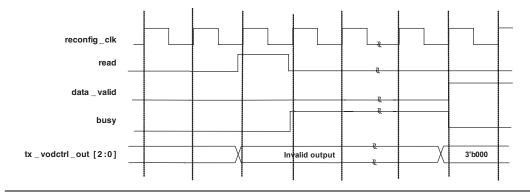

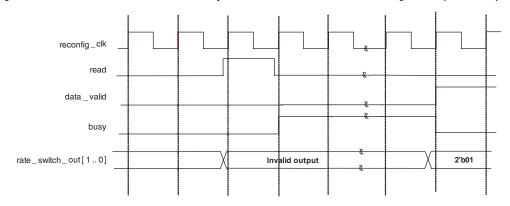

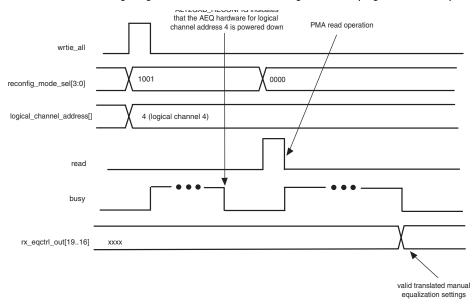

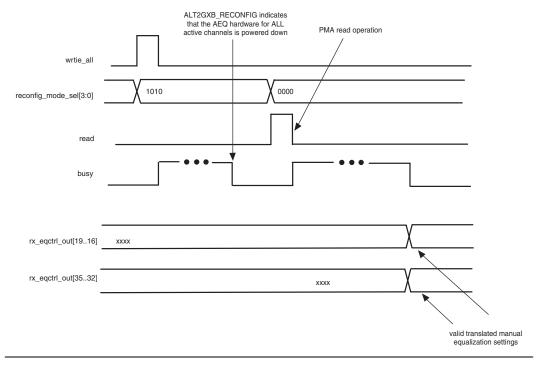

To initiate a read transaction, assert the read signal. The data on the output control ports is not valid until the data\_valid signal is high. The data\_valid signal goes high when the entire selected output signals have valid read values. Both read and write transactions are based on the reconfig\_clk and are edge triggered. Assert the write\_all and read signal for one reconfig\_clk cycle.

Figure 3–10. Read Transaction Waveform –  $V_{OD}$ , Analog Settings Reconfiguration

Figure 3-11. Read Transaction Waveform - Dynamic Transmit Rate Switch Reconfiguration (Division 2)

In addition to the PMA reconfiguration, the Quartus II software (version 6.1 and later) dynamic reconfiguration controller enables these two features:

- Channel Reconfiguration

- Dynamic Transmit Rate Switch

The following two sections explain these features.

#### **Channel Reconfiguration**

#### Introduction

Channel reconfiguration provides you the flexibility to reconfigure a channel by writing a new set of legal register bits into the ALT2GXB by the dynamic reconfiguration controller. With this feature you can either reconfigure the data rate of a channel or functional mode (including Basic mode with the custom mode enumeration [CME] features), or a mix of data rates and functional modes. The CME features are additional transceiver features introduced in Basic functional mode. Some of the CME features are controlled by PLD signals that allow you to dynamically control certain features in real time. However, some of the CME features are static and set through the Quartus II ALT2GXB configuration.

Channel reconfiguration only affects the channel involved in the reconfiguration; other channels are not affected.

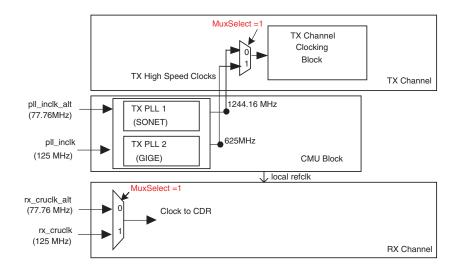

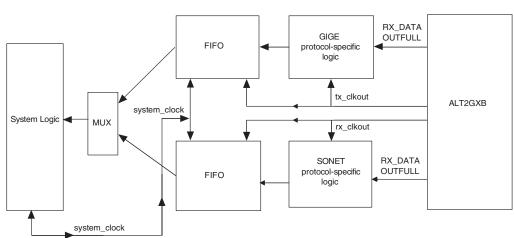

Channel reconfiguration can be classified into two major areas—data rate reconfiguration and functional mode reconfiguration:

- Data Rate Reconfiguration—Data rate reconfiguration involves switching the data rate of a channel by switching between two TX PLLs and reconfiguring the RX PLLs. The two TX PLLs can be set to different base rates. With data rate reconfiguration, you can also switch the data rate using local clock dividers present in the transmit and receive sides of every transceiver channel. You can reconfigure these clock dividers to 1, 2, and 4. When you reconfigure the clock dividers, ensure that the functional mode supports the minimum and maximum data rate.

- Functional Mode Reconfiguration—this can be:

- switched between one protocol functional mode to another protocol functional mode

- switched between a protocol functional mode to a Basic functional mode

- switched between a Basic mode to another Basic mode

There is no limit to the number of mode switches in channel reconfiguration, assuming transceiver and core clocking supports the transition.

Channel reconfiguration supports the following configurations of the physical transceiver channel:

- Duplex Channels (TX and RX)

- TX Only

- RX Only

- Independent TX/Independent RX in one physical channel

For the following discussion, the reference of a channel is a duplex channel, unless mentioned as TX-only or RX-only.

#### Design Flow

The Quartus II software provides a design flow called user memory initialization file (.mif, also known as MIF) flow to use the channel reconfiguration feature. This design flow involves writing the entire contents of the MIF for a channel. The Quartus II software generates the MIFs when you provide appropriate project settings (discussed below) and then compile an ALT2GXB instance. Each MIF has the settings for a full-duplex transceiver channel. The settings are all legal register settings of the transceiver channel. The ALT2GXB\_RECONFIG instance reads the value in the MIF using the reconfig\_data[15..0] port for every write transaction.

Each MIF contains twenty-eight 16-bit words if you enable the settings shown below.

For the Channel and CMU PLL Reconfiguration feature, the Quartus II software provides new settings that generates a MIF file with 38 words. This is discussed in "Quartus II Settings and Requirements" on page 3–111.

The Quartus II software creates the MIF under the <**Project\_DIR>/reconfig\_mif** folder. The file name is based on the design name and the rx\_ and tx\_ pin names. For example: **reconfig\_datarate\_1Gto2G\_pin\_af1\_pin\_af4.mif** (the Quartus II software automatically generates file name). You can change the MIF name. One design can have multiple MIFs (no limit) and one MIF can be used to reconfigure multiple channels. These MIFs can be stored in on-chip or off-chip memory.

If you do not specify pins for the tx\_dataout and rx\_datain for the transceiver channel, the Quartus II software selects a channel and generates a MIF for that channel. However, the MIF can still be used for any transceiver channel.

#### MIF Generation in Quartus II Software

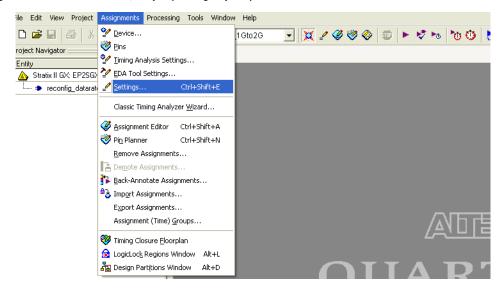

The MIF is not generated by default in a Quartus II compilation. There are three steps to enable MIF generation. Once the Quartus II software settings are enabled, a MIF is generated after you compile an ALT2GXB instance. The three steps to enable MIF generation are shown below.

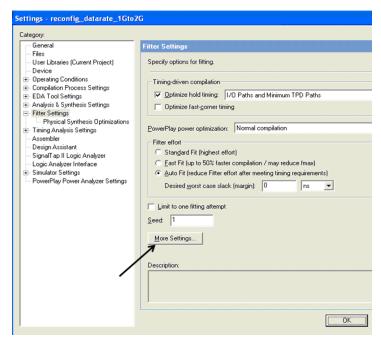

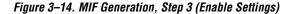

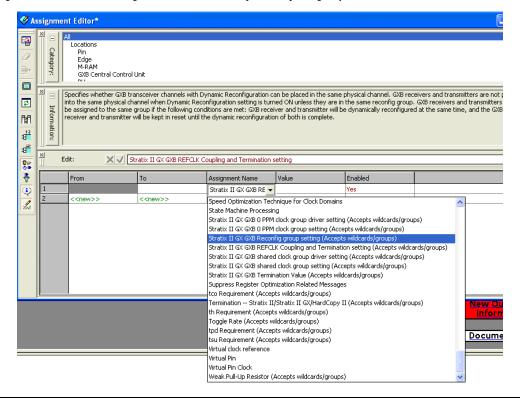

1. On the Assignments menu, select **Settings** (Figure 3–12).

Figure 3-12. MIF Generation, Step 1 (Settings Option)

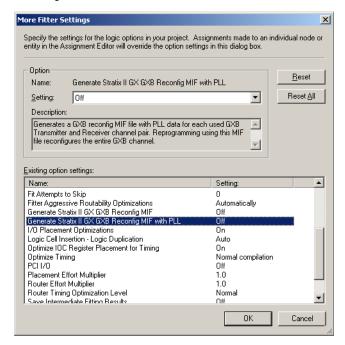

2. Select **Fitter settings**, then choose **More Settings** (Figure 3–13).

3. In the Option box of the **More Fitter Settings** page, set the **Generate Stratix II GX GXB reconfig MIF** option to **On** c (Figure 3–14).

The MIF is generated in the Assembler stage of the compilation process. However, for any change in the design or the above settings, the Quartus II software runs through the fitter stage before starting the assembler stage.

As previously discussed, the channel reconfiguration can be a data rate reconfiguration using two TX PLLs and local clock dividers, or a functional mode reconfiguration, or both. To reconfigure a channel successfully, select the appropriate options in the ALT2GXB MegaWizard (discussed in the sections below).

#### **ALT2GXB Configuration Related to Channel Reconfiguration**

You must setup the following two system design aspects in a ALT2GXB MegaWizard instance:

- Transceiver and Core Clocking

- PLD Data Path Interface

#### Transceiver and Core Clocking

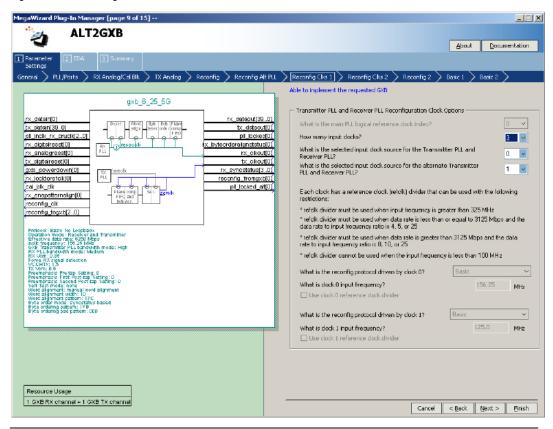

You must set up the core clocking and transceiver clocking options as part of channel reconfiguration for functional mode switchover or data rate transition. Transceiver clocking covers all the clock options you need to set up:

- Two TX PLLs for data rates and functional modes

- Input reference clocks for transmit and receive

- Internal clock MUX reference index setups

Core clocking covers the PLD interface clocking. PLD interface clocking is related to the parallel transmit and receive clocks (tx\_clkout and rx\_clkout). These clocks are used to parallel transmit data into and parallel receive data out of the transceiver. Core clocking is needed in any channel reconfiguration. Core clock assignments (clock grouping assignment and 0 PPM assignments) will override the core clocking set in the ALT2GXB instance. The details related to transceiver and core clocking are discussed in the following section. Transceiver and core clocking are classified as:

- Data rate switch using local clock block dividers

- Data rate switch based on clock frequencies of two PLLs in the transceiver block

#### **Data Rate Switch Using Local Clock Block Dividers**

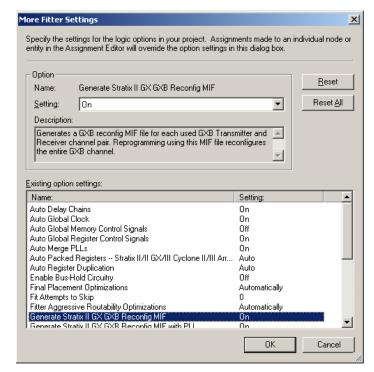

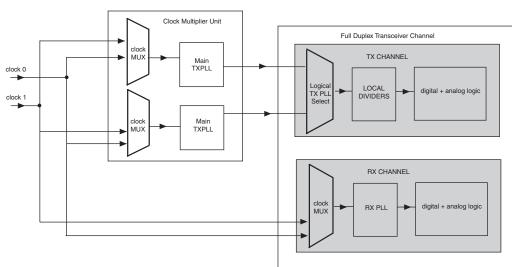

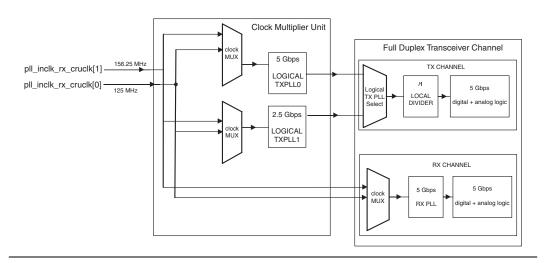

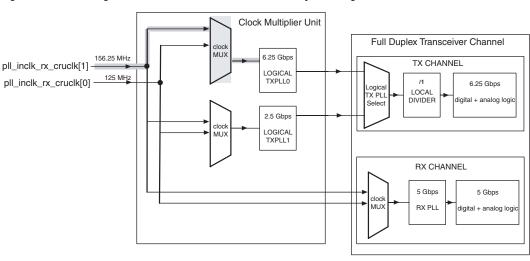

If you intend to switch the data rate in multiples of 1, 2, and 4 of the base data rate, use the local clock dividers. Local clock dividers further divide the TX PLL base rate and are present in transmit and receive block of every transceiver channel (refer to Figure 3–15).

Figure 3-15. Transmit Local Clock Divider Block

Transmit local clock dividers are placed after the CMU PLLs and thus the TX PLLs are not affected during a data rate switch using local clock dividers.

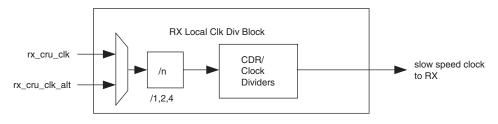

Receive local clock dividers are placed before the RX PLL (CDR). Thus the RX PLL is affected every time the data rate switch using local clock dividers occurs. The Quartus II software data rate division factor chooses a combination of local clock dividers and feedback dividers present in the CDR that yields the best performance (refer to Figure 3–16).

Figure 3-16. Receive Local Clock Divider Block

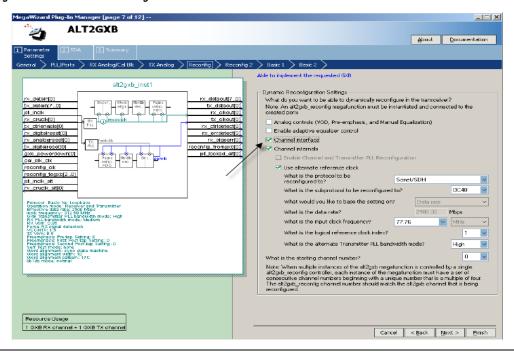

To configure the local divider using the same TX PLL base setting, use the following steps:

- 1. Set the base setting on the CMU PLL (use the fastest data rate that is intended to be reconfigured to).

- 2. Set the local clock divider setting (use the effective data rate for that configuration).

- 3. Enable either the **Channel Internals** or **Channel Interface** option (refer to "Channel Internals" on page 3–53 and "Channel Interface" on page 3–53 for more information).

- Setup core clocking (refer to "Transmitter Core Clocking" on page 3–45 and "Receiver Core Clocking" on page 3–48 for more information).

- 5. Finish the ALT2GXB configuration.

- 6. Repeat the previous 5 steps with the same TX PLL base setting and different local clock divider settings.

- 7. Group core clocking.

- Lock down the pin assignments for the clocks and generate the MIFs for above instances.

Steps 1 and 2 are the only steps related to the local clock divider settings. Step 4 is a mandatory step and is an important part of clocking in every channel reconfiguration (refer to Figure 3–17).

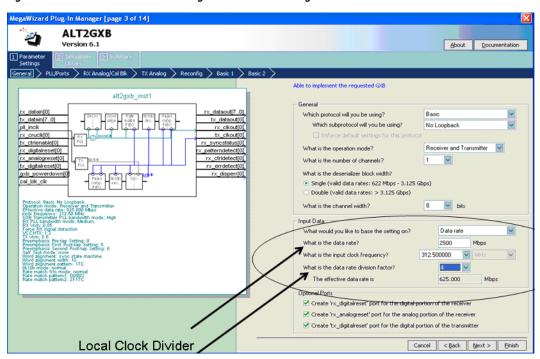

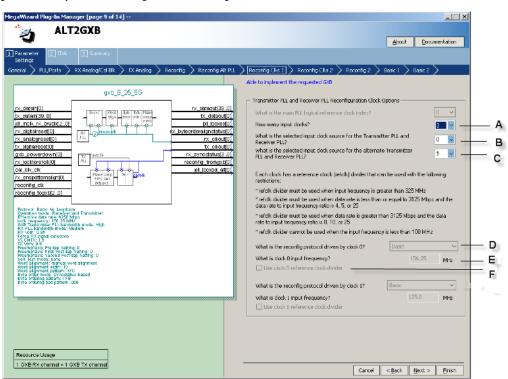

gaWizard Plug-In Manager [page 3 of 14] ALT2GXB Version 6.1 About Documentation Able to implement the requested GXB alt2gxb\_inst1 rx\_dataout[7..0] rx\_datain[0] Which protocol will you be using? Which subprotocol will you be using? No Loopback pll\_inclk rx\_clkout[0] tx\_ctrlenable[0] rx\_syncstatus[0] What is the operation mode?

What is the number of channels? Receiver and Transmitter 1 🔻 tx\_digitalreset[0] What is the deserializer block width? • Single (valid data rates: 622 Mbps - 3.125 Gbps) O Double (valid data rates: > 3.125 Gbps) What is the channel width? What would you like to base the setting on? Data rate 2500 What is the input clock frequency? 312.500000 What is the data rate division factor? 1 The effective data rate is 2500.000 Mbps Optional Ports Create 'rx\_digitalreset' port for the digital portion of the receive Create 'rx analogreset' port for the analog portion of the receiver ✓ Create 'tx\_digitalreset' port for the digital portion of the transmitter Local Clock Divider for TX and RX Cancel < Back Next > Einish

Figure 3-17. ALT2GXB Instance—TX/RX Local Clock Divider

#### Data Rate Switch Based on Clock Frequencies of Two PLLs

If your application requires the transceiver to switch between multiple data rates, you can use channel reconfiguration to switch between the two TX PLLs in the transceiver block. The following sections explain how to setup two PLLs and achieve multiple data rates using channel reconfiguration:

- 1. Set the primary PLL (mode1) data rate setting.

- 2. Set the local clock divider (if needed).

- 3. Enable the **Channel Internals** option in the dynamic reconfiguration section of the ALT2GXB (refer to "Channel Internals" on page 3–53 for more information).

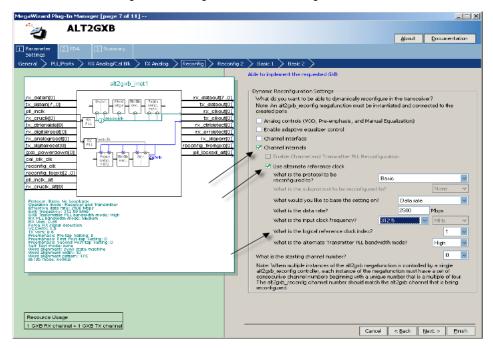

- 4. In Channel Internals option, enable the use alternate reference clock (Mode 2) option.

- Set all the parameters related to alternate PLL protocols, data rates, bandwidth, and clock frequency.

- 5. Set the **what is the logical reference index?** option (refer to the Logical Reference Index).

- 6. Set the core clocking options—transmit and receive

- This is a mandatory step for every channel reconfiguration that uses tx\_clkout and rx\_clkout (refer to "Transmitter Core Clocking" on page 3–45).

- 7. If there are no other settings to configure in the ALT2GXB, select finish the ALT2GXB instantiation.