# 12. IEEE 1149.1 (JTAG) Boundary-Scan Testing for the Cyclone III Device Family

#### CIII51014-2.3

This chapter provides guidelines on using the IEEE Std. 1149.1 boundary-scan test (BST) circuitry in Cyclone<sup>®</sup> III device family (Cyclone III and Cyclone III LS devices). BST architecture tests pin connections without using physical test probes, and captures functional data while a device is operating normally. Boundary-scan cells (BSCs) in a device can force signals onto pins or capture data from pin or logic array signals. Forced test data is serially shifted into the boundary-scan cells. Captured data is serially shifted out and externally compared to expected results.

This chapter contains the following sections:

- "IEEE Std. 1149.1 BST Architecture" on page 12–1

- "IEEE Std. 1149.1 BST Operation Control" on page 12–2

- "I/O Voltage Support in a JTAG Chain" on page 12–5

- "Guidelines for IEEE Std. 1149.1 BST" on page 12–6

- "Boundary-Scan Description Language Support" on page 12–7

### IEEE Std. 1149.1 BST Architecture

Cyclone III device family operating in the IEEE Std. 1149.1 BST mode use four required pins:

- TDI

- TD0

- TMS

- TCK

The TCK pin has an internal weak pull-down resistor, while the TDI and TMS pins have weak internal pull-up resistors. The TDO output pin and all the JTAG input pins are powered by the  $V_{CCIO}$  supply of bank 1A. All user I/O pins are tri-stated during JTAG configuration.

For recommendations on how to connect a JTAG chain with multiple voltages across the devices in the chain, refer to "I/O Voltage Support in a JTAG Chain" on page 12–5.

• For more information about the description and functionality of all JTAG pins, registers used by the IEEE Std. 1149.1 BST circuitry, and the test access port (TAP) controller, refer to *AN39: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices*.

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **IEEE Std. 1149.1 BST Operation Control**

Table 12–1 lists the boundary-scan register length for devices in Cyclone III device family.

| Family         | Device    | Boundary-Scan Register<br>Length |

|----------------|-----------|----------------------------------|

| Cyclone III    | EP3C5     | 603                              |

|                | EP3C10    | 603                              |

|                | EP3C16    | 1,080                            |

|                | EP3C25    | 732                              |

|                | EP3C40    | 1,632                            |

|                | EP3C55    | 1,164                            |

|                | EP3C80    | 1,314                            |

|                | EP3C120   | 1,620                            |

| Cyclone III LS | EP3CLS70  | 1,314                            |

|                | EP3CLS100 | 1,314                            |

|                | EP3CLS150 | 1,314                            |

|                | EP3CLS200 | 1,314                            |

Table 12–1. Boundary-Scan Register Length for Cyclone III Device Family

Table 12–2 lists the IDCODE information for devices in Cyclone III device family.

| Table 12-2. | Device | <b>IDCODE</b> | for Cyclone | e III Device Family | I |

|-------------|--------|---------------|-------------|---------------------|---|

|-------------|--------|---------------|-------------|---------------------|---|

| Family         | Device    | IDCODE (32 Bits) <sup>(1)</sup> |                       |                                    |                            |  |

|----------------|-----------|---------------------------------|-----------------------|------------------------------------|----------------------------|--|

|                |           | Version (4 Bits)                | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) <sup>(2)</sup> |  |

|                | EP3C5     | 0000                            | 0010 0000 1111 0001   | 000 0110 1110                      | 1                          |  |

| Cyclone III    | EP3C10    | 0000                            | 0010 0000 1111 0001   | 000 0110 1110                      | 1                          |  |

|                | EP3C16    | 0000                            | 0010 0000 1111 0010   | 000 0110 1110                      | 1                          |  |

|                | EP3C25    | 0000                            | 0010 0000 1111 0011   | 000 0110 1110                      | 1                          |  |

|                | EP3C40    | 0000                            | 0010 0000 1111 0100   | 000 0110 1110                      | 1                          |  |

|                | EP3C55    | 0000                            | 0010 0000 1111 0101   | 000 0110 1110                      | 1                          |  |

|                | EP3C80    | 0000                            | 0010 0000 1111 0110   | 000 0110 1110                      | 1                          |  |

|                | EP3C120   | 0000                            | 0010 0000 1111 0111   | 000 0110 1110                      | 1                          |  |

| Cyclone III LS | EP3CLS70  | 0000                            | 0010 0111 0000 0001   | 000 0110 1110                      | 1                          |  |

|                | EP3CLS100 | 0000                            | 0010 0111 0000 0000   | 000 0110 1110                      | 1                          |  |

|                | EP3CLS150 | 0000                            | 0010 0111 0000 0011   | 000 0110 1110                      | 1                          |  |

|                | EP3CLS200 | 0000                            | 0010 0111 0000 0010   | 000 0110 1110                      | 1                          |  |

### Notes to Table 12-2:

(1) The MSB is on the left.

(2) The LSB of the IDCODE is always 1.

Cyclone III device family supports the IEEE Std. 1149.1 (JTAG) instructions as listed in Table 12–3.

| JTAG Instruction        | Instruction Code | Description                                                                                                                                                                                                                                                                                                        |

|-------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD          | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap <sup>®</sup> II embedded logic analyzer.                                                               |

| EXTEST (1)              | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested<br>by forcing a test pattern at the output pins and capturing test results at<br>the input pins.                                                                                                                                          |

| BYPASS                  | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                        |

| USERCODE                | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                          |

| IDCODE                  | 00 000 0110      | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO. IDCODE is the default instruction at power up and in TAP RESET state.                                                                                                                        |

| HIGHZ                   | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                 |

| CLAMP                   | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary scan register.                                    |

| ICR Instructions        | _                | Used when configuring Cyclone III device family using the JTAG port<br>with a USB-Blaster <sup>™</sup> ByteBlaster <sup>™</sup> II, MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup><br>download cable, or when using a Jam File, or JBC File via an embedded<br>processor.                                |

| PULSE_NCONFIG           | 00 0000 0001     | Emulates pulsing the $n_{CONFIG}$ pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                   |

| CONFIG_IO (2)           | 00 0000 1101     | Allows I/O reconfiguration through JTAG ports using the IOCSR for JTAG testing. This is executed after or during configurations. nSTATUS pin must go high before you can issue the CONFIG_IO instruction.                                                                                                          |

| EN_ACTIVE_CLK (2)       | 01 1110 1110     | Allows CLKUSR pin signal to replace the internal oscillator as the configuration clock source.                                                                                                                                                                                                                     |

| DIS_ACTIVE_CLK (2)      | 10 1110 1110     | Allows you to revert the configuration clock source from CLKUSR pin signal set by EN_ACTIVE_CLK back to the internal oscillator.                                                                                                                                                                                   |

| ACTIVE_DISENGAGE (2)    | 10 1101 0000     | Places the active configuration mode controllers into idle state prior to CONFIG_IO to configure the IOCSR or perform board level testing.                                                                                                                                                                         |

| ACTIVE_ENGAGE (2)       | 10 1011 0000     | This instruction might be used in AS and AP configuration schemes to re-engage the active controller.                                                                                                                                                                                                              |

| APFC_BOOT_ADDR (2), (3) | 10 0111 0000     | Places the 22-bit active boot address register between the TDI and TDO pins, allowing a new active boot address to be serially shifted into TDI and into the active parallel (AP) flash controller. In remote system upgrade, the $PFC_BOOT_ADDR$ instruction sets the boot address for the factory configuration. |

| JTAG Instruction            | Instruction Code | Description                                                                                                                                                                                                                                                                                          |

|-----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FACTORY (4)                 | 10 1000 0001     | Enables access to all other JTAG instructions (other than BYPASS,<br>SAMPLE/PRELOAD and EXTEST instructions, which are supported upon<br>power up). This instruction also clears the device configuration data<br>and advanced encryption standard (AES) volatile key.                               |

| KEY_PROG_VOL (4)            | 01 1010 1101     | Used to enter and store the security key into volatile registers. When this instruction is executed, TDI is connected to a 512-bit volatile key scan chain. TDO is not connected to the end of this scan chain.                                                                                      |

| KEY_CLR_VREG <sup>(4)</sup> | 00 0010 1001     | Clears the volatile verify register which signifies the validity of the volatile keys stored in the registers. You must clear the volatile verify register by issuing this command whenever you attempt to program a new volatile key. This instruction must be asserted for at least 10 TCK cycles. |

### Table 12–3. IEEE Std. 1149.1 (JTAG) Instructions Supported by Cyclone III Device Family (Part 2 of 2)

#### Notes to Table 12-3:

(1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

(2) For more information about how to use CONFIG\_IO, EN\_ACTIVE\_CLK, DIS\_ACTIVE\_CLK, ACTIVE\_DISENGAGE, ACTIVE\_ENGAGE and APFC\_BOOT\_ADDR instructions for Cyclone III device family, refer to the *Configuration, Design Security, and Remote System Upgrades in Cyclone III Devices* chapter.

(3) APFC\_BOOT\_ADDR instruction is not supported in Cyclone III LS devices.

(4) For Cyclone III LS devices only. For more information about how to program the security key into the volatile registers, refer to the *Configuration, Design Security, and Remote System Upgrades in Cyclone III Devices* chapter.

The IEEE Std. 1149.1 BST circuitry is enabled upon device power-up. You can perform BST on Cyclone III device family before, after, and during configuration. Cyclone III device family supports the BYPASS, IDCODE and SAMPLE instructions during configuration without interrupting configuration. To send all other JTAG instructions, interrupt the configuration using the CONFIG\_IO instruction except for active configuration schemes in which the ACTIVE\_DISENGAGE instruction is used instead.

The CONFIG\_IO instruction allows you to configure I/O buffers via the JTAG port, and when issued, interrupts configuration. This instruction allows you to perform board-level testing prior to configuring Cyclone III device family. Alternatively, you can wait for the configuration device to complete configuration. After configuration is interrupted and JTAG BST is complete, you must reconfigure the part via JTAG (PULSE\_NCONFIG instruction) or by pulsing nCONFIG low.

When you perform JTAG boundary-scan testing before configuration, the nCONFIG pin must be held low.

**For more information about the following topics, refer to** *AN39: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices:*

- TAP controller state-machine

- Timing requirements for IEEE Std. 1149.1 signals

- Instruction mode

- Mandatory JTAG instructions (SAMPLE/PRELOAD, EXTEST and BYPASS)

- Optional JTAG instructions (IDCODE, USERCODE, CLAMP and HIGHZ)

The following information is only applicable to Cyclone III LS devices:

- Only the three mandatory JTAG 1149.1 JTAG instructions (BYPASS, SAMPLE/PRELOAD, EXTEST) and the FACTORY private instruction are supported from the JTAG pins upon power up. The FACTORY instruction (instruction code: 10 1000 0001) must be issued before the device starts loading the core configuration data to enable access to all other JTAG instructions. This instruction also clears the device configuration data and AES volatile key.

- IDCODE instruction is not supported upon power-up, prior to issuing the FACTORY instruction. However, it is the default instruction when the TAP controller is in the reset state. Without loading any instructions, you can go to the Shift\_DR state and shift out the JTAG Device ID.

- IDCODE, CONFIG\_IO, ACTIVE\_DISENGAGE, HIGHZ, CLAMP, USERCODE and PULSE\_NCONFIG instructions are supported, provided that the FACTORY instruction is executed.

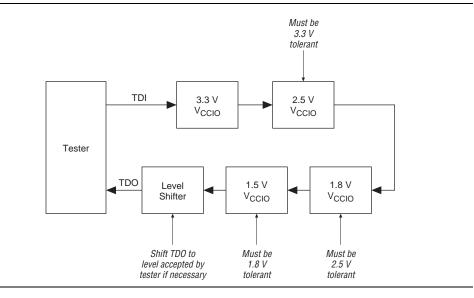

# I/O Voltage Support in a JTAG Chain

A JTAG chain can contain several different devices. However, you must be cautious if the chain contains devices that have different  $V_{CCIO}$  levels. The output voltage level of the TDO pin must meet the specifications of the TDI pin it drives. For Cyclone III device family, the TDO pin is powered by the  $V_{CCIO}$  power supply. Because the  $V_{CCIO}$  supply is 3.3 V, the TDO pin drives out 3.3 V.

Devices can interface with each other although they might have different  $V_{CCIO}$  levels. For example, a device with a 3.3-V TDO pin can drive to a device with a 5.0-V TDI pin because 3.3 V meets the minimum TTL-level  $V_{IH}$  for the 5.0-V TDI pin. JTAG pins on Cyclone III device family can support the input levels of  $V_{CCIO}$  of bank 1A.

For multiple devices in a JTAG chain with 3.0-V or 3.3-V I/O standard, you must connect a 25- $\Omega$  series resistor on a TDO pin driving a TDI pin.

You can also interface the TDI and TDO lines of the devices that have different  $V_{CCIO}$  levels by inserting a level shifter between the devices. If possible, the JTAG chain must be built in such a way that a device with a higher  $V_{CCIO}$  level drives to a device with an equal or lower  $V_{CCIO}$  level. This way, a level shifter may be required only to shift the TDO level to a level acceptable to the JTAG tester.

Figure 12–1 shows the JTAG chain of mixed voltages and how a level shifter is inserted in the chain.

## **Guidelines for IEEE Std. 1149.1 BST**

Use the following guidelines when performing BST with IEEE Std. 1149.1 devices:

- If the 10 bit checkerboard pattern (1010101010) does not shift out of the instruction register via the TDO pin during the first clock cycle of the SHIFT\_IR state, the TAP controller did not reach the proper state. To solve this problem, try one of the following procedures:

- Verify that the TAP controller has reached the SHIFT\_IR state correctly. To advance the TAP controller to the SHIFT\_IR state, return to the RESET state and send the code 01100 to the TMS pin.

- Check the connections to the VCC, GND, JTAG, and dedicated configuration pins on the device.

- Perform a SAMPLE/PRELOAD test cycle prior to the first EXTEST test cycle to ensure that known data is present at the device pins when you enter the EXTEST mode. If the OEJ update register contains a 0, the data in the OUTJ update register is driven out. The state must be known and correct to avoid contention with other devices in the system.

- Do not perform EXTEST testing during ICR. This instruction is supported before or after ICR, but not during ICR. Use the CONFIG\_IO instruction to interrupt configuration and then perform testing, or wait for configuration to complete.

- If testing is performed before configuration, hold the nCONFIG pin low.

You must not invoke the following private instructions at any instance because these instructions can potentially damage the device, rendering the device useless:

- 1000010000

- **100100000**

- 1011100000

## **Boundary-Scan Description Language Support**

The boundary-scan description language (BSDL), a subset of VHDL, provides a syntax that allows you to describe the features of an IEEE Std. 1149.1 BST-capable device that can be tested. To download BSDL files for IEEE Std. 1149.1-compliant Cyclone III device family, visit the Altera Download Center.

To perform BST on a configured device, a post configuration BSDL file that is customized to your design is required. Post configuration BSDL file generation with BSDL Customizer script (available on the Altera Download Center) is for Cyclone III devices only.

Use version 9.0 and later of the Quartus II software to create a post configuration BSDL file for Cyclone III LS devices.

• For information on the procedures to generate the generic and post configuration BSDL files with Quartus II software, visit the Altera Download Center.

### **Document Revision History**

Table 12–4 lists the revision history for this document.

| Date          | Version | Changes                                                                                                                                                                                                                                                                                          |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| December 2011 | 2.3     | <ul> <li>Updated "IEEE Std. 1149.1 BST Architecture" on page 12–1 and "I/O Voltage Support in a<br/>JTAG Chain" on page 12–5.</li> </ul>                                                                                                                                                         |  |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                                                                                                                                                                            |  |

| December 2009 | 2.2     | Minor changes to the text.                                                                                                                                                                                                                                                                       |  |

| July 2009     | 2.1     | Made minor correction to the part number.                                                                                                                                                                                                                                                        |  |

| June 2009     | 2.0     | <ul> <li>Updated "Introduction" on page 12–1, "IEEE Std. 1149.1 BST Architecture" on<br/>page 12–1, "IEEE Std. 1149.1 BST Operation Control" on page 12–2, "Guidelines for IEEE<br/>Std. 1149.1 BST" on page 12–6, and "Boundary-Scan Description Language Support" on<br/>page 12–7.</li> </ul> |  |

|               |         | <ul> <li>Updated Table 12–1 on page 12–2, Table 12–2 on page 12–2, and Table 12–3 on<br/>page 12–3.</li> </ul>                                                                                                                                                                                   |  |

| October 2008  | 1.3     | Updated chapter to new template.                                                                                                                                                                                                                                                                 |  |

| May 2008      | 1.2     | Minor textual changes.                                                                                                                                                                                                                                                                           |  |

Table 12-4. Document Revision History (Part 1 of 2)

BSDL files for IEEE std. 1149.1-compliant Cyclone III LS devices can also be generated using version 9.0 and later of the Quartus II software.

| Date       | Version | Changes                                                                                             |  |  |

|------------|---------|-----------------------------------------------------------------------------------------------------|--|--|

|            |         | <ul> <li>Updated "IEEE Std.1149.1 Boundary-Scan Register" section.</li> </ul>                       |  |  |

|            |         | <ul> <li>Updated IDCODE information and removed SignalTap II instructions in Table 12-4.</li> </ul> |  |  |

| July 2007  | 1.1     | <ul> <li>Updated "BST for Configured Devices" section.</li> </ul>                                   |  |  |

|            |         | Added a guideline to "Guidelines for IEEE Std. 1149.1 Boundary-Scan Testing" section.               |  |  |

|            |         | <ul> <li>Added chapter TOC and "Referenced Documents" section.</li> </ul>                           |  |  |

| March 2007 | 1.0     | Initial release.                                                                                    |  |  |

Table 12–4. Document Revision History (Part 2 of 2)