# 7. Configuring Stratix II and Stratix II GX Devices

SII52007-4.5

## Introduction

Stratix® II and Stratix II GX devices use SRAM cells to store configuration data. Because SRAM memory is volatile, configuration data must be downloaded to Stratix II and Stratix II GX devices each time the device powers up. Stratix II and Stratix II GX devices can be configured using one of five configuration schemes: the fast passive parallel (FPP), active serial (AS), passive serial (PS), passive parallel asynchronous (PPA), and Joint Test Action Group (JTAG) configuration schemes. All configuration schemes use either an external controller (for example, a MAX® II device or microprocessor) or a configuration device.

# **Configuration Devices**

The Altera enhanced configuration devices (EPC16, EPC8, and EPC4) support a single-device configuration solution for high-density devices and can be used in the FPP and PS configuration schemes. They are ISP-capable through its JTAG interface. The enhanced configuration devices are divided into two major blocks, the controller and the flash memory.

For information on enhanced configuration devices, refer to the *Enhanced Configuration Devices* (*EPC4*, *EPC8* & *EPC16*) *Data Sheet* in volume **2** of the *Configuration Handbook*.

The Altera serial configuration devices (EPCS64, EPCS16, and EPCS4) support a single-device configuration solution for Stratix II and Stratix II GX devices and are used in the AS configuration scheme. Serial configuration devices offer a low cost, low pin count configuration solution.

For information on serial configuration devices, refer to the *Serial Configuration Devices* (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Data Sheet chapter in volume 2 of the *Configuration Handbook*.

The EPC2 configuration devices provide configuration support for the PS configuration scheme. The EPC2 device is ISP-capable through its JTAG interface. The EPC2 device can be cascaded to hold large configuration files.

For more information on EPC2 configuration devices, refer to the *Configuration Devices for SRAM-Based LUT Devices Data Sheet* chapter in volume 2 of the *Configuration Handbook*.

The configuration scheme is selected by driving the Stratix II or Stratix II GX device MSEL pins either high or low as shown in Table 7–1. The MSEL pins are powered by the  $V_{CCIO}$  power supply of the bank they reside in. The MSEL [  $3\ldots 0$  ] pins have 9-k $\Omega$  internal pull-down resistors that are always active. During power-on reset (POR) and during reconfiguration, the MSEL pins have to be at LVTTL  $V_{IL}$  and  $V_{IH}$  levels to be considered a logic low and logic high.

To avoid any problems with detecting an incorrect configuration scheme, hard-wire the MSEL[] pins to  $V_{CCPD}$  and GND, without any pull-up or pull-down resistors. Do not drive the MSEL[] pins by a microprocessor or another device.

| Table 7–1. Stratix II and Stratix II GX Configuration Schemes (Part 1 of 2)                  |       |       |       |       |  |

|----------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Configuration Scheme                                                                         | MSEL3 | MSEL2 | MSEL1 | MSELO |  |

| Fast passive parallel (FPP)                                                                  | 0     | 0     | 0     | 0     |  |

| Passive parallel asynchronous (PPA)                                                          | 0     | 0     | 0     | 1     |  |

| Passive serial (PS)                                                                          | 0     | 0     | 1     | 0     |  |

| Remote system upgrade FPP (1)                                                                | 0     | 1     | 0     | 0     |  |

| Remote system upgrade PPA (1)                                                                | 0     | 1     | 0     | 1     |  |

| Remote system upgrade PS (1)                                                                 | 0     | 1     | 1     | 0     |  |

| Fast AS (40 MHz) (2)                                                                         | 1     | 0     | 0     | 0     |  |

| Remote system upgrade fast AS (40 MHz) (2)                                                   | 1     | 0     | 0     | 1     |  |

| FPP with decompression and/or design security feature enabled (3)                            | 1     | 0     | 1     | 1     |  |

| Remote system upgrade FPP with decompression and/or design security feature enabled (1), (3) | 1     | 1     | 0     | 0     |  |

| AS (20 MHz) (2)                                                                              | 1     | 1     | 0     | 1     |  |

| Remote system upgrade AS (20 MHz) (2)                                                        | 1     | 1     | 1     | 0     |  |

| JTAG-based configuration (5)                                                                 | (4)   | (4)   | (4)   | (4)   |  |

| Table 7–1. Stratix II and Stratix II GX Configuration Schemes (Part 2 of 2) |       |       |       |       |  |

|-----------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Configuration Scheme                                                        | MSEL3 | MSEL2 | MSEL1 | MSELO |  |

Notes to Table 7-1:

- (1) These schemes require that you drive the RUnlu pin to specify either remote update or local update. For more information about remote system upgrades in Stratix II devices, refer to the Remote System Upgrades With Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II Device Handbook or the Remote System Upgrades With Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook.

- (2) Only the EPCS16 and EPCS64 devices support up to a 40 MHz DCLK. Other EPCS devices support up to a 20 MHz DCLK. Refer to the *Serial Configuration Devices* (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Data Sheet for more information.

- (3) These modes are only supported when using a MAX II device or a microprocessor with flash memory for configuration. In these modes, the host system must output a DCLK that is 4× the data rate.

- (4) Do not leave the MSEL pins floating. Connect them to  $V_{CCPD}$  or ground. These pins support the non-JTAG configuration scheme used in production. If only JTAG configuration is used, you should connect the MSEL pins to ground.

- (5) JTAG-based configuration takes precedence over other configuration schemes, which means MSEL pin settings are ignored.

Stratix II and Stratix II GX devices offer design security, decompression, and remote system upgrade features. Design security using configuration bitstream encryption is available in Stratix II and Stratix II GX devices, which protects your designs. Stratix II and Stratix II GX devices can receive a compressed configuration bit stream and decompress this data in real-time, reducing storage requirements and configuration time. You can make real-time system upgrades from remote locations of your Stratix II and Stratix II GX designs with the remote system upgrade feature.

Table 7–2 and Table 7–3 show the uncompressed configuration file sizes for Stratix II and Stratix II GX devices, respectively.

| Table 7–2. Stratix II Uncompressed .rbf Sizes Notes (1), (2) |                    |       |  |  |  |  |

|--------------------------------------------------------------|--------------------|-------|--|--|--|--|

| Device                                                       | Data Size (MBytes) |       |  |  |  |  |

| EP2S15                                                       | 4,721,544          | 0.590 |  |  |  |  |

| EP2S30                                                       | 9,640,672          | 1.205 |  |  |  |  |

| EP2S60                                                       | 16,951,824         | 2.119 |  |  |  |  |

| EP2S90                                                       | 25,699,104         | 3.212 |  |  |  |  |

| EP2S130                                                      | 37,325,760         | 4.666 |  |  |  |  |

| EP2S180                                                      | 49,814,760         | 6.227 |  |  |  |  |

*Notes to Table 7–2:*

- (1) These values are final.

- (2) .rbf: Raw Binary File.

| Table 7–3. Stratix II GX Uncompressed .rbf Sizes Note (1) |                  |                    |  |  |  |  |

|-----------------------------------------------------------|------------------|--------------------|--|--|--|--|

| Device                                                    | Data Size (Bits) | Data Size (MBytes) |  |  |  |  |

| EP2SGX30C<br>EP2SGX30D                                    | 9,640,672        | 1.205              |  |  |  |  |

| EP2SGX60C<br>EP2SGX60D<br>EP2SGX60E                       | 16,951,824       | 2.119              |  |  |  |  |

| EP2SGX90E<br>EP2SGX90F                                    | 25,699,104       | 3.212              |  |  |  |  |

| EP2SGX130G                                                | 37,325,760       | 4.666              |  |  |  |  |

Note to Table 7-3:

(1) .rbf: Raw Binary File.

Use the data in Table 7–2 to estimate the file size before design compilation. Different configuration file formats, such as a Hexidecimal (.hex) or Tabular Text File (.ttf) format, will have different file sizes. However, for any specific version of the Quartus<sup>®</sup> II software, any design targeted for the same device will have the same uncompressed configuration file size. If you are using compression, the file size can vary after each compilation because the compression ratio is dependent on the design.

This chapter explains the Stratix II and Stratix II GX device configuration features and describes how to configure Stratix II and Stratix II GX devices using the supported configuration schemes. This chapter provides configuration pin descriptions and the Stratix II and Stratix II GX device configuration file formats. In this chapter, the generic term device(s) includes all Stratix II and Stratix II GX devices.

For more information on setting device configuration options or creating configuration files, refer to *Software Settings* in volume 2 of the *Configuration Handbook*.

# Configuration Features

Stratix II and Stratix II GX devices offer configuration data decompression to reduce configuration file storage, design security using data encryption to protect your designs, and remote system upgrades to allow for remotely updating your Stratix II and Stratix II GX designs. Table 7–4 summarizes which configuration features can be used in each configuration scheme.

| Configuration<br>Scheme | Configuration Method                                | Design Security | Decompression | Remote System<br>Upgrade |

|-------------------------|-----------------------------------------------------|-----------------|---------------|--------------------------|

| FPP                     | MAX II device or a Microprocessor with flash memory | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |

|                         | Enhanced Configuration Device                       |                 | <b>√</b> (2)  | ✓                        |

| AS                      | Serial Configuration Device                         | ✓               | ✓             | <b>✓</b> (3)             |

| PS                      | MAX II device or a Microprocessor with flash memory | ~               | ~             | <b>✓</b>                 |

|                         | Enhanced Configuration Device                       | ✓               | ~             | ✓                        |

|                         | Download cable                                      | ✓               | ✓             |                          |

| PPA                     | MAX II device or a Microprocessor with flash memory |                 |               | ~                        |

| JTAG                    | MAX II device or a Microprocessor with flash memory |                 |               |                          |

#### Notes to Table 7-4:

- (1) In these modes, the host system must send a DCLK that is  $4\times$  the data rate.

- (2) The enhanced configuration device decompression feature is available, while the Stratix II and Stratix II GX decompression feature is not available.

- (3) Only remote update mode is supported when using the AS configuration scheme. Local update mode is not supported.

# **Configuration Data Decompression**

Stratix II and Stratix II GX devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and transmit this compressed bit stream to Stratix II and Stratix II GX devices. During configuration, Stratix II and Stratix II GX devices automatically recognize the compressed file format and decompresses the bit stream in real time and programs its SRAM cells.

Data indicates that compression typically reduces configuration bit stream size by 35 to 55%.

Stratix II and Stratix II GX devices support decompression in the FPP (when using a MAX II device/microprocessor + flash), AS, and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.

When using FPP mode, the intelligent host must provide a DCLK that is  $4\times$  the data rate. Therefore, the configuration data must be valid for four DCLK cycles.

The decompression feature supported by Stratix II and Stratix II GX devices is different from the decompression feature in enhanced configuration devices (EPC16, EPC8, and EPC4 devices), although they both use the same compression algorithm. The data decompression feature in the enhanced configuration devices allows them to store compressed data and decompress the bitstream before transmitting it to the target devices. When using Stratix II and Stratix II GX devices in FPP mode with enhanced configuration devices, the decompression feature is available only in the enhanced configuration device, not the Stratix II or Stratix II GX device.

In PS mode, use the Stratix II or Stratix II GX decompression feature because sending compressed configuration data reduces configuration time. Do not use both the Stratix II or Stratix II GX device and the enhanced configuration device decompression features simultaneously. The compression algorithm is not intended to be recursive and could expand the configuration file instead of compressing it further.

When you enable compression, the Quartus II software generates configuration files with compressed configuration data. This compressed file reduces the storage requirements in the configuration device or flash memory, and decreases the time needed to transmit the bitstream to the Stratix II or Stratix II GX device. The time required by a Stratix II or Stratix II GX device to decompress a configuration file is less than the time needed to transmit the configuration data to the device.

There are two ways to enable compression for Stratix II and Stratix II GX bitstreams: before design compilation (in the **Compiler Settings** menu) and after design compilation (in the **Convert Programming Files** window).

To enable compression in the project's compiler settings, select **Device** under the **Assignments** menu to bring up the **Settings** window. After selecting your Stratix II or Stratix II GX device, open the **Device & Pin Options** window, and in the **General** settings tab enable the check box for **Generate compressed bitstreams** (as shown in Figure 7–1).

Device & Pin Options General | Configuration | Programming Files | Unused Pins | Dual-Purpose Pins | Voltage | Specify general device options. These options are not dependent on the configuration Changes apply to Compiler settings 'one\_wire' Options: Auto-restart configuration after error □Release clears before tri-states ■Enable user-supplied start-up clock (CLKUSR) □Enable device-wide reset (DEV\_CLRn) □ Enable device-wide output enable (DEV\_OE) ■Enable INIT\_DONE output Generate compressed bitstreams Lyduto usercode JTAG user code (32-bit hexadecimal): FFFFFFF Description: Produces compressed bitstreams and enables bitstream decompression. Reset OK Cancel

Figure 7–1. Enabling Compression for Stratix II and Stratix II GX Bitstreams in Compiler Settings

Compression can also be enabled when creating programming files from the **Convert Programming Files** window.

- 1. Click **Convert Programming Files** (File menu).

- Select the programming file type (POF, SRAM HEXOUT, RBF, or TTF).

- 3. For POF output files, select a configuration device.

- 4. In the **Input files to convert** box, select **SOF Data**.

- 5. Select **Add File** and add a Stratix II or Stratix II GX device SOF(s).

- Select the name of the file you added to the SOF Data area and click Properties.

- 7. Check the **Compression** check box.

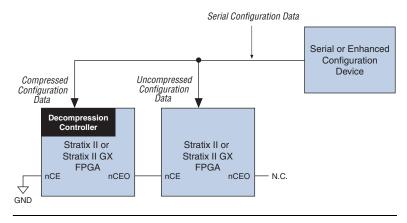

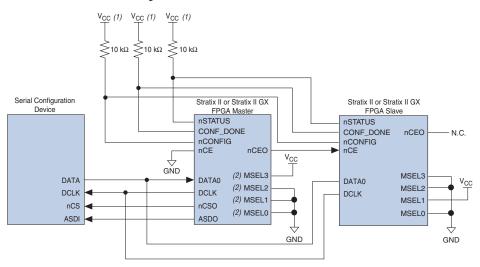

When multiple Stratix II or Stratix II GX devices are cascaded, you can selectively enable the compression feature for each device in the chain if you are using a serial configuration scheme. Figure 7–2 depicts a chain of two Stratix II or Stratix II GX devices. The first Stratix II or Stratix II GX device has compression enabled and therefore receives a compressed bit stream from the configuration device. The second Stratix II or Stratix II GX device has the compression feature disabled and receives uncompressed data.

In a multi-device FPP configuration chain all Stratix II or Stratix II GX devices in the chain must either enable of disable the decompression feature. You can not selectively enable the compression feature for each device in the chain because of the DATA and DCLK relationship.

Figure 7–2. Compressed and Uncompressed Configuration Data in the Same Configuration File

You can generate programming files for this setup from the **Convert Programming Files** window (File menu) in the Quartus II software.

# **Design Security Using Configuration Bitstream Encryption**

Stratix II and Stratix II GX devices are the industry's first devices with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm—the most advanced encryption algorithm available today. When using the design security feature, a

128-bit security key is stored in the Stratix II or Stratix II GX device. In order to successfully configure a Stratix II or Stratix II GX device that has the design security feature enabled, it must be configured with a configuration file that was encrypted using the same 128-bit security key. The security key can be stored in non-volatile memory inside the Stratix II or Stratix II GX device. This non-volatile memory does not require any external devices, such as a battery back-up, for storage.

When using a serial configuration scheme such as passive serial (PS) or active serial (AS), configuration time is the same whether or not the design security feature is enabled. If the fast passive parallel (FPP) scheme is used with the design security or decompression feature, a  $4\times$  DCLK is required. This results in a slower configuration time when compared to the configuration time of an FPGA that has neither the design security, nor decompression feature enabled. For more information about this feature, contact Altera Applications group.

# **Remote System Upgrade**

Stratix II and Stratix II GX devices feature remote and local update.

For more information about this feature, refer to the *Remote System Upgrades With Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Remote System Upgrades With Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*

#### Power-On Reset Circuit

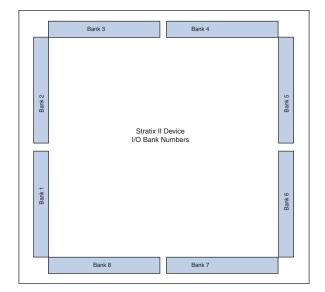

The POR circuit keeps the entire system in reset until the power supply voltage levels have stabilized on power-up. Upon power-up, the device does not release nSTATUS until  $V_{\text{CCINT}}$ ,  $V_{\text{CCPD}}$ , and  $V_{\text{CCIO}}$  of banks 3, 4, 7, and 8 are above the device's POR trip point. On power down,  $V_{\text{CCINT}}$  is monitored for brown-out conditions.

The passive serial (PS) mode (MSEL[3,2,1,0] = 0010) and the Fast passive parallel (FPP) mode (MSEL[3,2,1,0] = 0000) always set bank 3 to use the lower POR trip point consistent with 1.8- and 1.5-V signaling, regardless of the VCCSEL setting. For all other configuration modes, VCCSEL selects the POR trip-point level. Refer to the section "VCCSEL Pin" on page 7–10 for more details.

In Stratix II devices, a pin-selectable option PORSEL is provided that allows you to select between a typical POR time setting of 12 ms or 100 ms. In both cases, you can extend the POR time by using an external component to assert the nSTATUS pin low.

# **V<sub>CCPD</sub> Pins**

Stratix II and Stratix II GX devices also offer a new power supply,  $V_{\rm CCPD}$ , which must be connected to 3.3-V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{\rm CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration pins when VCCSEL is connected to ground. Refer to Table 7–5 for information on the pins affected by VCCSEL.

$V_{\rm CCPD}$  must ramp-up from 0-V to 3.3-V within 100 ms. If  $V_{\rm CCPD}$  is not ramped up within this specified time, your Stratix II or Stratix II GX device will not configure successfully. If your system does not allow for a  $V_{\rm CCPD}$  ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are stable.

### **VCCSEL Pin**

The VCCSEL pin selects the type of input buffer used on configuration input pins and it selects the POR trip point voltage level for  $V_{CCIO}$  bank 3 powered by VCCIO3 pins.

For more information, refer to Table 7–24 on page 7–105.

The configuration input pins and the PLL\_ENA pin (Table 7–5) have a dual buffer design. These pins have a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The VCCSEL input pin selects which input buffer is used during configuration. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD}$ , while the 1.8-V/1.5-V input buffer is powered by  $V_{CCIO}$ . After configuration, the dual-purpose configuration pins are powered by the  $V_{CCIO}$  pins of the bank in which they reside. Table 7–5 shows the pins affected by VCCSEL.

| Table 7–5. Pins Affected by the Voltage Level at VCCSEL |                                                |                                                       |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| Pin                                                     | VCCSEL = LOW (connected to GND)                | $VCCSEL = HIGH (connected to V_{CCPD})$               |  |  |  |  |

| nSTATUS (when used as an input)                         |                                                |                                                       |  |  |  |  |

| nCONFIG                                                 |                                                |                                                       |  |  |  |  |

| CONF_DONE (when used as an input)                       |                                                |                                                       |  |  |  |  |

| DATA[70]                                                |                                                |                                                       |  |  |  |  |

| nCE                                                     |                                                |                                                       |  |  |  |  |

| DCLK (when used as an input)                            |                                                | 1.8/1.5-V input buffer is selected.                   |  |  |  |  |

| CS                                                      | 3.3/2.5-V input buffer is selected.            | Input buffer is powered by V <sub>CCIO</sub> of       |  |  |  |  |

| nWS                                                     | Input buffer is powered by V <sub>CCPD</sub> . | the I/O bank. These input buffers are 3.3 V tolerant. |  |  |  |  |

| nRS                                                     |                                                | 0.0 1 (0.0.4.1.                                       |  |  |  |  |

| nCS                                                     |                                                |                                                       |  |  |  |  |

| CLKUSR                                                  |                                                |                                                       |  |  |  |  |

| DEV_OE                                                  |                                                |                                                       |  |  |  |  |

| DEV_CLRn                                                |                                                |                                                       |  |  |  |  |

| RUnLU                                                   |                                                |                                                       |  |  |  |  |

| PLL_ENA                                                 |                                                |                                                       |  |  |  |  |

VCCSEL is sampled during power-up. Therefore, the VCCSEL setting cannot change on the fly or during a reconfiguration. The VCCSEL input buffer is powered by  $V_{CCINT}$  and has an internal 5-k $\Omega$  pull-down resistor that is always active.

VCCSEL must be hardwired to  $V_{CCPD}$  or GND.

A logic high selects the 1.8-V/1.5-V input buffer, and a logic low selects the 3.3-V/2.5-V input buffer. VCCSEL should be set to comply with the logic levels driven out of the configuration device or MAX II device or a microprocessor with flash memory.

VCCSEL also sets the POR trip point for I/O bank 3 to ensure that this I/O bank has powered up to the appropriate voltage levels before configuration begins. For passive serial (PS) mode (MSEL[3..0] = 0010) and for Fast passive parallel (FPP) mode (MSEL[3..0] = 0000) the POR circuitry selects the trip point associated with 1.5-V/1.8-V signaling. For all other configuration modes defined by MSEL[3..0] settings (other

than 00X0 (MSEL[1] = X, "don't care"), VCCSEL=GND selects the higher I/O bank 3 POR trip point for 2.5-V/3.3-V signaling and VCCSEL=VCCPD selects the lower I/O bank 3 POR trip point associated with 1.5-V/1.8-V signaling.

For all configuration modes with MSEL[3..0] not equal to 00X0 (MSEL[1] = X, "don't care"), if VCCIO of configuration bank 3 is powered by 1.8-V or 1.5-V and VCCSEL = GND, the voltage supplied to this I/O bank(s) may never reach the POR trip point, which prevents the device from beginning configuration.

If the VCCIO of I/O bank 3 is powered by 1.5- or 1.8-V and the configuration signals used require 3.3- or 2.5-V signaling, you should set VCCSEL to VCCPD to enable the 1.8-/1.5-V input buffers for configuration. The 1.8-V/1.5-V input buffers are 3.3-V tolerant.

The fast passive parallel (FPP) and passive serial (PS) modes always enable bank 3 to use the POR trip point to be consistent with 1.8- and 1.5-V signaling, regardless of the VCCSEL setting.

Table 7–6 shows how you should set VCCSEL depending on the configuration mode, the voltage level on VCCIO3 pins that power bank 3, and the supported configuration input voltages.

| Table 7–6. Supported $V_{\it CCSEL}$ Setting Based on Mode, VCCIO3, and Input Configuration Voltage     |             |             |                       |  |  |  |

|---------------------------------------------------------------------------------------------------------|-------------|-------------|-----------------------|--|--|--|

| Configuration Mode V <sub>CCIO</sub> (Bank 3) Supported Configuration Input Voltages V <sub>CCSEL</sub> |             |             |                       |  |  |  |

| All modes                                                                                               | 3.3-V/2.5-V | 3.3-V/2.5-V | GND                   |  |  |  |

| All modes                                                                                               | 1.8-V/1.5-V | 3.3-V/2.5-V | V <sub>CCPD</sub> (1) |  |  |  |

| All modes                                                                                               | 1.8-V/1.5-V | 1.8-V/1.5-V | V <sub>CCPD</sub>     |  |  |  |

| _                                                                                                       | 3.3-V/2.5-V | 1.8-V/1.5-V | Not Supported         |  |  |  |

Note to Table 7-6:

(1) The VCCSEL pin can also be connected to GND for PS (MSEL[3..0]=0010) and FPP (MSEL[3..0]=0000) modes.

Table 7–7 shows the configuration mode support for banks 4, 7, and 8.

| Table 7–7. Stratix II Configuration Mode Support for Banks 4, 7 and 8               |                                                                        |                |              |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|--------------|--|--|--|--|

|                                                                                     | Configuration Voltage/ $V_{\text{CCIO}}$ Support for Banks 4, 7, and 8 |                |              |  |  |  |  |

| Configuration Mode                                                                  | 3.3/3.3                                                                | 1.8/1.8        | 3.3/1.8      |  |  |  |  |

|                                                                                     | VCCSEL = GND                                                           | VCCSEL = VCCPD | VCCSEL = GND |  |  |  |  |

| Fast passive parallel                                                               | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Passive parallel asynchronous                                                       | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Passive serial                                                                      | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Remote system upgrade FPP                                                           | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Remote system upgrade PPA                                                           | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Remote system upgrade PS                                                            | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Fast AS (40 MHz)                                                                    | Y                                                                      | Υ              | Υ            |  |  |  |  |

| Remote system upgrade fast AS (40 MHz)                                              | Y                                                                      | Y              | Y            |  |  |  |  |

| FPP with decompression and/or design security                                       | Y                                                                      | Y              | Y            |  |  |  |  |

| Remote system upgrade FPP with decompression and/or design security feature enabled | Y                                                                      | Y              | Y            |  |  |  |  |

| AS (20 MHz)                                                                         | Υ                                                                      | Y              | Υ            |  |  |  |  |

| Remote system upgrade AS (20 MHz)                                                   | Υ                                                                      | Y              | Υ            |  |  |  |  |

# **Output Configuration Pins**

You must verify that the configuration output pins for your chosen configuration modes meet the  $V_{\rm IH}$  of the configuration device. Refer to Table 7–22 on page 7–94 for a consolidated list of configuration output pins.

The  $V_{IH}$  of 3.3 V or 2.5 V configuration devices will not be met when the  $V_{CCIO}$  of the output configuration pins are 1.8 V or 1.5 V. Level shifters will be required to meet the input high level voltage threshold  $V_{IH}$ .

Note that AS mode is only applicable for 3.3-V configurations. If I/O bank 3 is less than 3.3 V, level shifters are required on the output pins (DCLK, nCSO, ASDO) from the Stratix II or Stratix II GX device back to the EPCS device.

The key is to ensure the VCCIO voltage of bank 3 is high enough to trip the VCCIO3 POR trip point on power-up. Also, to make sure the configuration device meets the  $V_{\rm IH}$  for the configuration input pins based on the selected input buffer.

# Fast Passive Parallel Configuration

Fast passive parallel (FPP) configuration in Stratix II and Stratix II GX devices is designed to meet the continuously increasing demand for faster configuration times. Stratix II and Stratix II GX devices are designed with the capability of receiving byte-wide configuration data per clock cycle. Table 7–8 shows the MSEL pin settings when using the FFP configuration scheme.

**Table 7–8. Stratix II and Stratix II GX MSEL Pin Settings for FPP Configuration Schemes** Notes (1), (2), and (3)

| Configuration Scheme                                                                                | MSEL3 | MSEL2 | MSEL1 | MSEL0 |

|-----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| FPP when not using remote system upgrade or decompression and/or design security feature            | 0     | 0     | 0     | 0     |

| FPP when using remote system upgrade (4)                                                            | 0     | 1     | 0     | 0     |

| FPP with decompression and/or design security feature enabled (5)                                   | 1     | 0     | 1     | 1     |

| FPP when using remote system upgrade and decompression and/or design security feature $(4)$ , $(5)$ | 1     | 1     | 0     | 0     |

#### Notes to Table 7-8:

- (1) You must verify the configuration output pins for your chosen configuration modes meet the V<sub>IH</sub> of the configuration device. Refer to Table 7–22 for a consolidated list of configuration output pins.

- (2) The  $V_{IH}$  of 3.3-V or 2.5-V configuration devices will not be met when the VCCIO of the output configuration pins is 1.8-V or 1.5-V. Level shifters will be required to meet the input high level voltage threshold  $V_{IH}$ .

- (3) The VCCSEL signal does not control TDO or nCEO. During configuration, these pins drive out voltage levels corresponding to the VCCIO supply voltage that powers the I/O bank containing the pin. For more information about multi-volt support, including information about using TDO and nCEO in multi-volt systems, refer to the Stratix II GX Architecture chapter in volume 1 of the Stratix II GX Device Handbook.

- (4) These schemes require that you drive the RUnlu pin to specify either remote update or local update. For more information about remote system upgrade in Stratix II devices, refer to the Remote System Upgrades With Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II Device Handbook or the Remote System Upgrades With Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook.

- (5) These modes are only supported when using a MAX II device or a microprocessor with flash memory for configuration. In these modes, the host system must output a DCLK that is 4× the data rate.

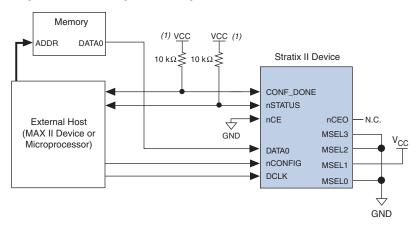

FPP configuration of Stratix II and Stratix II GX devices can be performed using an intelligent host, such as a MAX II device, a microprocessor, or an Altera enhanced configuration device.

## FPP Configuration Using a MAX II Device as an External Host

FPP configuration using compression and an external host provides the fastest method to configure Stratix II and Stratix II GX devices. In the FPP configuration scheme, a MAX II device can be used as an intelligent host that controls the transfer of configuration data from a storage device, such as flash memory, to the target Stratix II or Stratix II GX device. Configuration data can be stored in RBF, HEX, or TTF format. When using the MAX II devices as an intelligent host, a design that controls the configuration process, such as fetching the data from flash memory and sending it to the device, must be stored in the MAX II device.

If you are using the Stratix II or Stratix II GX decompression and/or design security feature, the external host must be able to send a DCLK frequency that is  $4 \times$  the data rate.

The  $4\times$  DCLK signal does not require an additional pin and is sent on the DCLK pin. The maximum DCLK frequency is 100 MHz, which results in a maximum data rate of 200 Mbps. If you are not using the Stratix II or Stratix II GX decompression or design security features, the data rate is  $8\times$  the DCLK frequency.

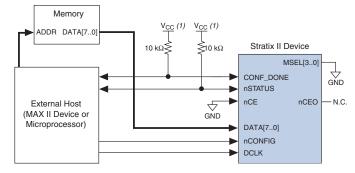

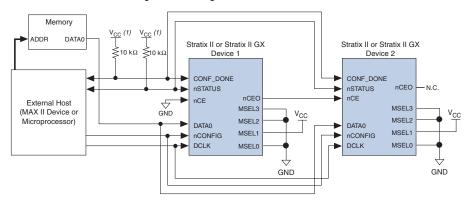

Figure 7–3 shows the configuration interface connections between the Stratix II or Stratix II GX device and a MAX II device for single device configuration.

Figure 7–3. Single Device FPP Configuration Using an External Host

Note to Figure 7-3:

(1) The pull-up resistor should be connected to a supply that provides an acceptable input signal for the device.  $V_{CC}$  should be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

Upon power-up, the Stratix II and Stratix II GX devices go through a Power-On Reset (POR). The POR delay is dependent on the PORSEL pin setting; when PORSEL is driven low, the POR time is approximately 100 ms, if PORSEL is driven high, the POR time is approximately 12 ms. During POR, the device resets, holds nSTATUS low, and tri-states all user I/O pins. Once the device successfully exits POR, all user I/O pins continue to be tri-stated. If nIO\_pullup is driven low during power-up and configuration, the user I/O pins and dual-purpose I/O pins have weak pull-up resistors, which are on (after POR) before and during configuration. If nIO\_pullup is driven high, the weak pull-up resistors are disabled.

You can hold nConfig low in order to stop device configuration.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration can be found in the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook* or the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

The configuration cycle consists of three stages: reset, configuration and initialization. While nCONFIG or nSTATUS are low, the device is in the reset stage. To initiate configuration, the MAX II device must drive the nCONFIG pin from low-to-high.

$V_{\text{CCINT}}$ ,  $V_{\text{CCIO}}$ , and  $V_{\text{CCPD}}$  of the banks where the configuration and JTAG pins reside need to be fully powered to the appropriate voltage levels in order to begin the configuration process.

When nCONFIG goes high, the device comes out of reset and releases the open-drain nSTATUS pin, which is then pulled high by an external 10-k $\Omega$  pull-up resistor. Once nSTATUS is released, the device is ready to receive configuration data and the configuration stage begins. When nSTATUS is pulled high, the MAX II device places the configuration data one byte at a time on the DATA[7..0] pins.

Stratix II and Stratix II GX devices receive configuration data on the DATA[7..0] pins and the clock is received on the DCLK pin. Data is latched into the device on the rising edge of DCLK. If you are using the Stratix II or Stratix II GX decompression and/or design security feature, configuration data is latched on the rising edge of every fourth DCLK cycle. After the configuration data is latched in, it is processed during the following three DCLK cycles.

Data is continuously clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin goes high one byte early in parallel configuration (FPP and PPA) modes. The last byte is required for serial configuration (AS and PS) modes. After the device has received the next to last byte of the configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by an external  $10\text{-}k\Omega$  pull-up resistor. A low-to-high transition on CONF\_DONE indicates configuration is complete and initialization of the device can begin. The CONF\_DONE pin must have an external  $10\text{-}k\Omega$  pull-up resistor in order for the device to initialize.

In Stratix II and Stratix II GX devices, the initialization clock source is either the internal oscillator (typically 10 MHz) or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If the internal oscillator is used, the Stratix II or Stratix II GX device provides itself with enough clock cycles for proper initialization. Therefore, if the internal oscillator is the initialization clock source, sending the entire configuration file to the device is sufficient to configure and initialize the device. Driving DCLK to the device after configuration is complete does not affect device operation.

You can also synchronize initialization of multiple devices or to delay initialization with the CLKUSR option. The **Enable user-supplied start-up clock** (**CLKUSR**) option can be turned on in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. Supplying a clock on CLKUSR does not affect the configuration process. The CONF\_DONE pin goes high one byte early in parallel configuration (FPP and PPA) modes. The last byte is required for serial configuration (AS and PS) modes. After the CONF\_DONE pin transitions high, CLKUSR is enabled after the time specified as t<sub>CD2CU</sub>. After this time period elapses, Stratix II and Stratix II GX devices require 299 clock cycles to initialize properly and enter user mode. Stratix II and Stratix II GX devices support a CLKUSR f<sub>MAX</sub> of 100 MHz.

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user-mode with a low-to-high transition. This <code>Enable INIT\_DONE Output</code> option is available in the Quartus II software from the <code>General</code> tab of the <code>Device & Pin Options</code> dialog box. If the <code>INIT\_DONE</code> pin is used, it is high because of an external 10-k $\Omega$  pull-up resistor when <code>nCONFIG</code> is low and during the beginning of configuration. Once the option bit to enable <code>INIT\_DONE</code> is programmed into the device (during the first frame of configuration data), the <code>INIT\_DONE</code> pin goes low. When initialization is complete, the <code>INIT\_DONE</code> pin is released and pulled high. The MAX II device must be able to detect this low-to-high transition, which signals the device has

entered user mode. When initialization is complete, the device enters user mode. In user-mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

To ensure DCLK and DATA[7..0] are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA[7..0] pins are available as user I/O pins after configuration. When you select the FPP scheme in the Quartus II software, as a default, these I/O pins are tri-stated in user mode. To change this default option in the Quartus II software, select the **Pins** tab of the **Device & Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

If you are using the Stratix II or Stratix II GX decompression and/or design security feature and need to stop DCLK, it can only be stopped three clock cycles after the last data byte was latched into the Stratix II or Stratix II GX device.

By stopping DCLK, the configuration circuit allows enough clock cycles to process the last byte of latched configuration data. When the clock restarts, the MAX II device must provide data on the DATA[7..0] pins prior to sending the first DCLK rising edge.

If an error occurs during configuration, the device drives its nSTATUS pin low, resetting itself internally. The low signal on the nSTATUS pin also alerts the MAX II device that there is an error. If the **Auto-restart configuration after error** option (available in the Quartus II software from the **General** tab of the **Device & Pin Options** (dialog box) is turned on, the device releases nSTATUS after a reset time-out period (maximum of  $100~\mu s$ ). After nSTATUS is released and pulled high by a pull-up resistor, the MAX II device can try to reconfigure the target device without needing to pulse nCONFIG low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2  $\mu s$ ) on nCONFIG to restart the configuration process.

The MAX II device can also monitor the CONF\_DONE and INIT\_DONE pins to ensure successful configuration. The CONF\_DONE pin must be monitored by the MAX II device to detect errors and determine when programming completes. If all configuration data is sent, but the CONF\_DONE or INIT\_DONE signals have not gone high, the MAX II device will reconfigure the target device.

If the optional CLKUSR pin is used and nCONFIG is pulled low to restart configuration during device initialization, you need to ensure CLKUSR continues toggling during the time nSTATUS is low (maximum of  $100 \mu s$ ).

When the device is in user-mode, initiating a reconfiguration is done by transitioning the nconfig pin low-to-high. The nconfig pin should be low for at least 2 µs. When nconfig is pulled low, the device also pulls nstatus and conf\_done low and all I/O pins are tri-stated. Once nconfig returns to a logic high level and nstatus is released by the device, reconfiguration begins.

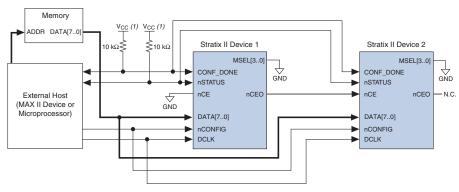

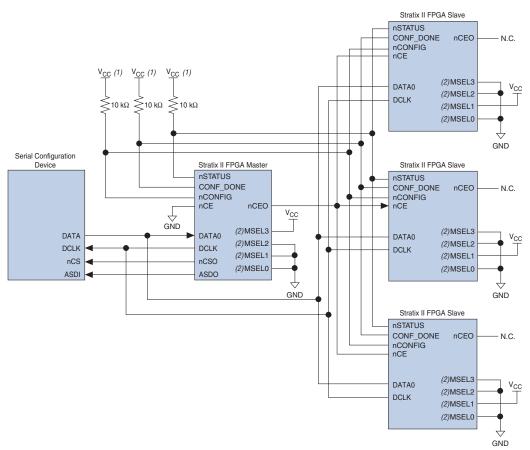

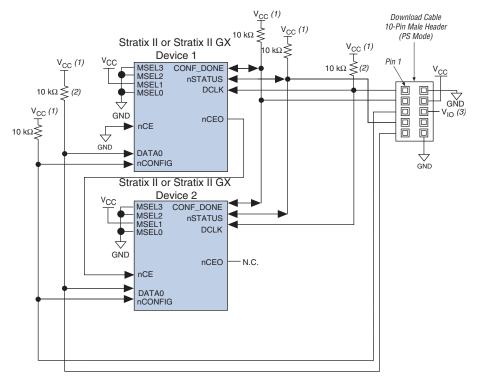

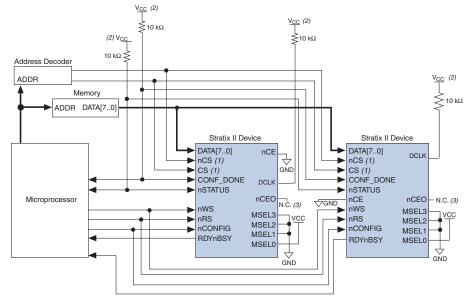

Figure 7–4 shows how to configure multiple devices using a MAX II device. This circuit is similar to the FPP configuration circuit for a single device, except the Stratix II or Stratix II GX devices are cascaded for multi-device configuration.

Figure 7-4. Multi-Device FPP Configuration Using an External Host

Note to Figure 7-4:

The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain. V<sub>CC</sub> should be high enough to meet the V<sub>IH</sub> specification of the I/O standard on the device and the external host.

In multi-device FPP configuration, the first device's nCE pin is connected to GND while its nCEO pin is connected to nCE of the next device in the chain. The last device's nCE input comes from the previous device, while its nCEO pin is left floating. After the first device completes configuration in a multi-device configuration chain, its nCEO pin drives low to activate the second device's nCE pin, which prompts the second device to begin configuration. The second device in the chain begins configuration within one clock cycle; therefore, the transfer of data destinations is transparent to the MAX II device. All other configuration pins (nCONFIG, nSTATUS, DCLK, DATA[7..0], and CONF\_DONE) are connected to every device in

the chain. The configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Ensure that the DCLK and DATA lines are buffered for every fourth device. Because all device CONF\_DONE pins are tied together, all devices initialize and enter user mode at the same time.

All nSTATUS and CONF\_DONE pins are tied together and if any device detects an error, configuration stops for the entire chain and the entire chain must be reconfigured. For example, if the first device flags an error on nSTATUS, it resets the chain by pulling its nSTATUS pin low. This behavior is similar to a single device detecting an error.

If the Auto-restart configuration after error option is turned on, the devices release their nSTATUS pins after a reset time-out period (maximum of 100  $\mu$ s). After all nSTATUS pins are released and pulled high, the MAX II device can try to reconfigure the chain without pulsing nCONFIG low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2  $\mu$ s) on nCONFIG to restart the configuration process.

In a multi-device FPP configuration chain, all Stratix II or Stratix II GX devices in the chain must either enable or disable the decompression and/or design security feature. You can not selectively enable the decompression and/or design security feature for each device in the chain because of the DATA and DCLK relationship. If the chain contains devices that do not support design security, you should use a serial configuration scheme.

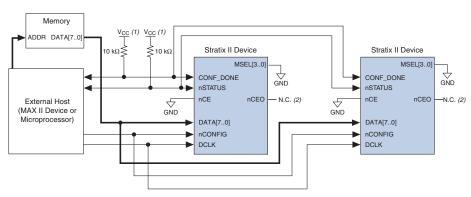

If a system has multiple devices that contain the same configuration data, tie all device nCE inputs to GND, and leave nCEO pins floating. All other configuration pins (nCONFIG, nSTATUS, DCLK, DATA[7..0], and CONF\_DONE) are connected to every device in the chain. Configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Ensure that the DCLK and DATA lines are buffered for every fourth device. Devices must be the same density and package. All devices start and complete configuration at the same time. Figure 7–5 shows multi-device FPP configuration when both Stratix II or Stratix II GX devices are receiving the same configuration data.

Figure 7–5. Multiple-Device FPP Configuration Using an External Host When Both Devices Receive the Same Data

#### *Notes to Figure 7–5:*

- The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain. V<sub>CC</sub> should be high enough to meet the V<sub>IH</sub> specification of the I/O on the device and the external host.

- (2) The nCEO pins of both Stratix II or Stratix II GX devices are left unconnected when configuring the same configuration data into multiple devices.

You can use a single configuration chain to configure Stratix II or Stratix II GX devices with other Altera devices that support FPP configuration, such as Stratix devices. To ensure that all devices in the chain complete configuration at the same time or that an error flagged by one device initiates reconfiguration in all devices, tie all of the device CONF\_DONE and nSTATUS pins together.

For more information on configuring multiple Altera devices in the same configuration chain, refer to *Configuring Mixed Altera FPGA Chains* in volume 2 of the *Configuration Handbook*.

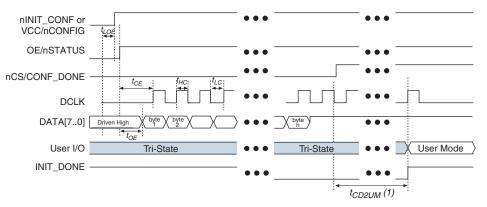

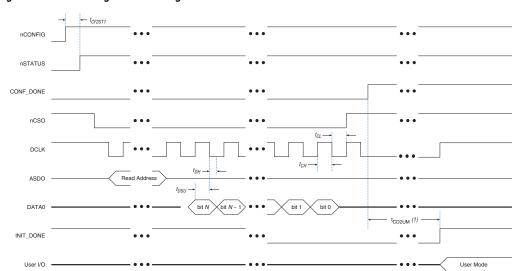

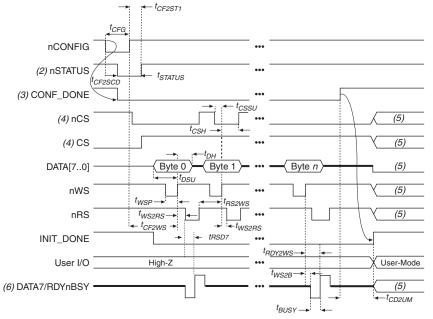

# FPP Configuration Timing

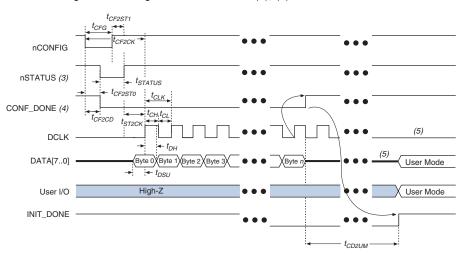

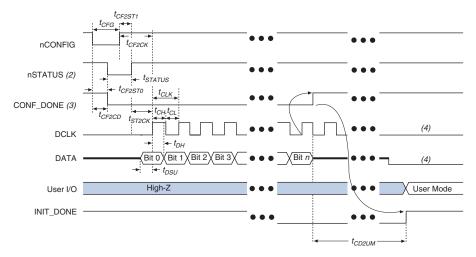

Figure 7–6 shows the timing waveform for FPP configuration when using a MAX II device as an external host. This waveform shows the timing when the decompression and the design security feature are not enabled.

Figure 7–6. FPP Configuration Timing Waveform Notes (1), (2)

#### *Notes to Figure 7–6:*

- (1) This timing waveform should be used when the decompression and design security feature are not used.

- (2) The beginning of this waveform shows the device in user-mode. In user-mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (3) Upon power-up, the Stratix II or Stratix II GX device holds nSTATUS low for the time of the POR delay.

- (4) Upon power-up, before and during configuration, CONF\_DONE is low.

- (5) DCLK should not be left floating after configuration. It should be driven high or low, whichever is more convenient.

- (6) DATA[7..0] are available as user I/O pins after configuration and the state of these pins depends on the dual-purpose pin settings.

Table 7–9 defines the timing parameters for Stratix II and Stratix II GX devices for FPP configuration when the decompression and the design security features are not enabled.

| Table 7-            | Notes (1), (2)                            |     |         |       |

|---------------------|-------------------------------------------|-----|---------|-------|

| Symbol              | Parameter                                 | Min | Max     | Units |

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low              |     | 800     | ns    |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low                |     | 800     | ns    |

| t <sub>CFG</sub>    | nCONFIG low pulse width                   | 2   |         | μs    |

| t <sub>STATUS</sub> | nSTATUS low pulse width                   | 10  | 100 (3) | μs    |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high              |     | 100 (3) | μs    |

| t <sub>CF2CK</sub>  | nCONFIG high to first rising edge on DCLK | 100 |         | μs    |

| t <sub>ST2CK</sub>  | nSTATUS high to first rising edge of DCLK | 2   |         | μs    |

| Table 7–9. FPP Timing Parameters for Stratix II and Stratix II GX Devices (Part 2 of 2)         Notes (1), (2) |                                                   |                                                  |     |       |  |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|-----|-------|--|

| Symbol                                                                                                         | Parameter                                         | Min                                              | Max | Units |  |

| t <sub>DSU</sub>                                                                                               | Data setup time before rising edge on DCLK        | 5                                                |     | ns    |  |

| t <sub>DH</sub>                                                                                                | Data hold time after rising edge on DCLK          | 0                                                |     | ns    |  |

| t <sub>CH</sub>                                                                                                | DCLK high time                                    | 4                                                |     | ns    |  |

| t <sub>CL</sub>                                                                                                | DCLK low time                                     | 4                                                |     | ns    |  |

| t <sub>CLK</sub>                                                                                               | DCLK period                                       | 10                                               |     | ns    |  |

| f <sub>MAX</sub>                                                                                               | DCLK frequency                                    |                                                  | 100 | MHz   |  |

| t <sub>R</sub>                                                                                                 | Input rise time                                   |                                                  | 40  | ns    |  |

| t <sub>F</sub>                                                                                                 | Input fall time                                   |                                                  | 40  | ns    |  |

| t <sub>CD2UM</sub>                                                                                             | CONF_DONE high to user mode (4)                   | 20                                               | 100 | μs    |  |

| t <sub>CD2CU</sub>                                                                                             | CONF_DONE high to CLKUSR enabled                  | 4 × maximum  DCLK period                         |     |       |  |

| t <sub>CD2UMC</sub>                                                                                            | CONF_DONE high to user mode with CLKUSR option on | $t_{\text{CD2CU}}$ +(299 $\times$ CLKUSR period) |     |       |  |

#### Notes to Table 7-9:

- (1) This information is preliminary.

- (2) These timing parameters should be used when the decompression and design security feature are not used.

- (3) This value is obtainable if users do not delay configuration by extending the nconfig or nstatus low pulse width.

- (4) The minimum and maximum numbers apply only if the internal oscillator is chosen as the clock source for starting up the device.

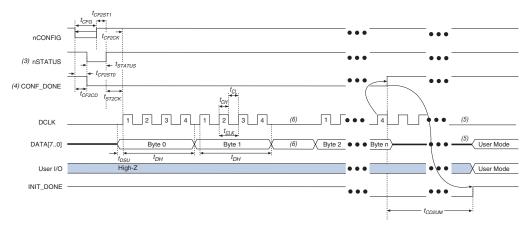

Figure 7–7 shows the timing waveform for FPP configuration when using a MAX II device as an external host. This waveform shows the timing when the decompression and/or the design security feature are enabled.

Figure 7–7. FPP Configuration Timing Waveform With Decompression or Design Security Feature Enabled Notes (1), (2)

#### Notes to Figure 7–7:

- (1) This timing waveform should be used when the decompression and/or design security feature are used.

- (2) The beginning of this waveform shows the device in user-mode. In user-mode, nCONFIG, nSTATUS and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (3) Upon power-up, the Stratix II or Stratix II GX device holds nSTATUS low for the time of the POR delay.

- (4) Upon power-up, before and during configuration, CONF\_DONE is low.

- (5) DCLK should not be left floating after configuration. It should be driven high or low, whichever is more convenient.

- (6) DATA[7..0] are available as user I/O pins after configuration and the state of these pins depends on the dual-purpose pin settings.

- (7) If needed, DCLK can be paused by holding it low. When DCLK restarts, the external host must provide data on the DATA[7..0] pins prior to sending the first DCLK rising edge.

Table 7–10 defines the timing parameters for Stratix II and Stratix II GX devices for FPP configuration when the decompression and/or the design security feature are enabled.

Table 7–10. FPP Timing Parameters for Stratix II and Stratix II GX Devices With Decompression or Design Security Feature Enabled Note (1)

| Symbol              | Parameter                                         | Min                                        | Max     | Units |

|---------------------|---------------------------------------------------|--------------------------------------------|---------|-------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low                      |                                            | 800     | ns    |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low                        |                                            | 800     | ns    |

| t <sub>CFG</sub>    | nCONFIG low pulse width                           | 2                                          |         | μs    |

| t <sub>STATUS</sub> | nSTATUS low pulse width                           | 10                                         | 100 (2) | μs    |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high                      |                                            | 100 (2) | μs    |

| t <sub>CF2CK</sub>  | nCONFIG high to first rising edge on DCLK         | 100                                        |         | μs    |

| t <sub>ST2CK</sub>  | nSTATUS high to first rising edge of DCLK         | 2                                          |         | μs    |

| t <sub>DSU</sub>    | Data setup time before rising edge on DCLK        | 5                                          |         | ns    |

| t <sub>DH</sub>     | Data hold time after rising edge on DCLK          | 30                                         |         | ns    |

| t <sub>CH</sub>     | DCLK high time                                    | 4                                          |         | ns    |

| t <sub>CL</sub>     | DCLK low time                                     | 4                                          |         | ns    |

| t <sub>CLK</sub>    | DCLK period                                       | 10                                         |         | ns    |

| f <sub>MAX</sub>    | DCLK frequency                                    |                                            | 100     | MHz   |

| t <sub>DATA</sub>   | Data rate                                         |                                            | 200     | Mbps  |

| t <sub>R</sub>      | Input rise time                                   |                                            | 40      | ns    |

| t <sub>F</sub>      | Input fall time                                   |                                            | 40      | ns    |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (3)                   | 20                                         | 100     | μs    |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | 4 × maximum  DCLK period                   |         |       |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | $t_{\text{CD2CU}}$ + (299 × CLKUSR period) |         |       |

#### Notes to Table 7-10:

- (1) These timing parameters should be used when the decompression and design security feature are used.

- (2) This value is obtainable if users do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

- (3) The minimum and maximum numbers apply only if the internal oscillator is chosen as the clock source for starting up the device.

Device configuration options and how to create configuration files are discussed further in the *Software Settings* chapter in the *Configuration Handbook*.

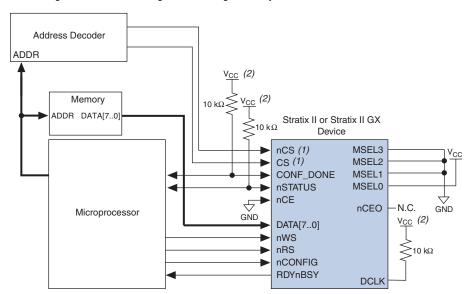

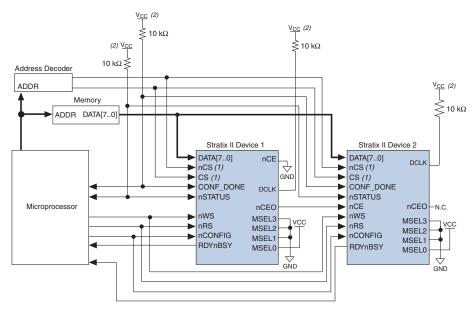

## **FPP Configuration Using a Microprocessor**

In the FPP configuration scheme, a microprocessor can control the transfer of configuration data from a storage device, such as flash memory, to the target Stratix II or Stratix II GX device.

All information in "FPP Configuration Using a MAX II Device as an External Host" on page 7–15 is also applicable when using a microprocessor as an external host. Refer to that section for all configuration and timing information.

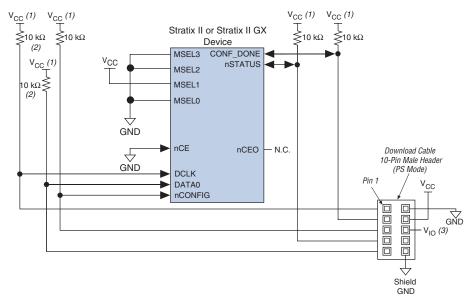

# FPP Configuration Using an Enhanced Configuration Device

In the FPP configuration scheme, an enhanced configuration device sends a byte of configuration data every DCLK cycle to the Stratix II or Stratix II GX device. Configuration data is stored in the configuration device.

When configuring your Stratix II or Stratix II GX device using FPP mode and an enhanced configuration device, the enhanced configuration device decompression feature is available while the Stratix II and Stratix II GX decompression and design security features are not.

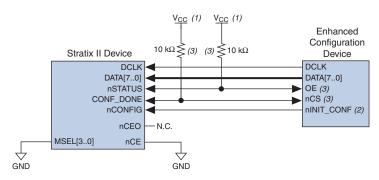

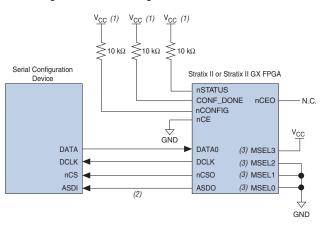

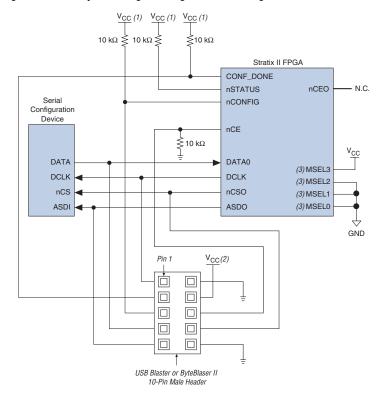

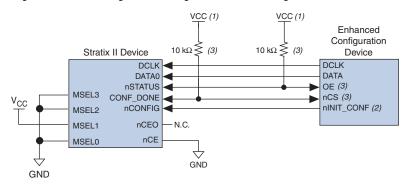

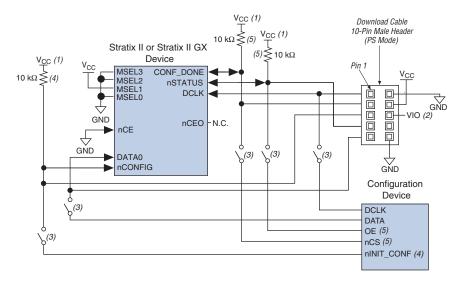

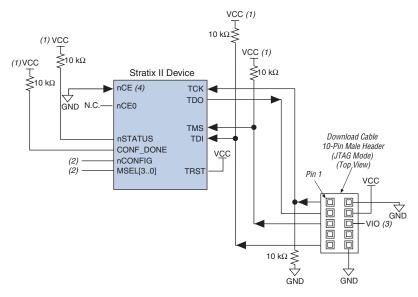

Figure 7–8 shows the configuration interface connections between a Stratix II or Stratix II GX device and the enhanced configuration device for single device configuration.

The figures in this chapter only show the configuration-related pins and the configuration pin connections between the configuration device and the device.

For more information on the enhanced configuration device and flash interface pins, such as PGM[2..0], EXCLK, PORSEL, A[20..0], and DQ[15..0], refer to the *Enhanced Configuration Devices* (EPC4, EPC8 & EPC16) Data Sheet in volume 2 of the Configuration Handbook.

Figure 7–8. Single Device FPP Configuration Using an Enhanced Configuration Device

Notes to Figure 7-8:

- The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active. This means an external pull-up resistor should not be used on the ninit\_conf-nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor.

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the Disable nCS and OE pull-ups on configuration device option when generating programming files.

The value of the internal pull-up resistors on the enhanced configuration devices can be found in the *Enhanced Configuration Devices* (*EPC4*, *EPC8* & *EPC16*) *Data Sheet* in volume 2 of the *Configuration Handbook*.

When using enhanced configuration devices, you can connect the device's nconfig pin to ninit\_conf pin of the enhanced configuration device, which allows the init\_conf JTAG instruction to initiate device configuration. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to  $V_{\rm CC}$  either directly or through a resistor. An internal pull-up resistor on the ninit\_conf pin is always active in the enhanced configuration devices, which means an external pull-up resistor should not be used if nconfig is tied to ninit\_conf.

Upon power-up, the Stratix II or Stratix II GX device goes through a POR. The POR delay is dependent on the PORSEL pin setting; when PORSEL is driven low, the POR time is approximately 100 ms, if PORSEL is driven high, the POR time is approximately 12 ms. During POR, the device will reset, hold nSTATUS low, and tri-state all user I/O pins. The

configuration device also goes through a POR delay to allow the power supply to stabilize. The POR time for enhanced configuration devices can be set to either 100 ms or 2 ms, depending on its PORSEL pin setting. If the PORSEL pin is connected to GND, the POR delay is 100 ms. If the PORSEL pin is connected to  $V_{\rm CC}$ , the POR delay is 2 ms. During this time, the configuration device drives its OE pin low. This low signal delays configuration because the OE pin is connected to the target device's nSTATUS pin.

When selecting a POR time, you need to ensure that the device completes power-up before the enhanced configuration device exits POR. Altera recommends that you use a 12-ms POR time for the Stratix II or Stratix II GX device, and use a 100-ms POR time for the enhanced configuration device.

When both devices complete POR, they release their open-drain OE or nSTATUS pin, which is then pulled high by a pull-up resistor. Once the device successfully exits POR, all user I/O pins continue to be tri-stated. If nIO\_pullup is driven low during power-up and configuration, the user I/O pins and dual-purpose I/O pins will have weak pull-up resistors, which are on (after POR) before and during configuration. If nIO\_pullup is driven high, the weak pull-up resistors are disabled.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration can be found in the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

When the power supplies have reached the appropriate operating voltages, the target device senses the low-to-high transition on nCONFIG and initiates the configuration cycle. The configuration cycle consists of three stages: reset, configuration and initialization. While nCONFIG or nSTATUS are low, the device is in reset. The beginning of configuration can be delayed by holding the nCONFIG or nSTATUS pin low.

$V_{\rm CCINT}$ ,  $V_{\rm CCIO}$  and  $V_{\rm CCPD}$  of the banks where the configuration and JTAG pins reside need to be fully powered to the appropriate voltage levels in order to begin the configuration process.

When nconfig goes high, the device comes out of reset and releases the nstatus pin, which is pulled high by a pull-up resistor. Enhanced configuration devices have an optional internal pull-up resistor on the OE pin. This option is available in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If this internal pull-up resistor is not used, an external 10-k $\Omega$  pull-up resistor on the OE-nstatus line is required. Once nstatus is released, the device is ready to receive configuration data and the configuration stage begins.

When nSTATUS is pulled high, the configuration device's OE pin also goes high and the configuration device clocks data out to the device using the Stratix II or Stratix II GX device's internal oscillator. The Stratix II and Stratix II GX devices receive configuration data on the DATA[7..0] pins and the clock is received on the DCLK pin. A byte of data is latched into the device on each rising edge of DCLK.

After the device has received all configuration data successfully, it releases the open-drain CONF\_DONE pin which is pulled high by a pull-up resistor. Because CONF\_DONE is tied to the configuration device's nCS pin, the configuration device is disabled when CONF\_DONE goes high. Enhanced configuration devices have an optional internal pull-up resistor on the nCS pin. This option is available in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If this internal pull-up resistor is not used, an external  $10\text{-k}\Omega\text{pull-up}$  resistor on the nCS-CONF\_DONE line is required. A low to high transition on CONF\_DONE indicates configuration is complete and initialization of the device can begin.

In Stratix II and Stratix II GX devices, the initialization clock source is either the internal oscillator (typically 10 MHz) or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If the internal oscillator is used, the Stratix II or Stratix II GX device provides itself with enough clock cycles for proper initialization. You also have the flexibility to synchronize initialization of multiple devices or to delay initialization with the CLKUSR option. The **Enable user-supplied start-up clock (CLKUSR)** option can be turned on in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. Supplying a clock on CLKUSR will not affect the configuration process. After all configuration data has been accepted and CONF\_DONE goes high, CLKUSR will be enabled after the time specified as  $t_{CD2CU}$ . After this time period elapses, Stratix II and Stratix II GX devices require 299 clock cycles to initialize properly and enter user mode. Stratix II and Stratix II GX devices support a CLKUSR  $f_{MAX}$  of 100 MHz.

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user-mode with a low-to-high transition. The <code>Enable INIT\_DONE Output</code> option is available in the Quartus II software from the <code>General</code> tab of the <code>Device & Pin Options</code> dialog box. If the <code>INIT\_DONE</code> pin is used, it will be high due to an external 10-k $\Omega$  pull-up resistor when <code>nCONFIG</code> is low and during the beginning of configuration. Once the option bit to enable <code>INIT\_DONE</code> is programmed into the device (during the first frame of configuration data), the <code>INIT\_DONE</code> pin will go low. When initialization is complete, the <code>INIT\_DONE</code> pin will be released and pulled high. In user-mode, the user

I/O pins will no longer have weak pull-up resistors and will function as assigned in your design. The enhanced configuration device will drive DCLK low and DATA[7..0] high at the end of configuration.

If an error occurs during configuration, the device drives its nSTATUS pin low, resetting itself internally. Since the nSTATUS pin is tied to OE, the configuration device will also be reset. If the **Auto-restart configuration after error** option (available in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box) is turned on, the device will automatically initiate reconfiguration if an error occurs. The Stratix II or Stratix II GX device releases its nSTATUS pin after a reset time-out period (maximum of 100  $\mu$ s). When the nSTATUS pin is released and pulled high by a pull-up resistor, the configuration device reconfigures the chain. If this option is turned off, the external system must monitor nSTATUS for errors and then pulse nCONFIG low for at least 2  $\mu$ s to restart configuration. The external system can pulse nCONFIG if nCONFIG is under system control rather than tied to  $V_{CC}$ .

In addition, if the configuration device sends all of its data and then detects that CONF\_DONE has not gone high, it recognizes that the device has not configured successfully. Enhanced configuration devices wait for 64 DCLK cycles after the last configuration bit was sent for CONF\_DONE to reach a high state. In this case, the configuration device pulls its 0E pin low, which in turn drives the target device's nSTATUS pin low. If the Auto-restart configuration after error option is set in the software, the target device resets and then releases its nSTATUS pin after a reset time-out period (maximum of 100 µs). When nSTATUS returns to a logic high level, the configuration device will try to reconfigure the device.

When CONF\_DONE is sensed low after configuration, the configuration device recognizes that the target device has not configured successfully. Therefore, your system should not pull CONF\_DONE low to delay initialization. Instead, you should use the CLKUSR option to synchronize the initialization of multiple devices that are not in the same configuration chain. Devices in the same configuration chain will initialize together if their CONF\_DONE pins are tied together.

If the optional CLKUSR pin is used and nCONFIG is pulled low to restart configuration during device initialization, ensure CLKUSR continues toggling during the time nSTATUS is low (maximum of  $100 \mu$ s).

When the device is in user-mode, a reconfiguration can be initiated by pulling the nCONFIG pin low. The nCONFIG pin should be low for at least 2 µs. When nCONFIG is pulled low, the device also pulls nSTATUS and CONF\_DONE low and all I/O pins are tri-stated. Because CONF\_DONE is

pulled low, this activates the configuration device because it sees its nCS pin drive low. Once nCONFIG returns to a logic high level and nSTATUS is released by the device, reconfiguration begins.

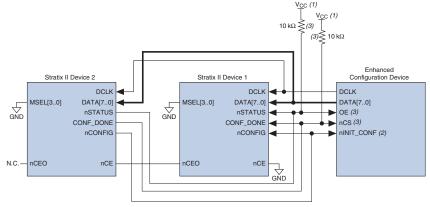

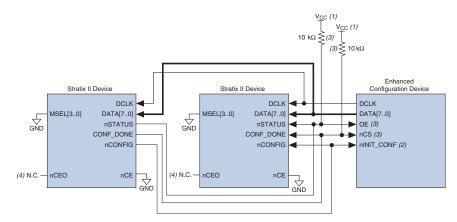

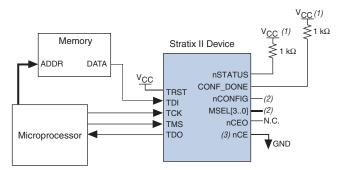

Figure 7–9 shows how to configure multiple Stratix II or Stratix II GX devices with an enhanced configuration device. This circuit is similar to the configuration device circuit for a single device, except the Stratix II or Stratix II GX devices are cascaded for multi-device configuration.

Figure 7–9. Multi-Device FPP Configuration Using an Enhanced Configuration Device

#### *Notes to Figure 7–9:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active. This means an external pull-up resistor should not be used on the ninit\_conf-nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor.

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the Disable nCS and OE pull-up resistors on configuration device option when generating programming files.

Enhanced configuration devices cannot be cascaded.

When performing multi-device configuration, you must generate the configuration device's POF from each project's SOF. You can combine multiple SOFs using the **Convert Programming Files** window in the Quartus II software.

For more information on how to create configuration files for multi-device configuration chains, refer to *Software Settings* in volume 2 of the *Configuration Handbook*.