MII51004-2.1

# Introduction

MAX<sup>®</sup> II devices offer hot socketing, also known as hot plug-in or hot swap, and power sequencing support. Designers can insert or remove a MAX II board in a system during operation without undesirable effects to the system bus. The hot socketing feature removes some of the difficulties designers face when using components on printed circuit boards (PCBs) that contain a mixture of 3.3-, 2.5-, 1.8-, and 1.5-V devices.

The MAX II device hot socketing feature provides:

- Board or device insertion and removal

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter contains the following sections:

- "MAX II Hot-Socketing Specifications" on page 4–1

- "Power-On Reset Circuitry" on page 4–5

# **MAX II Hot-Socketing Specifications**

MAX II devices offer all three of the features required for the hot-socketing capability listed above without any external components or special design requirements. The following are hot-socketing specifications:

- The device can be driven before and during power-up or power-down without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the V<sub>CCIO</sub> or V<sub>CCINT</sub> power supplies. External input signals to device I/O pins do not power the device V<sub>CCIO</sub> or V<sub>CCINT</sub> power supplies via internal paths. This is true if the V<sub>CCINT</sub> and the V<sub>CCIO</sub> supplies are held at GND.

### **Devices Can Be Driven before Power-Up**

Signals can be driven into the MAX II device I/O pins and GCLK [3..0] pins before or during power-up or power-down without damaging the device. MAX II devices support any power-up or power-down sequence ( $V_{CCIO1}$ ,  $V_{CCIO2}$ ,  $V_{CCIO3}$ ,  $V_{CCIO4}$ ,  $V_{CCINT}$ ), simplifying the system-level design.

## I/O Pins Remain Tri-Stated during Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, the MAX II device's output buffers are turned off during system power-up. MAX II devices do not drive out until the device attains proper operating conditions and is fully configured. Refer to "Power-On Reset Circuitry" on page 4–5 for information about turn-on voltages.

### Signal Pins Do Not Drive the V<sub>CCI0</sub> or V<sub>CCI01</sub> Power Supplies

MAX II devices do not have a current path from I/O pins or GCLK [3..0] pins to the  $V_{CCIO}$  or  $V_{CCINT}$  pins before or during power-up. A MAX II device may be inserted into (or removed from) a system board that was powered up without damaging or interfering with system-board operation. When hot socketing, MAX II devices may have a minimal effect on the signal integrity of the backplane.

### **AC and DC Specifications**

You can power up or power down the  $V_{CCIO}$  and  $V_{CCINT}$  pins in any sequence. During hot socketing, the I/O pin capacitance is less than 8 pF. MAX II devices meet the following hot socketing specifications:

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu$ A.

- The hot socketing AC specification is:  $|I_{IOPIN}| < 8 \text{ mA for } 10 \text{ ns or less.}$

MAX II devices are immune to latch-up when hot socketing. If the TCK JTAG input pin is driven high during hot socketing, the current on that pin might exceed the specifications above.

$I_{IOPIN}$  is the current at any user I/O pin on the device. The AC specification applies when the device is being powered up or powered down. This specification takes into account the pin capacitance but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading must be taken into consideration separately. The peak current duration due to power-up transients is 10 ns or less.

The DC specification applies when all  $V_{CC}$  supplies to the device are stable in the powered-up or powered-down conditions.

## Hot Socketing Feature Implementation in MAX II Devices

The hot socketing feature turns off (tri-states) the output buffer during the power-up event (either  $V_{CCINT}$  or  $V_{CCIO}$  supplies) or power-down event. The hot-socket circuit generates an internal HOTSCKT signal when either  $V_{CCINT}$  or  $V_{CCIO}$  is below the threshold voltage during power-up or power-down. The HOTSCKT signal cuts off the output buffer to make sure that no DC current (except for weak pull-up leaking) leaks through the pin. When  $V_{CC}$  ramps up very slowly during power-up,  $V_{CC}$  may still be relatively low even after the power-on reset (POR) signal is released and device configuration is complete.

Make sure that the  $V_{CCINT}$  is within the recommended operating range even though SRAM download has completed.

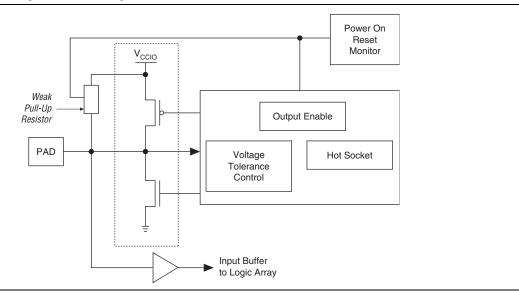

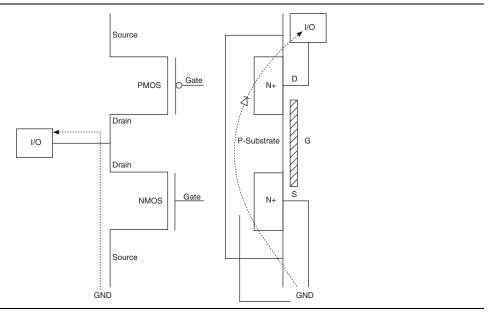

Each I/O and clock pin has the circuitry shown in Figure 4–1.

Figure 4–1. Hot Socketing Circuit Block Diagram for MAX II Devices

The POR circuit monitors  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels and keeps I/O pins tri-stated until the device has completed its flash memory configuration of the SRAM logic. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is enabled during download to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  are powered, and it prevents the I/O pins from driving out when the device is not fully powered or operational. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$  and  $V_{CCINT}$  when driven by external signals before the device is powered.

For information about 5.0-V tolerance, refer to the *Using MAX II Devices in Multi-Voltage Systems* chapter in the *MAX II Device Handbook*.

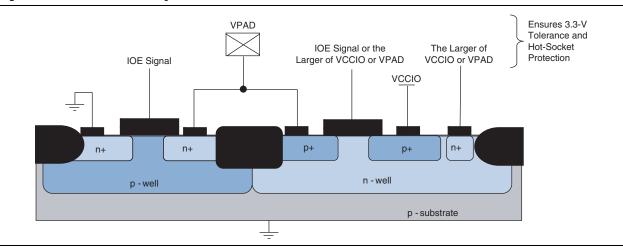

Figure 4–2 shows a transistor-level cross section of the MAX II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{CCIO}$  is powered before  $V_{CCINT}$  or if the I/O pad voltage is higher than  $V_{CCIO}$ . This also applies for sudden voltage spikes during hot insertion. The  $V_{PAD}$  leakage current charges the 3.3-V tolerant circuit capacitance.

#### Figure 4-2. Transistor-Level Diagram of MAX II Device I/O Buffers

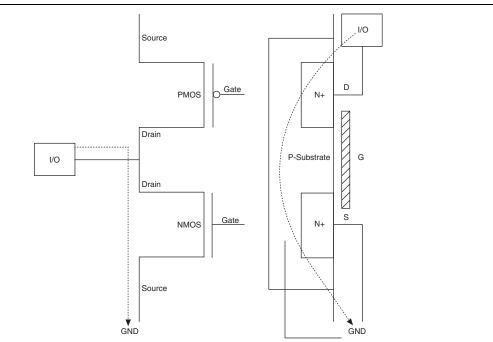

The CMOS output drivers in the I/O pins intrinsically provide electrostatic discharge (ESD) protection. There are two cases to consider for ESD voltage strikes: positive voltage zap and negative voltage zap.

A positive ESD voltage zap occurs when a positive voltage is present on an I/O pin due to an ESD charge event. This can cause the N+ (Drain)/ P-Substrate junction of the N-channel drain to break down and the N+ (Drain)/P-Substrate/N+ (Source) intrinsic bipolar transistor turn on to discharge ESD current from I/O pin to GND. The dashed line (see Figure 4–3) shows the ESD current discharge path during a positive ESD zap.

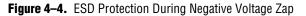

When the I/O pin receives a negative ESD zap at the pin that is less than -0.7 V (0.7 V is the voltage drop across a diode), the intrinsic

P-Substrate/N+ drain diode is forward biased. Therefore, the discharge ESD current path is from GND to the I/O pin, as shown in Figure 4–4.

# **Power-On Reset Circuitry**

MAX II devices have POR circuits to monitor  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels during power-up. The POR circuit monitors these voltages, triggering download from the non-volatile configuration flash memory (CFM) block to the SRAM logic, maintaining tri-state of the I/O pins (with weak pull-up resistors enabled) before and during this process. When the MAX II device enters user mode, the POR circuit releases the I/O pins to user functionality. The POR circuit of the MAX II (except MAX IIZ) device continues to monitor the  $V_{CCINT}$  voltage level to detect a brown-out condition. The POR circuit of the MAX IIZ device does not monitor the  $V_{CCINT}$  voltage level after the device enters into user mode. More details are provided in the following sub-sections.

## **Power-Up Characteristics**

IP

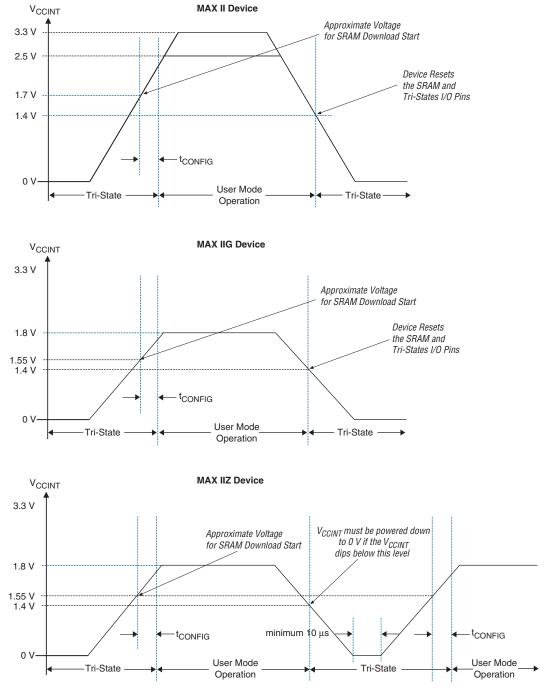

When power is applied to a MAX II device, the POR circuit monitors  $V_{CCINT}$  and begins SRAM download at an approximate voltage of 1.7 V or 1.55 V for MAX IIG and MAX IIZ devices. From this voltage reference, SRAM download and entry into user mode takes 200 to 450 µs maximum, depending on device density. This period of time is specified as  $t_{CONFIG}$  in the power-up timing section of the *DC and Switching Characteristics* chapter in the *MAX II Device Handbook*.

Entry into user mode is gated by whether all  $V_{\text{CCIO}}$  banks are powered with sufficient operating voltage. If  $V_{\text{CCIN}}T$  and  $V_{\text{CCIO}}$  are powered simultaneously, the device enters user mode within the  $t_{\text{CONFIG}}$  specifications. If  $V_{\text{CCIO}}$  is powered more than  $t_{\text{CONFIG}}$  after  $V_{\text{CCINT}}$ , the device does not enter user mode until 2  $\mu$ s after all  $V_{\text{CCIO}}$  banks are powered.

For MAX II and MAX IIG devices, when in user mode, the POR circuitry continues to monitor the  $V_{CCINT}$  (but not  $V_{CCIO}$ ) voltage level to detect a brown-out condition. If there is a  $V_{CCINT}$  voltage sag at or below 1.4 V during user mode, the POR circuit resets the SRAM and tri-states the I/O pins. Once  $V_{CCINT}$  rises back to approximately 1.7 V (or 1.55 V for MAX IIG devices), the SRAM download restarts and the device begins to operate after  $t_{CONFIG}$  time has passed.

For MAX IIZ devices, the POR circuitry does not monitor the V<sub>CCINT</sub> and V<sub>CCIO</sub> voltage levels after the device enters user mode. If there is a V<sub>CCINT</sub> voltage sag below 1.4 V during user mode, the functionality of the device will not be guaranteed and you must power down the V<sub>CCINT</sub> to 0 V for a minimum of 10 µs before powering the V<sub>CCINT</sub> and V<sub>CCIO</sub> up again. Once V<sub>CCINT</sub> rises from 0 V back to approximately 1.55 V, the SRAM download restarts and the device begins to operate after t<sub>CONFIG</sub> time has passed.

Figure 4–5 shows the voltages for POR of MAX II, MAX IIG, and MAX IIZ devices during power-up into user mode and from user mode to power-down or brown-out.

All  $V_{\mbox{\tiny CCINT}}$  and  $V_{\mbox{\tiny CCIO}}$  pins of all banks must be powered on MAX II devices before entering user mode.

#### Notes to Figure 4–5:

(1) Time scale is relative.

(2) Figure 4–5 assumes all  $V_{CCIO}$  banks power up simultaneously with the  $V_{CCINT}$  profile shown. If not,  $t_{CONFIG}$  stretches out until all  $V_{CCIO}$  banks are powered.

After SRAM configuration, all registers in the device are cleared and released into user function before I/O tri-states are released. To release clears after tri-states are released, use the DEV\_CLRn pin option. To hold the tri-states beyond the power-up configuration time, use the DEV\_OE pin option.

# **Referenced Documents**

This chapter refereces the following documents:

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

# **Document Revision History**

Table 4–1 shows the revision history for this chapter.

| Table 4-1. | Document Revision History     |

|------------|-------------------------------|

|            | Boounionenterioronenteriorony |

| Date and Revision             | Changes Made                                                                                                   | Summary of Changes                         |

|-------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| October 2008,<br>version2.1   | <ul> <li>Updated "MAX II Hot-Socketing Specifications" and "Power-On<br/>Reset Circuitry" sections.</li> </ul> | _                                          |

|                               | <ul> <li>Updated New Document Format.</li> </ul>                                                               |                                            |

| December 2007,<br>version 2.0 | <ul> <li>Updated "Hot Socketing Feature Implementation in MAX II<br/>Devices" section.</li> </ul>              | Updated document with MAX IIZ information. |

|                               | <ul> <li>Updated "Power-On Reset Circuitry" section.</li> </ul>                                                |                                            |

|                               | Updated Figure 4–5.                                                                                            |                                            |

|                               | <ul> <li>Added "Referenced Documents" section.</li> </ul>                                                      |                                            |

| December 2006,<br>version 1.5 | <ul> <li>Added document revision history.</li> </ul>                                                           | -                                          |

| February 2006,<br>version 1.4 | <ul> <li>Updated "MAX II Hot-Socketing Specifications" section.</li> </ul>                                     | —                                          |

|                               | <ul> <li>Updated "AC and DC Specifications" section.</li> </ul>                                                |                                            |

|                               | <ul> <li>Updated "Power-On Reset Circuitry" section.</li> </ul>                                                |                                            |

| June 2005,<br>version 1.3     | Updated AC and DC specifications on page 4-2.                                                                  | _                                          |

| December 2004,<br>version 1.2 | <ul> <li>Added content to Power-Up Characteristics section.</li> </ul>                                         | —                                          |

|                               | Updated Figure 4-5.                                                                                            |                                            |

| June 2004,<br>version 1.1     | Corrected Figure 4-2.                                                                                          | _                                          |