# Intel Arria 10 FPGA Remote System Update via PCI Express\* Design Example User Guide

Date: Mar 2021

Revision: 2021.3.26

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

# Contents

| 1. | Overview                                                                                             | 3  |

|----|------------------------------------------------------------------------------------------------------|----|

| 2. | Reference Design Hardware and Software Requirements                                                  | 4  |

|    | 2.1. Hardware Requirements                                                                           | 4  |

|    | 2.2. Software Requirements                                                                           | 4  |

| 3. | Working with the Reference Design                                                                    | 5  |

|    | 3.1. Reference Design Package                                                                        | 5  |

|    | 3.2. Compiling the Factory Design                                                                    | 6  |

|    | 3.3. Compiling the Application 1 Design                                                              | 6  |

|    | 3.4. Compiling the Application 2 Design                                                              | 7  |

|    | 3.5. Creating Raw Programming Data File for Remote System Update via PCIe                            | 8  |

|    | 3.6. Setting Up the Hardware                                                                         | 13 |

|    | 3.6.1 Program the Serial Flash (EPCQL) with JTAG Indirect Configuration File                         | 13 |

|    | 3.7. Installing the Remote System Update via PCIe Design Driver and Running the Application Software | 16 |

|    | 3.7.1. Writing Application Image 1 into the Serial Flash                                             | 16 |

|    | 3.7.2. Writing Application Image 2 into the Serial Flash                                             | 18 |

|    | 3.7.3. Trigger FPGA Reconfiguration                                                                  | 19 |

|    | 3.8 Summary                                                                                          | 20 |

| 4. | Design Description                                                                                   | 21 |

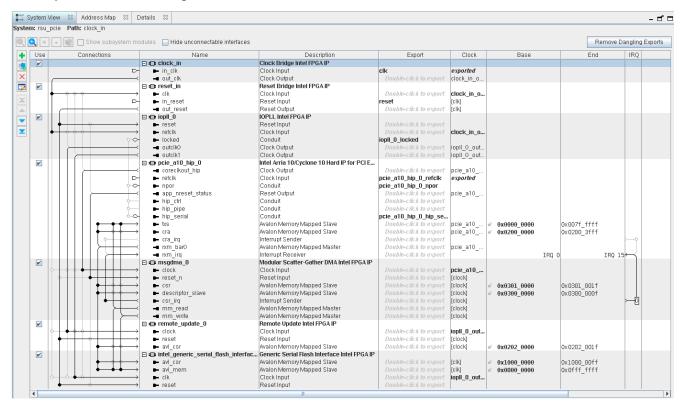

|    | 4.1. Design Components                                                                               | 22 |

|    | 4.1.1. Intel Arria 10 PCIe Gen3 Hard IP                                                              | 22 |

|    | 4.1.2. Modular Scatter-Gather DMA Intel FPGA IP                                                      | 24 |

|    | 4.1.3. Generic Serial Flash Interface Intel FPGA IP                                                  | 25 |

|    | 4.1.4. Remote Update Intel FPGA IP                                                                   | 25 |

| 5. | User Application and Loadable Device Driver                                                          | 26 |

| 6. | Useful APIs                                                                                          | 26 |

| 7. | Document Revision History                                                                            | 27 |

# 1. Overview

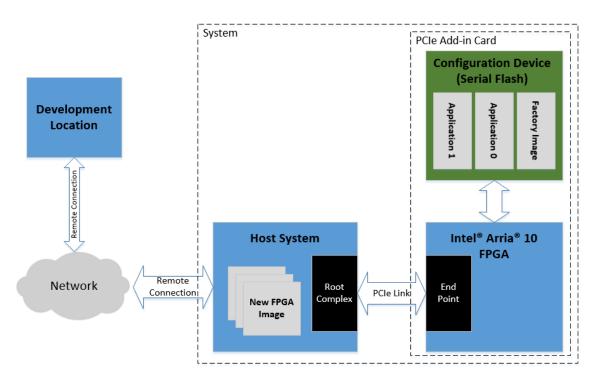

Remote update capability is one of the key advantages of FPGA. It enables deployed systems to be updated with design patches or enhanced capability without recalling. This is a prominent feature to manage remote upgrades of the application configuration images in the configuration device for PCI Express add in card that is designed using FPGA. It helps to reduce time to market and extends product life.

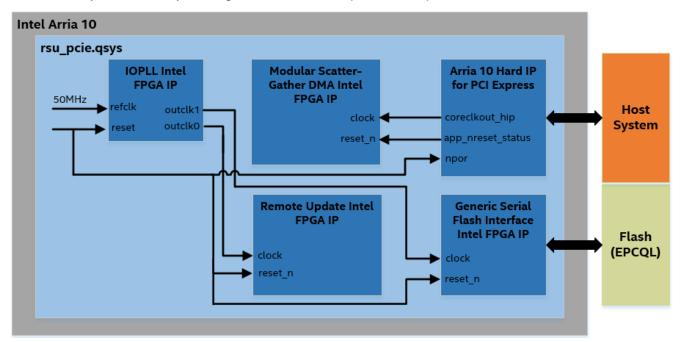

This reference design demonstrates remote system update functionality on Arria<sup>®</sup> 10 FPGA Development Kit using PCI Express as the communication protocol. The configuration image from the host system is received via PCI Express in the Intel<sup>®</sup> Arria 10 device and then written into the serial flash by Modular Scatter-Gather DMA. The reconfiguration process of remote update is controlled by the dedicated remote system upgrade circuitry in the Intel Arria 10 device and manage via PCI Express. When an error occurs, the circuitry detects the error, reverts to a safe configuration image, and provides error status to the design.

A smart host can use the PCI Express protocol and the application topology to update the entire FPGA dynamically without requiring a system power down or host reboot. With a simple software model for configuration, it allows quick update of design for changing application loads.

Figure 1: FPGA Design Image Deployment from Development Site to System Online via Remote System Update

## 2. Reference Design Hardware and Software Requirements

#### 2.1. Hardware Requirements

- 1. Intel Arria 10 GX FPGA Development Kit.

- 2. Micro USB to USB Type A cable for configuring the FPGA device.

- 3. A computer with a PCIe Gen3 x8 or x16 slot running Linux Operating System. CentOS Linux 7.4 64bit was used for this reference design testing.

- 4. A Windows or Linux computer to run Quartus Prime Pro software and configure the Intel Arria 10 GX FPGA Development Kit.

#### 2.2. Software Requirements

- 1. The Linux software driver installed on the Linux computer. The reference design is available in the Intel FPGA Design Store and the Linux software driver is included in the package. Besides, the Intel Quartus Prime Pro Edition Platform Archive File (.par) includes the recommended synthesis, fitter, and timing analysis settings for the parameters specified in the reference designs.

- 2. Quartus Prime Pro software, version 20.4.

#### Related Information

Intel Arria 10 Remote System Update via PCI Express Reference Design Intel Quartus Prime Pro Edition Download Center Intel Arria 10 GX FPGA Development Kit

*Note:* To download this reference designs, first make sure that you have access to the Intel Design Store by logging into Design Store. You can then click on the link provided above to download the design.

# 3. Working with the Reference Design

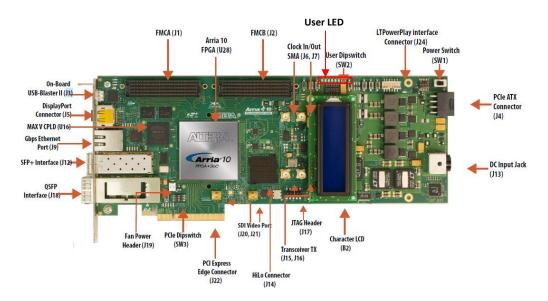

This reference design consists of minimal design components to enable remote system update functionality on Arria 10 FPGA Development Kit through PCI Express interface. The same design will be used to create one factory image and two application images. The difference between these images is the on-board user LED light setting. Factory image will have four red LED lights lit up when loaded, while application image 1 will have one red LED light lit up and application image 2 will have two red LED lights lit up when loaded.

Figure 2: Arria 10 FPGA Development Kit

#### 3.1. Reference Design Package

The reference design uses the following structure:

- top.v The top-level module instantiates rsu\_pcie.

- rsu\_pcie.v Platform Designer top-level files. If you modify the design (rsu\_pcie.qsys) using Platform Designer, you must regenerate the system for the changes to take effect.

The reference design contains the following folders:

- driver contains the Linux driver and software application package, rsu\_over\_pcie\_arria10\_driver.tar.gz

- master\_image constains known working image files for hardware testing

- platform contains the IP and RTL source files

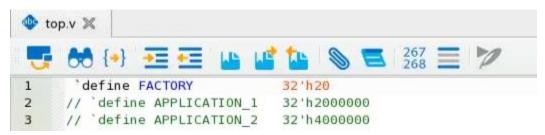

## **3.2. Compiling the Factory Design**

- 1. Download the reference design project archive from Intel FPGA Design Store.

- 2. Launch Quartus Prime Pro software.

- 3. Restore the project by following the instructions on the Intel FPGA Design Store download page with the project folder named as "factory".

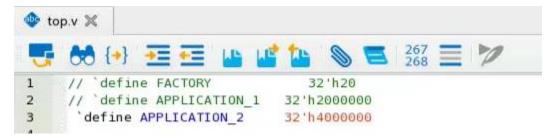

- 4. On the **File** menu of Quartus Prime Pro software, click **Open** button, and select the top.v file in the project directory and click **Open** button.

- 5. At the top part of the top.v file, make sure that the FACTORY definition is uncommented, while APPLICATION\_1 and APPLICATION\_2 definition is commented.

- 6. On the **File** menu, click **Save** to save the modification of top.v file.

- 7. On the **Processing** menu, click **Start Compilation** to run full compile of the design.

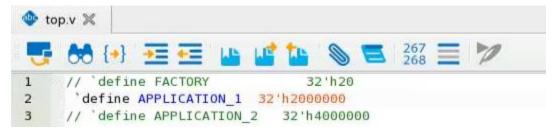

### **3.3. Compiling the Application 1 Design**

- 1. Launch Quartus Prime Pro software.

- 2. Restore the project by following the instructions on the Intel FPGA Design Store download page with the project folder named as "application\_1".

- 3. On the **File** menu of Quartus Prime Pro software, click **Open** button, and select the top.v file in the project directory and click **Open** button.

- 4. At the top part of the top.v file, make sure that the APPLICATION\_1 definition is uncommented, while FACTORY and APPLICATION\_2 definition is commented.

- 5. On the File menu, click Save to save the modification of top.v file.

- 6. On the **Processing** menu, click **Start Compilation** to run full compile of the design.

## **3.4. Compiling the Application 2 Design**

- 1. Launch Quartus Prime Pro software.

- 2. Restore the project by following the instructions on the Intel FPGA Design Store download page with the project folder named as "application\_2".

- 3. On the **File** menu of Quartus Prime Pro software, click **Open** button, and select the top.v file in the project directory and click **Open** button.

- 4. At the top part of the top.v file, make sure that the APPLICATION\_2 definition is uncommented, while FACTORY and APPLICATION\_1 definition is commented.

- 5. On the File menu, click Save to save the modification of top.v file.

- 6. On the Processing menu, click Start Compilation to run full compile of the design.

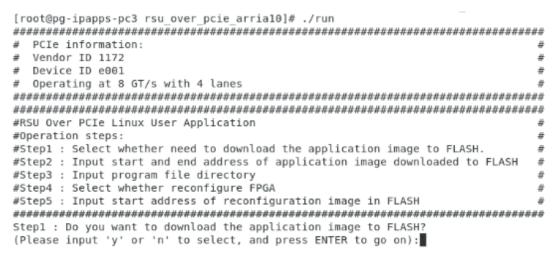

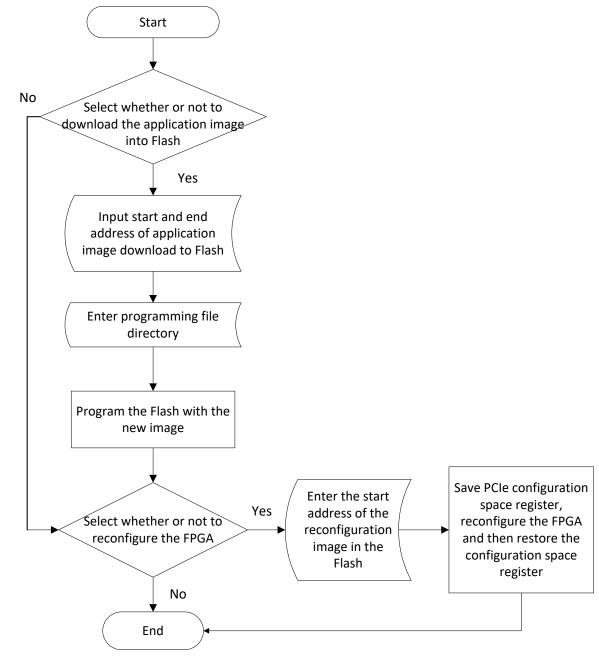

### 3.5. Creating Raw Programming Data File for Remote System Update via PCIe

Raw Programming Data file is a binary file (with the extension .rpd) containing configuration data for use outside the Quartus Prime software. Below are the steps to generate a Raw Programming Data file that contains Factory, Application 1 and Application 2 images using the Convert Programming Files Wizard.

- 1. Launch Quartus Prime Pro software.

- 2. On the **File** menu, click **Convert Programming Files...** to bring up the dialog box as shown in figure below.

| Flash Loader     Add Sof P       SOF Data     Page_0       Add Devic     Add Devic       Remov     Up       Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ile <u>T</u> ools <u>W</u> indow      |                        |                                        |             |               | Search Intel FPGA  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------|----------------------------------------|-------------|---------------|--------------------|--|--|--|

| Open Conversion Setup Data       Save Conversion Setup         utput programming file         Programming file type:       JTAG indirect Configuration File (jic)         Options/Boot info       Configuration device:       EPCQL1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ou can also import inpu<br>iture use. |                        |                                        |             | up informatio | n created here for |  |  |  |

| Programming file type: JTAG indirect Configuration File (jic)           Options/Boot info       Configuration device:       EPCQL1024 <ul> <li>Mode:</li> <li>Active Serial x4</li> </ul> File name:       output_files/rujic <ul> <li>Advanced</li> <li>Remote/Local update difference file:</li> <li>NONE</li> <li>Create Memory Map File (Generate ru_map)</li> <li>Create CvP files (Generate ru_maph), ic and ru core rbf)</li> <li>Create CvP files (Generate ru_auto.rpd)</li> <li>Create Fault injection File (Generate ru_fit)</li> </ul> Add area     Properties     Start Address     Add Go fP           File/Data area         Properties         Start Address         Add Sof P           SOF Data         Page_0 <auto>         Add Devy         Up         Down</auto>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | en Conversion Setup Di | ata                                    |             | Save 0        | onversion Setup    |  |  |  |

| Options/Boot info       Configuration device:       EPCQL1024       Image: Mode:       Active Serial x4         File name:       output_files/ru_jic       Image: Mode:       Active Serial x4         Advanced       Remote/Local update difference file:       MONE       Image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone image: Mone ima | utput programming file                |                        |                                        |             |               |                    |  |  |  |

| File name:       output_files/ru_jic         Advanced       Remote/_ocal update difference file:       MONE         Image: Create Memory Map File (Generate ru_map)       Create CvP files (Generate ru_enup)       Create CvP files (Generate ru_auto.rpd)         Image: Create Fault Injection File (Generate ru_fif)       Image: Create Fault Injection File (Generate ru_fif)         put files to convert       Image: Create Fault Injection File (Generate ru_fif)         File/Data area       Properties         Start Address       Add Jerge         Files Loader       Page_O         SOF Data       Page_O         Image: Create Fault Injection File (Contracte Fault Injectin File (Contracte                                                                                                                                                                                              | Programming file type:                | JTAG Indirect Config   | uration File (.jic)                    |             |               |                    |  |  |  |

| Advanced       Remote/Local update difference file:       NONE         Image: Create Memory Map File (Generate rumap)       Create CvP files (Generate rumap)       Create CvP files (Generate rumap)         Image: Create CvP files (Generate rumap)       Create config data RPD (Generate rumato rpd)       Create Fault Injection File (Generate rumato rpd)         Image: Create Fault Injection File (Generate rumato rpd)       Create Fault Injection File (Generate rumato rpd)       Add Heg I         File/Data area       Properties       Start Address       Add Sof P         Flash Loader       SOF Data       Page_O <auto>         Image: Comparison of the transmitted of the tran</auto>                                                                                                                                         | Options/Boot info                     | Configuration device:  | nfig <u>u</u> ration device: EPCQL1024 |             |               |                    |  |  |  |

| ✓ Create Memory Map File (Generate ru map)         □ Create CVP files (Generate ru periphijc and ru core rbf)         ✓ Create config data RPD (Generate ru_auto.rpd)         □ Create Fault hijection File (Generate ru fif)         put files to convert         File/Data area       Properties         SOF Data       Page_0 <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>       Image: Sof Data         Image: Sof Data       Page: Sof Data         Image: Sof Data</auto></auto></auto></auto></auto></auto></auto>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | File <u>n</u> ame:                    | output_files/ru.jic    |                                        |             |               |                    |  |  |  |

| ☐ Create CvP files (Generate ru_periphijic and ru.core rbf)         ☑ Create config data RPD (Generate ru_auto.rpd)         □ Create Fault hijection File (Generate ru fif)         put files to convert         File/Data area       Properties         SOF Data       Page_0 <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>         Image: Sof Data       Page_0         <auto>       Image: Sof Data         Image: Sof Data       Page_0         Image: Sof Data<th>Advanced</th><td>Remote/Local update</td><td>difference file:</td><td>NONE</td><td></td><td></td></auto></auto></auto></auto></auto></auto></auto></auto></auto></auto>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Advanced                              | Remote/Local update    | difference file:                       | NONE        |               |                    |  |  |  |

| File/Data area     Properties     Start Address     Add Heg D       Flash Loader     SOF Data     Page_0 <auto>       Add Devig     Remov       Up     Down</auto>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | ✓ Create config data   | RPD (Generate ru                       | u_auto.rpd) |               |                    |  |  |  |

| Flash Loader     Add Sof P       SOF Data     Page_0       Add Devic     Add Devic       Remov     Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | out files to convert                  |                        |                                        |             |               |                    |  |  |  |

| SOF Data Page_0 <auto> Add Sof P<br/>Add Devic<br/>Remov<br/>Up</auto>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | File/Data are                         | ea Properti            | es Start Add                           | ress        |               | Add He <u>x</u> Da |  |  |  |

| Remov<br>Up<br>Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       | Page_0                 | <auto></auto>                          |             |               | Add <u>S</u> of Pa |  |  |  |

| Up<br>Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                        |                                        |             |               | Add Device         |  |  |  |

| Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                        |                                        |             |               | Remove             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                        |                                        |             |               |                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                        |                                        |             |               |                    |  |  |  |

| Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                        |                                        |             |               | Up<br>Down         |  |  |  |

- 3. In the dialog box, configure it with the setting as below:

- **Programming file type**: JTAG Indirect Configuration File (.jic)

- Configuration device: EPCQL1024

- Mode: Active Serial x4

- File name: ru.jic

- Check the Create Memory Map File (Generate ru.map) option

- Check the Create config data RPD File (Generate ru\_auto.rpd) option

4. Select the **Flash Loader** and click **Add Device...** button to bring up the dialog box as shown in figure. In the dialog box, select **Arria 10** for **Device family**, **10AX115S2** for **Device name** and then click **OK** button.

| ile <u>T</u> ools <u>W</u> indow                                                                                   | v                                                                                                                                                                       |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          | s                         | earch Int                                       | el FPGA              |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------|----------------------|

| pecify the input file<br>ou can also import<br>uture use.                                                          | Device family                                                                                                                                                           |                                                                  | Select De     | vices (on pg-iccf0307)<br>Device name                                                                                                                                                                                                                                                                                                                                                                                    |                           | ,                                               | <                    |

| onversion setup fi<br>Jutput programmin<br>Programming file :<br>Options/Boot in<br>File <u>n</u> ame:<br>Advanced | APEX20 Arria 10 Arria 10 Arria 13 Arria 13 Arria 14 Arria 16 Arria 16 Arria 16 Arria 10 Cyclone | X<br>Z<br>TO GX<br>TO LP<br>II<br>III<br>III LS<br>IV E<br>IV GX |               | <ul> <li>□ 0AX115R3AA</li> <li>□ 0AX115R3E2</li> <li>□ 10AX115R3E5</li> <li>□ 0AX115R4</li> <li>□ 0AX115R4</li> <li>□ 0AX115R4E3</li> <li>□ 0AX115R4E2</li> <li>□ 0AX115R4E5</li> <li>□ 0AX115R5</li> <li>□ 0AX115S1</li> <li>□ 0AX115S1</li> <li>□ 0AX115S1E2</li> <li>□ 0AX115S1E5</li> <li>□ 0AX11552</li> <li>□ 0AX11552</li> <li>□ 0AX11552</li> <li>□ 0AX11552</li> <li>□ 0AX11552</li> <li>□ 0AX11552A</li> </ul> | Exp<br>Exp<br>Rer<br>Unch | ew.<br>port<br>port<br>dit.<br>move<br>neck All |                      |

| put files to conve                                                                                                 |                                                                                                                                                                         |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           | currect                                         |                      |

| File/Data                                                                                                          | area                                                                                                                                                                    | Properties                                                       | Start Addre   | 55                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |                                                 | Add He <u>x</u> Data |

| Flash Loader<br>SOF Data                                                                                           |                                                                                                                                                                         | Page_0                                                           | <auto></auto> |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                                 | Add Sof Page         |

| SOF Data                                                                                                           |                                                                                                                                                                         | Fage_0                                                           | Sautoz        |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                                 | Add Dev <u>i</u> ce  |

|                                                                                                                    |                                                                                                                                                                         |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                                 | Remove               |

|                                                                                                                    |                                                                                                                                                                         |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                                 |                      |

|                                                                                                                    |                                                                                                                                                                         |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                                 | Down                 |

|                                                                                                                    |                                                                                                                                                                         |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                                 | Properties           |

|                                                                                                                    |                                                                                                                                                                         |                                                                  |               |                                                                                                                                                                                                                                                                                                                                                                                                                          | Generate                  | Close                                           | Help                 |

5. Select the **SOF Data** and click **Add File...** button to locate and add factory image file (.sof).

6. Select the factory image (.sof) file and click on **Properties** button button to bring up the dialog box as shown in figure. In the dialog box, check the **Compression** option and then click **OK** button.

| SOF File Properties: Bitstre                        | eam Encryption (on pg-iccf0307)                                |

|-----------------------------------------------------|----------------------------------------------------------------|

| / Compression                                       |                                                                |

| Enable decompression during Partial Reconfiguration | n The attached SOF does not enable Partial Reconfiguration     |

|                                                     |                                                                |

| I Enable votable semirity key                       |                                                                |

| Generate encryption lock file                       |                                                                |

| Generate key programming file                       |                                                                |

|                                                     |                                                                |

|                                                     | Open Save                                                      |

| Use same file for Key 2                             |                                                                |

|                                                     | Open Save                                                      |

|                                                     |                                                                |

|                                                     |                                                                |

|                                                     | - Add Edit Delete                                              |

|                                                     | + Add Edit Delete                                              |

|                                                     |                                                                |

|                                                     | Off (unless by the OTP fuse option)                            |

|                                                     | Off (unless by the OTP fuse option)                            |

|                                                     | Off (unless by the OTP fuse option)                            |

|                                                     | Off (unless by the OTP fuse option)                            |

|                                                     |                                                                |

| Design Security Feature Disclaimer                  |                                                                |

|                                                     | ▼<br>e read and understand the disclaimer above. (This must be |

| checked to enable bitstream encryption generation.) |                                                                |

|                                                     | <u>O</u> K <u>C</u> ancel                                      |

- 7. Click on Add Sof Page button to add a new Sof Page.

- 8. Select the **SOF Data** of Page\_1 and click **Add File...** button to locate and add application\_1 image file (.sof).

- 9. Select the application image (.sof) file and click on **Properties** button to bring up the dialog box as shown in figure. In the dialog box, check the **Compression** option and then click **OK** button.

- 10. Repeat steps 7 to 9 above to create Sof Page 2.

- 11.Select **SOF Data** of Page\_0 and click **Properties** button to bring up SOF Data Properties dialog box. In the dialog box, configure it with the setting as below and then click **OK** button.

- Address mode for selected pages: Start

- Start address (32-bit hexadecimal): 0x20

- 12. Select SOF Data of Page\_1 and click Properties button to bring up SOF Data Properties dialog box. In the dialog box, configure it with the setting as below and then click **OK** button.

- Address mode for selected pages: Start

- Start address (32-bit hexadecimal): 0x2000000

- 13. Select SOF Data of Page\_2 and click Properties button to bring up SOF Data Properties dialog box. In the dialog box, configure it with the setting as below and then click **OK** button.

- Address mode for selected pages: Start

- Start address (32-bit hexadecimal): 0x4000000

| le <u>T</u> ools <u>W</u> indow                                |                       |                                                                                                                     |              | Search Intel FPGA |

|----------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|--------------|-------------------|

| ou can also import inpu<br>iture use.<br>onversion setup files | it file information f | ype of programming file to generate.<br>From other files and save the conversio<br>SOF Data Properties (or<br>Pages |              | ted here for      |

| utput programming file                                         |                       | 0                                                                                                                   |              |                   |

| Programming file type:                                         | JTAG Indirect         |                                                                                                                     |              |                   |

| Options/Boot info                                              | Configuration d       | 3                                                                                                                   |              | tive Serial x4 -  |

| File name:                                                     | output_files/ru       | □ 4<br>□ 5                                                                                                          |              | -                 |

| Advanced                                                       | Remote/Local u        | Selected pages comment Page_0                                                                                       | *            |                   |

| put files to convert                                           | Create CVP 1          | Address mode for selected pages Start Start Start ddress (32-bit hexadecimal)                                       |              |                   |

| File/Data are                                                  | a Pi                  | ſ                                                                                                                   | OK Cancel    | Add Hex Data      |

| - Flash Loader                                                 |                       | L                                                                                                                   | and a second | Add Sof Page      |

| 10AX11552<br>Boot Info                                         |                       | 0x0000000                                                                                                           |              | Add File          |

| * SOF Data                                                     | Page_                 |                                                                                                                     |              | Remove            |

| top.sof<br>* SOF Data                                          | 10AX<br>Page          | 11552F<br>1 0x02000000                                                                                              |              |                   |

| top.sof                                                        | 100 C 100 C           | 11552F                                                                                                              |              |                   |

| 5OF Data                                                       | Page                  | 0 0x00000020                                                                                                        |              | Down              |

| top.sof                                                        | 10AX                  | 115S2F                                                                                                              |              | Properties        |

14. Finally, the final Convert Programming File dialog configuration should look as shown in figure below, click on the **Generate** button to generate the ru\_auto.rpd file.

| le <u>T</u> ools <u>W</u> indow                    |                                                                                 |                                                           |         |               | Search           | Intel FPGA           |  |

|----------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------|---------|---------------|------------------|----------------------|--|

|                                                    |                                                                                 | of programming file to gen<br>other files and save the co |         | ) information | created here for |                      |  |

| Op                                                 | en Conversion Setup D                                                           | ata                                                       |         | Save Co       | onversion Setup  |                      |  |

| utput programming file                             |                                                                                 |                                                           |         |               |                  |                      |  |

| Programming file type:                             | JTAG Indirect Config                                                            | uration File (.jic)                                       |         |               |                  |                      |  |

| Options/Boot info                                  | Configuration device:                                                           | EPCQL1024                                                 | <u></u> | <u>d</u> ode: | Active Serial x4 | -                    |  |

| File <u>n</u> ame:                                 | output_files/ru.jic                                                             |                                                           |         |               |                  |                      |  |

| Advanced                                           | Remote/Local update                                                             | difference file: NONE                                     |         |               |                  |                      |  |

|                                                    | ✓ Create Memory Ma                                                              | p File (Generate ru.map)                                  |         |               |                  |                      |  |

|                                                    |                                                                                 | enerate ruperiphijic and ru                               |         |               |                  |                      |  |

|                                                    |                                                                                 |                                                           |         |               |                  |                      |  |

|                                                    |                                                                                 | RPD (Generate ru_auto.rp                                  | d)      |               |                  |                      |  |

|                                                    | Create Fault Injection                                                          | on File (Generate ru fif)                                 |         |               |                  |                      |  |

| put files to convert                               |                                                                                 |                                                           |         |               |                  |                      |  |

| File/Data are                                      | a Properti                                                                      | ies Start Address                                         |         |               |                  | Add He <u>x</u> Data |  |

| <ul> <li>Flash Loader<br/>10AX11552</li> </ul>     |                                                                                 |                                                           |         |               |                  | Add <u>S</u> of Page |  |

| BootInfo                                           |                                                                                 | 0x00000000                                                |         |               |                  | Add Device           |  |

| ▼ SOF Data                                         | Page_2                                                                          | 0x04000000                                                |         |               |                  | Remove               |  |

| top.sof 10AX11552F<br>• SOF Data Page 1 0x02000000 |                                                                                 |                                                           |         |               |                  |                      |  |

| top.sof                                            |                                                                                 |                                                           |         |               |                  |                      |  |

|                                                    | Page_0                                                                          | 0x0000020                                                 |         |               |                  | Down                 |  |

| ▼ SOF Data                                         | SOF Data         Page_0         0x00000020           top.sof         10AX115S2F |                                                           |         |               |                  |                      |  |

| ✓ SOF Data                                         | 10AX1155                                                                        | 2F                                                        |         |               |                  | Properties           |  |

## 3.6. Setting Up the Hardware

Figure 3: Hardware Setup

- 1. Plug the Intel Arria 10 GX FPGA Development Kit card into a PCIe slot of the Linux machine that supports Gen3 x8 or Gen3 x16.

- Connect a USB cable from computer of which Quartus Prime Pro software was installed to the Intel Arria 10 GX FPGA Development Kit at J3 (On-Board USB-Blaster II). Otherwise, you can also use an external USB-Blaster II cable to connect the computer to the Intel Arria 10 GX FPGA Development Kit at J17 (JTAG Header).

- 3. To power up Intel Arria 10 GX FPGA Development Kit via the PCIe slot, power on the Linux computer. Alternatively, you can power up FPGA Development Kit using the external power adapter that ships with the kit.

# 3.6.1 Program the Serial Flash (EPCQL) with JTAG Indirect Configuration File

JTAG Indirect Configuration file is a binary file (with the extension .jic) containing serial configuration device data and the serial flash loader device name. Follow the instruction in section 3.5 to create JIC file. It is used to program the configuration data for a into an serial configuration device. The factory image will be loaded by default upon power up. Below are the instructions to program the a serial configuration device with JIC file.

- 1. On computer installed with Quartus Prime Pro software, invoke the Intel Quartus Prime programmer software from the **Tools** menu of Quartus Prime Pro software.

- 2. Click on the **Hardware Setup...** button to bring up bring up the Hardware Setup dialog box. In the dialog box, select USB-BalsterII for the hardware and click **Close** button.

| ardware Setu | No Hardware                  |                |                                   |          |                       |          |                 | Mode:         | JTAG            |          |              | * | Progress: |  |

|--------------|------------------------------|----------------|-----------------------------------|----------|-----------------------|----------|-----------------|---------------|-----------------|----------|--------------|---|-----------|--|

|              | e ISP to allow backgro       | und programmin | g when availabl                   | e        |                       |          |                 | inoue.        | Jind            |          |              |   | riogiess. |  |

| Start        | File                         | Device         | Checksum                          | Usercode | Program/<br>Configure |          | Blank-<br>Check | Examine       | Security<br>Bit |          | ISP<br>CLAMF |   |           |  |

| Stop         |                              |                |                                   |          | rdware Se             |          |                 | (0204)        |                 |          |              |   |           |  |

| o Detect     |                              | ·              |                                   |          | -                     | tup (or  | i pg-icc        | 10294)        |                 |          |              | × |           |  |

| Delete       |                              |                | ware Settings                     | JTAG Set |                       |          |                 |               |                 |          |              |   |           |  |

| id File      |                              |                | t a programmin<br>vare setup appl |          |                       |          |                 |               | This prog       | rammin   | g            |   |           |  |

| nge File     |                              | Curre          | ntly selected h                   | ardware: | USB-Blasterii         | on knga  | -MOBL.g         | ar.corp.intel | .com [USI       | 3-1]     | -            |   |           |  |

| ave File     | Hardware frequency: 24000000 |                |                                   |          |                       |          |                 |               | Hz              | :        |              |   |           |  |

| Device       |                              |                |                                   | v        | Auto-adjus            | t freque | ncy at ch       | ain scanning  |                 |          |              |   |           |  |

| bup.         |                              | Availa         | able hardware i                   | tems     |                       |          |                 |               |                 |          |              |   |           |  |

| Down         |                              |                | rdware                            |          | Server                | Port     |                 |               | Add             | Hardwa   | ire          |   |           |  |

|              |                              | us             | B-Blasteril                       |          | knga                  | USB-1    |                 |               | Remo            | ove Hard | fware        |   |           |  |

|              |                              |                |                                   |          |                       |          |                 |               |                 |          |              |   |           |  |

|              |                              |                |                                   |          |                       |          |                 |               |                 |          |              |   |           |  |

|              |                              |                |                                   |          |                       |          |                 |               |                 |          |              |   |           |  |

|              |                              |                |                                   |          |                       |          |                 |               |                 |          |              |   |           |  |

3. Click on Auto Detect button, select 10AX115S2 device and then click OK button.

| 🚢 Hardware Setup    | USB-Blasteril or  | n knga-MOBL.gar.o | orp.intel.com [ | USB-1]         |                       |           |                 | Mode:       | JTAG            |       |              | * |