## Cyclone 10 LP Remote System Upgrade Design Example User Guide

Date: 8/11/2017

Revision: 1.0

©2017 Intel Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, INTEL, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Intel Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Intel warrants performance of its semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Table of Contents**

| Introduction                                                 | 3  |

|--------------------------------------------------------------|----|

| Requirements                                                 | 3  |

| Theory of Operation                                          | 3  |

| How to Setup the Hardware for Link Test                      | 5  |

| Step.1 Download .par file from design store                  | 6  |

| Step.2 Generate design project and compile the Factory Image | 6  |

| Step.3 Creating JTAG Indirect Configuration File (.jic)      | 8  |

| Step.4 Program FPGA                                          | 10 |

| References                                                   | 12 |

| Revision History                                             | 12 |

### Introduction

This design example demonstrates the ability of Cyclone 10 LP device booting between 2 configuration images by initiating Quartus build-in IP: Altera Remote Update IP. In the first chapter of this User Guide, the design example instructions will walk you through each of the steps to generate this design and eventually loading the 2 configuration images (1 factory image and 1 application image) on your FPGA.

### Requirements

You will need the following hardware and software to implement this design example:

| Quartus Version             | Quartus <sup>®</sup> 17.0 Build 595 Standard Edition |  |  |

|-----------------------------|------------------------------------------------------|--|--|

| IPs                         | Altera Remote Update, ALTPLL                         |  |  |

| Hardware                    | Cyclone 10 LP FPGA Evaluation Kit                    |  |  |

| Device number               | 10CL025YU256I7G                                      |  |  |

| Configuration Device        | EPCQ64                                               |  |  |

| Configuration Scheme (Mode) | Active Serial                                        |  |  |

**NOTE:** A complete RSU design should include at a minimum 2 project files: 1 factory image and 1 application image. These two projects should be compiled separately to generate their own .sof file. However in this particular design example, for ease of use, we are using one project and two top level source files (*factory\_image.v* and *application\_image.v*) which we manually switch to the top entity. For your own design, it is recommended to always have two separate design projects for each image.

### **Theory of Operation**

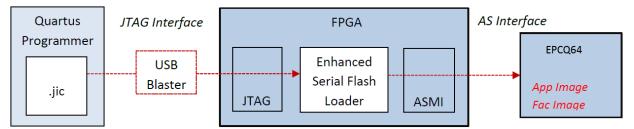

Step 1: Program Your Serial Configuration Device (EPCQ64) with the FPGA Configuration Image

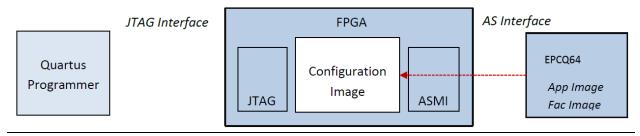

### Step 2: Configure Your FPGA from Your Serial Configuration Device (EPCQ64)

The two images are first generated as SRAM Object Files (.sof) files after compilation and then combined into 1 single Jtag Indirect File (.jic). This .jic file is then loaded to an external flash (EPCQ64 in this case) through the Enhanced Serial Flash Loader (SFL) generated by Quartus Programmer as shown in the above block diagram. In this example, half of the memory resource is divided into half and each store one image. The factory image is Image 0 and the application image is Image 1. On the next power cycle after the 2 images are loaded into flash, the Cyclone 10 LP FPGA will start being configured by images loaded from the EPCQ64.

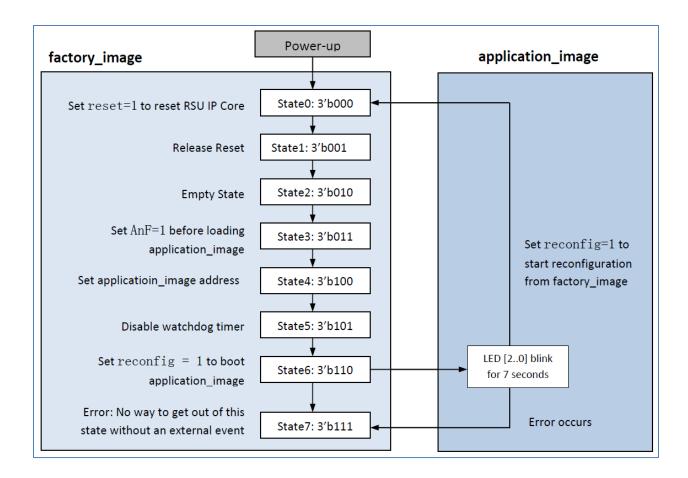

In the factory image, you will see incremental counter at LED 2:0 and LED3 show heartbeat. There is a 7step state machine: State 0 (Reset the remote system update circuitry) -> State 1 (Release the reset) -> State 2 (Empty State) -> State 3 (Set AnF=1) -> State 4 (Set start address for application image) -> State 5 (Disable the watchdog timer) -> State 6 (Boot the application Image) -> State 7 (Hold if error occurs). LED [2...0] is set to be a counter indicating which state the factory image jumps into. LED[3] is set to be a much faster blinking light as a "heartbeat". Once the factory image enters State 6, *reconfig* is set to 1'b1 which triggers the state machine enters the application image.

In the application image, LED [2...0] will keep blinking simultaneously for 7 seconds and then jump back to State 0 in the factory image. The only condition entering State 7 is when an error occurs. Once it enters State 7, there is no way out of this state without an external even although the "heartbeat" LED [3] still blinks indicating the factory image is still working.

### How to Setup the Hardware for Link Test

Follow these steps to setup the hardware to run the reference design:

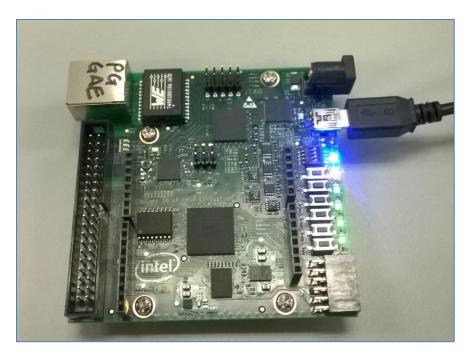

- 1. Connect the USB cable coming together with the Cyclone 10 LP FPGA Evaluation Kit between the PC and the kit as shown in Figure 1

- 2. The USB cable will supply the power as well as establish the JTAG connection with the kit

- To enable RSU feature, make sure SW1.4 set to 1 (move to left side from the view of Figure 1). For more details about default switching settings, please refer to Cyclone 10 LP FPGA Evaluation Kit user guide

- 4. The hardware system is now ready for programming.

Figure 1. Cyclone 10 LP FPGA Evaluation Kit

### Step.1 Download .par file from design store

Download the .par file from design store and save them to your local <destination> folder. (Note: Please rename your local folder <destination> of your own)

# Step.2 Generate design project and compile the Factory Image **Open C10LP\_RSU.par in Quartus**

- I. Follow the guideline on Design Store to load your design as a template.

- II. You can find a more detailed guideline <u>here</u>.

| 🕥 Device and Pin Options - top      |                                                                       |             |                     |                     |                                                |               | ×                                     |

|-------------------------------------|-----------------------------------------------------------------------|-------------|---------------------|---------------------|------------------------------------------------|---------------|---------------------------------------|

| Category:                           |                                                                       |             |                     |                     |                                                |               |                                       |

| General                             | Configuration                                                         |             |                     |                     |                                                |               |                                       |

| Configuration                       | Specify the device configuration scheme and the configuration device. |             |                     |                     |                                                |               |                                       |

| Programming Files<br>Unused Pins    | Configuration scheme: Active Serial (can use Configuration Device)    |             |                     |                     | •                                              |               |                                       |

| Dual-Purpose Pins                   |                                                                       |             |                     |                     | •                                              |               |                                       |

| Capacitive Loading                  | Configuration mode: Remote                                            |             |                     |                     |                                                |               |                                       |

| Board Trace Model                   | Configuration device                                                  |             |                     |                     |                                                |               |                                       |

| Voltage                             | Use configuration d                                                   | levice:     | EPCQ64              |                     |                                                |               | •                                     |

| Pin Placement                       | -                                                                     |             |                     | Configuration De    | evice Optio                                    | ns            |                                       |

| Error Detection CRC<br>CvP Settings | Configuration device I/                                               | O voltage:  | Auto                |                     |                                                |               | •                                     |

| Partial Reconfiguration             | Force VCCIO to be o                                                   | ompatible   | with configuration  | I/O voltage         |                                                |               |                                       |

|                                     | VID Operation mode                                                    |             |                     |                     |                                                |               | ~                                     |

|                                     | -                                                                     |             |                     |                     | <i>c</i> , , , , , , , , , , , , , , , , , , , |               |                                       |

|                                     | Configuration pin:                                                    |             |                     | Cont                | figuration P                                   | Pin Options   |                                       |

|                                     | Generate compressed                                                   | l bitstream | 5                   |                     |                                                |               |                                       |

|                                     | Active serial clock source                                            | 2:          |                     |                     |                                                |               | ~                                     |

|                                     | Enable input tri-state                                                | on active o | configuration pins  | in user mode        |                                                |               |                                       |

|                                     | Description:                                                          |             |                     |                     |                                                |               |                                       |

|                                     | The method used to loa                                                | d data into | the device. Up to t | three configuration | on schemes                                     | are available |                                       |

|                                     | depending on the select                                               |             |                     | -                   |                                                |               | · · · · · · · · · · · · · · · · · · · |

|                                     |                                                                       |             |                     |                     |                                                |               |                                       |

|                                     |                                                                       |             |                     |                     |                                                |               |                                       |

|                                     |                                                                       |             |                     |                     |                                                |               | Reset                                 |

|                                     |                                                                       |             |                     |                     | ОК                                             | Cancel        | Help                                  |

### **Configuration settings in Device and Pin Options**

In the upper left Project navigator window, double click the Compilation Hierarchy title "Cyclone 10 LP: 10CL025YU256I7G" and In the Device panel, click Device and Pin Options.

- In the Device and Pin Options panel, select the correct settings.

Configuration Scheme – Active Serial

Configuration Mode – Remote

Configuration Device – EPCQ64

### Compile and rename the SRAM Object File

- a. Generate design project and compile factory image.

- Replace the Top-level Entity with factory\_image.v

- ✓ In Project navigator window, under "Files", right click "source/factory\_image.v" and and set as Top-Level Entity

- Click "Start Compilation".

- After the design is compiled successfully, go to <destination>/output\_files, there should be a SRAM Object File top.sof generated in the folder. Change the name to factory\_image.sof.

- b. Generate design project and compile Application Image

- Replace the Top-level Entity with application\_image.v

- ✓ In Project navigator window, under "Files", double click "Files".

- ✓ In the Settings window, delete factory\_image.v and add application\_image.v (<destination>/source/application\_image.v).

- ✓ After application\_image.v is added in Project Navigator, right click "source/ application\_image.v" and set as Top-Level Entity.

- Compile and rename the SRAM Object File to application\_image.sof

- ✓ Click "Start Compilation"

- ✓ After the design is compiled successfully, go to <destination>/output\_files, change the name of top.sof to application\_image.sof

### Step.3 Creating JTAG Indirect Configuration File (.jic)

- a. Open Convert Programming File GUI

- In Quartus, click File > Convert Programming Files.

- b. Select Programming Type

- Select "JTAG Indirect Configuration File (.jic)" as programming file type.

- c. Select Configuration Device and Mode

- Select "EPCQ64" as Configuration Device and select "Active Serial" mode.

- Locate your .jic file under <destination> folder and rename it if necessary.

- d. Add Flash Loader

- Under Flash Loader section, select "Flash Loader" and click "Add device" on the right.

- In this example, we chose "10CL025Y".

| Select Devices  |   |             | ×           |

|-----------------|---|-------------|-------------|

| Device family   |   | Device name |             |

| АРЕХ20К         | ^ | 10CL006Y    | ^ New       |

| Arria 10        |   | 10CL006Z    | Import      |

| Arria GX        |   | 10CL010Y    | Import      |

| 🗆 Arria II GX   |   | 10CL010Z    | Export      |

| 🗆 Arria II GZ   |   | 10CL016Y    |             |

| 🗆 Arria V       |   | 10CL016Z    | Edit        |

| 🗆 Arria V GZ    |   | 10CL025Y    | Demovie     |

| Cyclone         |   | 10CL025Z    | Remove      |

| 🗹 Cyclone 10 LP |   | 10CL040Y    | Uncheck All |

| Cyclone II      |   | 10CL040Z    |             |

| Cyclone III     |   | 10CL055Y    |             |

| Cyclone III LS  |   | 10CL055Z    |             |

| Cyclone IV E    |   | 10CL080Y    |             |

| Cyclone IV GX   | ~ | 10CL080Z    | ~           |

|                 |   |             |             |

|                 |   |             | OK Cancel   |

- e. Add Page 0: factory\_image.sof

- Select "SOF Data (Page\_0)" and click "Add File".

- Locate to <destination> folder where restores factory\_image.sof generated in Step.2.

- There should be "factory\_image.sof (10CL025YU256)" added under "SOF Data (Page\_0)".

- Select "SOF Data (Page\_0)" and click "Properties".

- In the new window, select "Block" under Address mode for selected pages.

- Enter "0x00000000" as start address (corresponding to the start address of sector 0).

- Enter "0x003FFFFF" as end address (corresponding to the end address of sector 63).

- Click OK to close "SOF Data Properties" window.

- Select "factory\_image.sof (10CL025YU256)" and click "Properties".

- Check "Compression" box on the top left corner and click OK.

- f. Add Page 1: application\_image.sof

- Click "Add Sof Page" to create a new page.

- Select "SOF Data (Page\_1)" and click "Add File".

- Locate to <destination> folder where restores application\_image.sof generated in Step.3.

- There should be "application\_image.sof (10CL025YU256)" added under "SOF Data (Page\_0)".

- Select "SOF Data (Page\_1)" and click "Properties".

- In the new window, select "Block" under Address mode for selected pages.

- Enter "0x00400000" as start address (corresponding to the start address of sector 64).

- Enter "0x007FFFFFF" as end address (corresponding to the end address of sector 127).

- Click OK to close "SOF Data Properties" window.

- Select "application\_image.sof (10CL025YU256)" and click "Properties".

- Check "Compression" box on the top left corner and click OK.

- g. Generate .jic file and check Memory Map File (.map)

- Click "Generate" close the Converting Programming Files GUI window.

- Now in your <destination> folder, you can find your .map file along with your .jic file.

- Open the .map file and it should look like this:

| BLOCK                                                                                                                        | START ADDRESS            | END ADI | DRESS                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|------------------------------|--|--|--|

| Page_0<br>Page_1                                                                                                             | 0x00000000<br>0x00400000 |         | (0x000328C8)<br>(0x00432485) |  |  |  |

| Configuration device: 10CL025Y<br>Configuration mode: Active Serial<br>Quad-Serial configuration device dummy clock cycle: 8 |                          |         |                              |  |  |  |

**<u>TIPS</u>**: You can always open .map file to check whether your programming files are converted correctly.

### Step.4 Program FPGA

- a. Auto Detect JTAG Chain

- In Quartus, click Tools > Programmer.

- Click "Hardware Setup" on the top left corner and select "USB-BlasterII[USB-1]" and close

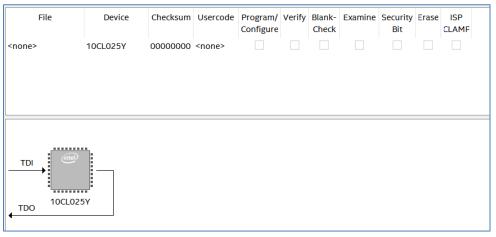

- Click "Auto Detect" and choose the corresponding device number. In this example, please select "10CL025Y". A JTAG chain should be generated successfully shown as below.

- Select " <none> 10CL025Y 00000000 <none>" and click "Change File"

- Locate the .jic file you generated in Step.4.

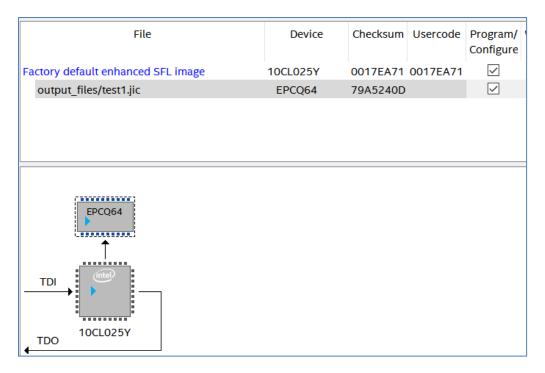

- Then you can see it changed to configuration as below. Tick the Program/Configure box.

- Click Start to program.

**NOTE**: the "Progress" Bar on the top right indicates the percentage of your configuration status. If you are careful enough, you will notice the bar will go from 0% to 100% very quickly in about 5 seconds and then goes back to 0% and start a much slower 2nd stage of process which takes around 60 seconds. The first stage indicates the Enhanced Serial Flash Loader (SFL) inside your targeted FPGA (In this example: Cyclone 10 LP) is loaded successfully. The 2nd slower stage you observe indicates the .jic file loading from the Quartus Programmer to your Flash Device (In this example: EPCQ64) through the Enhanced SFL which was just loaded successfully in the 1st Stage.

- After progress bar shows "100% (Successfully)", power cycle the board.

- After a power cycle, the factory image in the EPCQ64 will be loaded in FPGA.

- b. LED Observations

- By powering up the board, you should able be see the 4 LEDs blinking:

- LED[2...0] are counters indicating the current stage.

- LED[3] is the "heartbeat" which will blink until state machine enters application image.

- When only LED[3] is blinking and LED [2...0] are all off, this means it enters Error Stage.

**NOTE**: The state machine will start from factory image then enter application image. After it enters the application image, LED[2...0] will blink simultaneously for around 7 seconds indicating the application image is loaded successfully after which it will revert to the factory image, starting the cycle all over again. A successful LED observation will be jumping back and forth between factory image and application image. Please see the diagram below.

| State # (LED [20]) | Functions                           |    |   |   |   | Image Status      |

|--------------------|-------------------------------------|----|---|---|---|-------------------|

| State 0 (3'b000)   | reset =1, reset RSU IP              | N. | 1 |   |   |                   |

| State 1 (3'b001)   | release reset                       | 10 | 8 |   |   |                   |

| State 2 (3'b010)   | empty state                         | 1  | 1 |   |   |                   |

| State 3 (3'b011)   | AnF=1                               |    | 1 |   |   | factory Image     |

| State 4 (3'b100)   | Set application_image start address | 1  |   |   |   | factory_Image     |

| State 5 (3'b101)   | disable watchdog                    | 2  |   |   |   |                   |

| State 6 (3'b110)   | reconfig=1, boot application Image  | 10 |   |   |   |                   |

|                    | LED[20] blink for 7 seconds         |    |   | 2 | * | application_image |

| State 7 (default)  | Hold                                |    |   |   |   | Error             |

### References

Quad-Serial Configuration (EPCQ) Device Datasheet

https://www.altera.com/en\_US/pdfs/literature/hb/cfg/cfg\_cf52012.pdf

Altera Remote Update IP Core User Guide

https://www.altera.com/en\_US/pdfs/literature/ug/ug\_altremote.pdf

### **Revision History**

| Date            | Version | Changes         |

|-----------------|---------|-----------------|

| August 11, 2017 | 1.0     | Initial Release |