INTEL® IN-MEMORY ANALYTICS ACCELERATOR (INTEL® IAA) ARCHITECTURE SPECIFICATION

> Document ID: 60941 Revision: 03 August 2023

#### **Notices & Disclaimers**

Intel technologies may require enabled hardware, software or service activation. No product or component can be absolutely secure.

Your costs and results may vary.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes the subject matter disclosed herein.

All product plans and roadmaps are subject to change without notice.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document, with the sole exception that a) you may publish an unmodified copy and b) code included in this document is licensed subject to the Zero-Clause BSD open source license (OBSD), https://opensource.org/licenses/OBSD. You may create software implementations based on this document and in compliance with the foregoing that are intended to execute on the Intel product(s) referenced in this document. No rights are granted to create modifications or derivatives of this document.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

# **Revision History**

| Date          | Revision Description                                                                                                                                                                                 |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| April 2022    | The initial release of the document.                                                                                                                                                                 |  |

| December 2022 | First revision and refinement of content.                                                                                                                                                            |  |

| April 2023    | <ul> <li>Removed "Intel Confidential" from header.</li> <li>Changed Metadata: added Intel Corp as author, added keywords and summary.</li> <li>Removed duplicated section from Chapter 6.</li> </ul> |  |

| August 2023   | Added discussions of index table and decompression on bit-boundaries.                                                                                                                                |  |

# Glossary

| Acronym | Term                                          | Description                                                                                                                                                                                                        |

|---------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AECS    | Analytics Engine Configuration and State      | A data structure used to pass configuration data that did not fit into the descriptor to the accelerator, and to pass state information between descriptor executions when a job consists of multiple descriptors. |

| DSA     | Intel <sup>®</sup> Data Streaming Accelerator | Intel Accelerator designed to accelerate streaming operations such as memory copy and others.                                                                                                                      |

| QPL     | Intel <sup>®</sup> Query Processing Library   | Intel library to interface between applications and the hardware.                                                                                                                                                  |

#### **Table of Contents** 1.1 12 2 2.1 3 Intel<sup>®</sup> Analytics Accelerator Architecture......12 3.1 3.2 3.2.1 3.3 3.3.1 3.3.2 3.3.3 3.4 3.4.1 3.4.2 3.4.3 3.4.4 3.4.5 3.4.6 3.4.7 3.5 3.5.1 3.5.2 3.5.3 3.5.4 3.6 3.7 3.8 3.8.1 3.8.2 3.8.3 3.9 3.10 3.10.1 3.10.2 3.10.3 3.10.4 3.10.5 3.10.6 3.10.7 4.1 4.2 4.3

|   | 4.4            | Error Codes                                              | . 36 |

|---|----------------|----------------------------------------------------------|------|

|   | 4.4.1          | Operation Status Codes                                   | 36   |

|   | 4.4.2          | •                                                        |      |

| - | 6 - 44         | ware Architecture                                        |      |

| 5 | 5010           |                                                          |      |

|   | 5.1            | Intel® Query Processing Library                          |      |

| 6 | Stru           | cture Formats                                            | 40   |

|   | 6.1            | Descriptor                                               | . 40 |

|   | 6.1.1          | Trusted Fields                                           | . 40 |

|   | 6.1.2          | Operation                                                | 41   |

|   | 6.1.3          | Operation Flags                                          |      |

|   | 6.1.4          | Completion Record Address                                | 44   |

|   | 6.1.5          | Source 1 Address                                         | . 44 |

|   | 6.1.6          | Destination Address                                      | . 45 |

|   | 6.1.7          | Source 1 Transfer Size                                   | . 45 |

|   | 6.1.8          | Completion Interrupt Handle                              |      |

|   | 6.1.9          | Source 2 Address                                         |      |

|   | 6.1.1          |                                                          |      |

|   | 6.1.1          | 1 Source 2 Transfer Size                                 | . 46 |

|   | 6.2            | Completion Record                                        | 47   |

|   | 6 2 1          | Status                                                   |      |

|   | 6.2.1<br>6.2.2 | Status<br>Error Code                                     |      |

|   | 6.2.2          | Fault Info                                               |      |

|   | 6.2.4          |                                                          |      |

|   | 6.2.5          | Fault Address                                            |      |

|   | 6.2.6          | Invalid Flags                                            |      |

|   | 6.2.7          | Output Size                                              |      |

|   | 6.2.8          | •                                                        |      |

|   | 6.2.9          | XOR Checksum                                             |      |

|   | 6.2.1          |                                                          |      |

|   | 6.2.1          |                                                          |      |

|   | 6.2.1          |                                                          |      |

|   | 6.3            | Descriptor Types                                         |      |

|   |                |                                                          |      |

|   | 6.3.1          |                                                          |      |

|   | 6.3.2          | Decompress Descriptor (0x42)                             |      |

|   | 6.3.3          | Analytics Descriptor (0x50, 0x52, 0x53, 0x56)            |      |

|   | 6.3.4          | Decrypt/Encrypt Descriptor (0x40, 0x41)                  |      |

|   | 6.3.5          | Compress Descriptor (0x43)<br>CRC64 Descriptor (0x44)    |      |

|   | 6.3.6          |                                                          |      |

|   | 6.4            | Analytics Engine Configuration and State                 | . 62 |

|   | 6.4.1          | AECS Format for Encrypt, Decrypt, Decompress, and Filter |      |

|   | 6.4.2          | AECS Format for Compress                                 | . 67 |

| 7 | Sum            | mary of Differences from Intel® DSA                      | 69   |

|   | 7.1            | General Differences                                      | . 69 |

|   | 7.2            | Configuration and Control Register Differences           |      |

|   |                |                                                          |      |

|   | 7.2.1          | General Capabilities Register (GENCAP)                   |      |

|   | 7.2.2          |                                                          |      |

|   | 7.3            | PCI Express (PCIe) Configuration Register Differences    | 72   |

| 7.3.1 | Device ID (DID)                               | . 72 |

|-------|-----------------------------------------------|------|

| 7.3.2 | Outstanding Page Request Capacity (PRSREQCAP) | .72  |

# **List of Tables**

| 9  |

|----|

| 12 |

| 13 |

| 13 |

| 18 |

| 19 |

| 24 |

| 29 |

| 32 |

| 33 |

| 34 |

| 34 |

| 35 |

| 36 |

| 36 |

| 37 |

| 40 |

| 41 |

| 42 |

| 46 |

| 47 |

| 48 |

| 50 |

| 51 |

| 53 |

| 54 |

| 56 |

| 57 |

| 59 |

| 60 |

| 62 |

| 63 |

| 64 |

| 65 |

| 66 |

| 67 |

| 67 |

| 68 |

| 70 |

| 70 |

|    |

# List of Figures

| Figure 2-1 Intel® Analytics Accelerator                     | 10 |

|-------------------------------------------------------------|----|

| Figure 3-1: Index Arrangement for Single Block Usage        | 15 |

| Figure 3-2: Index Arrangement for Multiple Block Usage      | 15 |

| Figure 3-3 GCM Calculations                                 |    |

| Figure 6-1 Generic Intel <sup>®</sup> IAA Descriptor Format | 40 |

| Figure 6-2 Intel® IAA Completion Record Format              |    |

| Figure 6-3 Decompress Descriptor                            | 51 |

| Figure 6-4 Analytics Descriptor                             | 53 |

| Figure 6-5 Decrypt/Encrypt Descriptor                       | 56 |

| Figure 6-6 Compress Descriptor                              | 57 |

| Figure 6-7 CRC-64 Descriptor                                | 60 |

| Figure 6-8 CRC-64 Completion Record                         |    |

# **1 INTRODUCTION**

The Intel<sup>®</sup> In-Memory Analytics Accelerator (Intel<sup>®</sup> IAA) is a hardware accelerator that provides very high throughput compression and decompression combined with primitive analytic functions.

The Intel<sup>®</sup> Data Streaming Accelerator (Intel<sup>®</sup> DSA) is a data mover and transformation accelerator. Intel IAA and Intel DSA share the same hardware/software and programming interface. This document describes the Intel IAA-specific functionality and the minor differences in interface from the base Intel DSA specification. One should refer to the Intel Data Streaming Accelerator Architecture specification for details on the common elements.

## **1.1 Audience**

The intended audience for this specification includes hardware engineers and SoC architects to build the hardware implementation, device driver software developers to program the device, virtualization software providers to efficiently enable sharing and virtualization of the device, and application or library developers utilizing accelerator operations.

It is assumed that the reader is already familiar with the Intel Data Streaming Accelerator (Intel DSA) architecture.

# **1.2** References

# Table 1-1 References

| Intel® Data Streaming Accelerator Architecture Specification                     |

|----------------------------------------------------------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manuals                   |

| Intel® Architecture Instruction Set Extensions Programming Reference             |

| Intel® Query Processing Library                                                  |

| PCI Express* Base Specification 4.0                                              |

| Intel® Virtualization Technology for Directed I/O Specification                  |

| Intel® Scalable I/O Virtualization Technical Specification                       |

| Intel® I/O Acceleration Technology                                               |

| ITU-T Series V: Data Communication Over the Telephone Network Error Control V.42 |

| RFC 1951, Deflate Compressed Data Format Specification                           |

| RFC 3720, Internet Small Computer Systems Interface                              |

# 2 OVERVIEW

The Intel<sup>®</sup> In-Memory Analytics Accelerator (Intel<sup>®</sup> IAA) is a hardware accelerator that provides very high throughput compression and decompression combined with analytics primitive functions. The analytic functions are commonly used for filtering data during analytic query processing. It primarily targets applications such as big-data and in-memory analytics databases, as well as application-transparent usages such as memory page compression. Other operations, such as data integrity functions (e.g., CRC64), are also supported. The device supports formats such as Huffman encoding and Deflate. For the Deflate format, it supports indexing the compressed stream for efficient random access.

# 2.1 Data Analytics Features

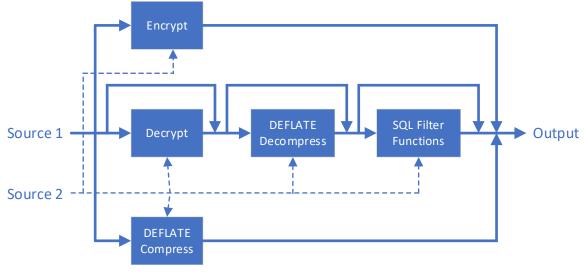

The accelerator logically contains three main functional blocks: Compression, Encryption, and Analytics. The Analytics pipe contains three sub-blocks: Decrypt, Decompress, and Filter. These functions are tied together so each analytics operation can perform any combination of decrypt/decompress/filter (e.g., decrypt-filter), as illustrated in Figure 2-1. Alternatively, one can compress or encrypt the input. Compression and Encryption cannot be linked with any other operations.

Not all of the functional blocks and features are available on all versions of the accelerator. The availability of these blocks and features are conveyed through the capability registers, in particular OPCAP, GENCAP (Section 7.2.1), and IAACAP (Section 7.2.2). Software should consult these registers before using a capability described by one of these registers.

The accelerator allows storing columnar databases in compressed form, decreasing memory footprint. In addition to increased effective memory capacity, this also reduces memory bandwidth by performing the filter function used for database queries "on the fly," thereby avoiding the use of memory bandwidth for uncompressed raw data transfer.

Figure 2-1 Intel<sup>®</sup> Analytics Accelerator

The device supports decompression compatible with the Deflate compression standard described in RFC 1951. The uncompressed data may be written directly to memory or passed to the input of the filter function. Decompression is supported for Deflate streams where the size of the history buffer is no more than 4096 bytes.

It also supports Deflate compression, along with the calculation of arbitrary CRCs.

Intel IAA encryption/decryption supports the following algorithms: GCM-AES128 (GCM with 128-bit keys), GCM-AES256, CFB-AES128, CFB-AES256, XTS-AES128, and XTS-AES256.

The SQL filter function block takes one or two input streams, a primary input, and in some cases, a secondary input. The primary input may be read from memory or received from the decompression or decryption block. If used, the secondary input is always read from memory. The data streams logically contain an array of unsigned values; however, they may be

formatted in any of several ways, e.g., as a packed array. If the bit-width of the values is 1, the stream will be referenced as a "bit-vector"; otherwise, it will be referenced as an "array."

The output of the filter function may be either an array or a bit vector, depending on the function.

In addition to generating output data, the device computes a 32-bit CRC and an XOR checksum of the data stream. See Section 3.6 for details. It also computes several "aggregates" of the output data. The CRC, XOR checksum, and aggregates are written to the completion record.

# **3 INTEL® ANALYTICS ACCELERATOR ARCHITECTURE**

# 3.1 Operations Overview

The accelerator supports data operations listed below, further detailed in the following sections.

| Туре       | Operation         | Description                                               |  |

|------------|-------------------|-----------------------------------------------------------|--|

| Decompress | Decompress        | Decompresses input data.                                  |  |

| Compress   | Compress          | Compresses input data.                                    |  |

| Decrypt    | Decrypt           | Decrypts input data.                                      |  |

| Encrypt    | Encrypt           | Encrypts input data.                                      |  |

| E'lles a   | Scan              | Computes a bit-mask of which entries satisfy a condition. |  |

|            | Extract           | Returns entries as specified by a range of entry indices. |  |

| Filter     | Select            | Returns entries as specified by a bit-mask.               |  |

|            | Expand            | Inserts zeros as specified by a bit-mask.                 |  |

| CRC        | CRC64             | Computes an arbitrary CRC up to 64-bits in size.          |  |

| Memory     | Translation Fetch | Prefetches address translations.                          |  |

#### **Table 3-1 Supported Data Operations**

The analytics pipeline consists of three stages:

- 1. Decrypt

- 2. Decompress

- 3. Filter, CRC64

In general, any non-empty subset of these operations can be performed in this order. All other operations must be done individually.

The paradigm for configuring the decrypt/decompress/filter pipeline is that the opcode specifies the last operation to be performed, and earlier operations are enabled via flag bits. For example, if any filter operation is to be performed, the opcode specifies the filter operation and flag bits indicate whether decrypt and/or decompress is to be done. If decompression but no filter operation is to be performed, the decompress opcode is used. Only if decrypt is to be performed with no decompress and no filter operation is the decrypt opcode used.

# 3.2 Analytics Engine Configuration and State

The analytics engine configuration and state (AECS) structure contains configuration information used to control the behavior of the various functions. Details of this structure are in Section 6.4. In addition to configuration information, the AECS may contain internal state of the analytics engine. The state information can be used to initialize the engine to a known state and to propagate state information from one operation to another. For each operation, the AECS may be read or written or both, depending on flags in the descriptor, as described in Section 6.1.3

When Source 2 Address and Source 2 Size are being used to read and/or write the AECS, then the actual memory being referenced will be twice the specified size. The read will occur from one half of the area, and the write will occur to the other half. In this way, the input data will not get overwritten by the output data, so that in the event of an error, the request can be retried by software. The AECS R/W Toggle Selector bit in the Operations Flags field of the descriptor indicates which half supplies the read data, and which half receives the write data.

In particular, if the AECS address (i.e., Source 2 Address) is "A," and the AECS size (i.e., Source 2 Transfer Size) is "S," then in one case the AECS is read from (A) and written to (A+S), and in the other case it is read from (A+S) and written to (A). Note that the total amount of memory accessed would be in general (2S).

Note that in some cases the AECS may be read but not written or written but not read. In either of these cases, the address used for the read or the write is the same as if there was both a read and a write happening. For example, if the AECS was being read but not written, and the AECS R/W Toggle Selector was 1, then the AECS would be read from (A+S) and nothing would be written to (A).

The Source 2 buffer cannot overlap the Source 1 buffer or the Destination buffer. If Source 2 contains AECS data, then the size of the Source 2 buffer for the purposes of the overlap check is twice the Source 2 Transfer Size. This is true regardless of whether it is being read, written, or both. For example, if Source 2 is being read as AECS and not written, so that it is only referencing the first half, then it is still required that the Source 1 and Destination buffers do not overlap either half of the doubled AECS buffer, even though the second half is not being used.

Depending on the operation, some portions of the nominal AECS may not be relevant and do not need to be read/written. Normally, the AECS is read from the beginning so that the Source 2 Size determines how much of the data at the end of the AECS is omitted.

Additionally, if decompression is enabled and Source 2 is being read as AECS (not written), the Load Partial flag bit in the Decompression Flags can be set (see Section 6.3.2.1). This causes the AECS data that is read to be interpreted as if they were preceded by 448 bytes of 0x00. In other words, the fields in the AECS that fall within the first 448 bytes take their default value of 0, and the fields starting at an offset of 448 are initialized with the data read from Source 2. This can be used for certain decompress operations where the earlier portion of the AECS contains no useful data, and where one is trying to minimize the amount of data read from Source 2 so as to minimize the decompress latency. An example would be when decompressing small pages with "canned" Deflate headers. The headers would be pre-parsed so that the actual compression operation would only want to load the Huffman Tables.

In general, the Source 2 data (for AECS) would contain the AECS data starting at either 0 or 448 and continuing to next multiple of 32 after the last bit of required data. This means that the size of Source 2 will depend on the operation. Some typical sizes (assuming the data starts at an offset of 0) are given in Table 3-2.

| Operation                     | AECS Size                                            |

|-------------------------------|------------------------------------------------------|

| Filter                        | 32                                                   |

| Encrypt/Decrypt               | 192                                                  |

| Decompress for Indexing       | 1088 (for AECS Format 1)<br>1248 (for AECS Format 2) |

| Decompress                    | 5376                                                 |

| Compress (With Huffman Table) | 1568                                                 |

#### Table 3-2 AECS Sizes for Various Operations

The amount of AECS data written back to the Source 2 buffer (if writing is enabled) is generally the smaller of the nominal size and the specified size. In other words, it will never write more than the nominal size and it will never write more than the specified size. The nominal sizes are given in Table 3-3.

| Table 3-3 | Nominal | AECS | Write Sizes |

|-----------|---------|------|-------------|

|-----------|---------|------|-------------|

| Condition                                           | Nominal Size |

|-----------------------------------------------------|--------------|

| Decompress                                          | 5376         |

| Compress with Write AECS Huffman Tables Flag set    | 1568         |

| Compress without Write AECS Huffman Tables Flag set | 64           |

## 3.2.1 AECS Format

There are two different formats for the decompress/analytics AECS. This reflects a change in the microarchitecture of the decompression engine after the first generation. There are some format fields in the AECS that indicate which format the data is in. If an AECS in the wrong format is read by the accelerator, the processing terminates with an error.

The appropriate AECS Format is indicated by IAACAP bit 0 (see Section 7.2.2).

This only applies to the AECS for decompress/analytics/crypto. It does not apply to the AECS for compression.

At byte offset 0x1DD there is a 3-bit AECS Format Number. The low order bit in the "Output Bits Valid" field (i.e. at offset 0xB0) is the AECS Format Valid bit. If the Format Valid bit is 0, then the Format Number is reserved.

In Format-1, both of these values must be 0, and in Format-2, both of these values must be 1. See Section 6.4.1.

- If an accelerator expecting a Format-1 AECS reads a Format-2 AECS, it will see an invalid value for the Output Bits Valid field and return an AECS error.

- If an accelerator expecting a Format-2 AECS reads a Format-1 AECS, it will see the incorrect Format Number and return an AECS Format error.

The intent is to provide a mechanism whereby the software library (or application, if not using the library) could check for these errors and, if necessary, convert the AECS to the proper format and resubmit the descriptor. Alternatively, the software could check these bits before submitting the descriptor.

## 3.3 Decompression

Intel IAA supports decompression compatible with the Deflate compression standard described in RFC 1951. The decompression block reads a compressed stream and an optional AECS and generates the corresponding uncompressed data. The uncompressed data may be written directly to memory or passed to the input of the filter function.

Decompression can be performed on a single buffer, where the entire stream is contained in a single buffer, or on multiple buffers, where the stream spans more than one buffer. In the latter case, a separate descriptor is submitted for each buffer. This is called a job. That is, a job is a series of descriptors that operate on one logical stream. The descriptors in a job are tied together by the use of a common AECS. The AECS written by each descriptor in the job is read by the next descriptor. The AECS structure contains data used to connect the individual descriptors used to process one logical job. It is typically read on all but the initial descriptor of a job, and it is written on all but the final descriptor.

For operations that write the output of decompression to memory, the output buffer size specified in the descriptor should be large enough to hold the output of the operation. If the output does not fit into the specified output buffer, the decompression operation terminates and reports the amount of the input that was consumed. An additional descriptor must be submitted to process the remaining input data into a new output buffer.

Decompression is supported for Deflate streams where the size of the history buffer is no more than 4 KB. (The default size for Deflate is 32 KB.) Using an input stream with a larger history size results in an error.

## 3.3.1 Verification

The decompression operation can be used by software to verify that the output generated by compression is correct, i.e., that it can be decompressed back to the original input. This could be done as a normal decompression job, with the output going into a buffer that is then compared against the original input.

A more efficient approach is to suppress the output of the decompressor. In this case, the hardware would write no output data, but it would still calculate the CRC of the decompressed data. This can then be compared against the CRC computed from the input to the compressor.

This avoids the need to have a temporary buffer in which to write the decompressed data, the overhead of the compare operation, and the bandwidth required to write and read that data.

### 3.3.2 Index Generation

The generation of indices for the compressed data (cf. Section 3.4.3) is done by the decompressor while it is operating for verification. In this case, the normal decompressed output has to be suppressed. Then when indexing is enabled, the index data is written to the output buffer. Note that the compression must have been done with indexing enabled.

The flush flag cannot be used when indexing is being used, except for a last descriptor (i.e., when write\_AECS is "never").

#### 3.3.2.1 Structure of the Index Table

Each index entry is 8-bytes (64-bits) long. The upper 32-bits is the CRC value of the uncompressed data up to the point corresponding to that index. The lower 32-bits is the bit-offset in the compressed data stream.

It is important to understand what the different indices point to, so that the proper ones can be used for access. In general, the indices for each block point to the boundaries between Deflate Block headers, miniblocks, and the EOB token. In other words, there will be an index entry at the start and at the end of each of these structures within the Deflate stream. The exception is that the hardware will not write an entry corresponding to the start of the first Deflate Block header. It is recommended that software write an initial entry of 0 into the index buffer, set the Destination Address to point to the second index entry, and set the Max Destination Size to the actual size of the index array minus 8.

Note that the AECS field Bit Offset for Indexing is used to pass the bit offset between linked descriptors. If it is desired that the bit offsets in the index table start from a non-zero value, then this field can be written for the first descriptor to set the starting value. In this case, the initial index value written by software would contain this value rather than zero.

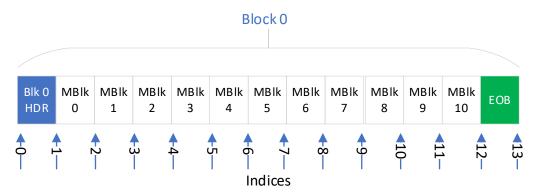

To make it easier to map between miniblock number and index entries, it is recommended that the block structure of the Deflate stream be regular. There are two common forms of this. The simplest is where the output consists of a single Deflate block. The index layout for this is illustrated in Figure 3-1.

Figure 3-1: Index Arrangement for Single Block Usage

In this example, the first index (created by software) points to the start of the Deflate Block header. Indices 1 through 11 point to the start of the 11 miniblocks. Index 12 points to the start of the EOB token, and Index 13 points to the end of the EOB token, which is also the end of the stream.

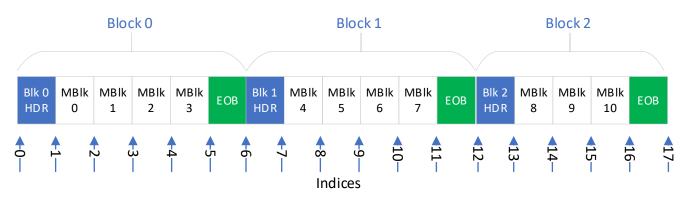

The other common structure is where there are multiple blocks, and all of the blocks with the possible exception of the last block are the same size. This is illustrated in Figure 3-2.

#### Figure 3-2: Index Arrangement for Multiple Block Usage

In this case, all of the Deflate Blocks except for the last one must have a size that is a multiple of the miniblock size. It is convenient but not required that the size be a power of 2 (e.g., a miniblock size of 1kB and a Deflate Block size of 32kB).

Knowing how big the miniblocks are, and how many miniblocks are in each Deflate Block, one can map from an offset in the

uncompressed stream to a particular miniblock, and from there one can compute the index entries that point to the start and end of that Deflate Block's header, and to the start and end of that miniblock.

#### 3.3.3 Decompression With non-Byte-aligned Boundaries

In some applications, a user may want to decompress part of a compressed stream, where the starting and/or ending locations do not align with a byte boundary.

In one formulation, the user has a pointer (actually an offset) to the start of the data to be processed (as a bit offset) and a pointer to the end (actually an offset to first bit not to be processed). If these are called START and END, then the total bit length of the data to be processed would be (END – START). For example, these pointers might have come from the index table (cf. Section 3.3.2.1).

Conceptually, one wants to convert these two pointers to a pointer to the starting byte, the number of bytes to process, and the number of bits to ignore in the first and last byte. This can be done, for example, with the following logic:

```

Start_address = data_buffer_address + START/8;

Size = ((END + 7)/8) - (START/8);

Ignore_start_bits = START & 7;

Ignore_end_bits = 7 & (0 - END);

```

Note that the Size is  $\underline{not}$  ((END + 7 - START)/8).

#### 3.3.3.1 Ending on a non-Byte-aligned Boundary

Ending on a non-byte-aligned position is relatively easy. There is a Decompression Flags field "Ignore End Bits" (see Section 6.3.2.1). A non-zero value in this field instructs IAA to stop processing on the last byte the specified number of bits from the end of the byte. For example, a value of 0 (the default) indicates that the whole byte should be processed, whereas a value of 3 would indicate that the first 5 bits should be processed, and the last 3 should be ignored.

The only complication is when the Decompression Bit Order flag is set. In this case, the input consists of an integral number of 16-bit words, or an even number of bytes. In this case, one may need to drop up to 15 bits. This can't always be done with the Ignore End Bits field, because that field is only 3 bits wide. To handle this case, there is 1-bit Ignore End Bits Extension field, which is logically bit-3 of the number of bits to be ignored. That is, in this case the Ignore End Bits Extension field gets bit-3 and Ignore End Bits 2:0 of the desired value.

This is slightly different for the CRC Flags. In this case, the "Ignore End Bits Extension" is really just bit-3 of the Ignore End Bits field. In other words, for the CRC opcode, the Ignore End Bits field is 4 bits wide, while in the other operations that have Decompress Flags, there is a 1-bit Ignore End Bits Extension field and a 3-bit Ignore End Bits field.

Note that if IAACAP bit-0 is 0, then the Ignore End Bits Extension field is not supported, and CRC, the Ignore End Bits field is only 3 bits wide. In this case, if the Decompress Bit Order flag is set, and the user wants to drop more than 7 bits, this cannot be done.

#### 3.3.3.2 Starting on a non-Byte-aligned Boundary: Method 1

The basic idea here is to store the partial byte (word or DWORD) that starts the data in the AECS input accumulator.

The IAA hardware contains an "input accumulator" which buffers data between coming in from memory and going out to the decoders. Roughly speaking, it takes data in a QWORD at a time, and outputs data at a bit granularity. It is represented in the AECS (cf. Section 6.4.1) as "Input Accumulator Data" and "Size QW *n*". Logically, the data area is considered to be an array of 32 QWORDs, with the number of bits present in each QWORD represented by a separate size field. For example, if the input accumulator was initialized to contain 9 bytes of data, then the data would be written into the first 9 bytes of the Input Accumulator Data field (8 bytes into the first QWORD and 1 byte into the second QWORD), and then Size QW 0 would be set to 64 (64-bits = 8 bytes), and Size QW 1 would be set to 8.

In a typical case, when one is starting on a non-byte-aligned boundary, the input accumulator is empty. Then one can simply write the partial byte (or larger granularity) into the beginning of the input accumulator data (i.e. into the first QWORD of the input accumulator data) and set the Size QW 0 field to the number of bits so written.

Note that the valid data should start at bit-0 of the input accumulator. So, for example, if the data started on bit-3 (i.e., one wanted to drop the first 3 bits), one would set the input accumulator data to (data byte >> 3) and the Size QW 0 field to 5. One would then point the Source 1 Address to the first full byte (i.e., the byte after the partial byte), and adjust the Source 1 Transfer Size accordingly.

This example assumes that Decompress Bit Order is not set. If this flag was set, one would need to write the partial word into the input accumulator rather than the partial byte. Also note that in this case, the bits within each 16-bit word are reversed (e.g., bits 0 and 15 are swapped, bits 1 and 14 swapped, etc.) by the hardware on the way into the input accumulator. So, in this case, if one wanted to drop the first 3 bits of the first word, one would read the partial word, bit-reverse the data, right shift it by 3 bits, write it into the start of the input accumulator data, set the size to 13, and set the Source 1 address to point to the following (full) word.

## 3.3.3.3 Starting on a non-Byte-aligned Boundary: Method 2

If IAACAP bit 1 (cf. Section 7.2.2) bit is set, then IAA supports an AECS field "Drop Initial Bits" (cf. Sections 6.4.1 and 3.7). In this case, one can just point the Source 1 Address to the partial byte/word and set this field to the desired number of bits to be dropped.

If this IAA device supports decryption, and one wants to do a decrypt-decompress starting on a boundary that is unaligned with a cryptographic block boundary, then one would need to point the Source 1 Address to the start of the cryptographic block and set the Drop Initial Bits field to the number of bits between the start of the cryptographic block and the start of the desired Deflate data. For that reason, the Drop Initial Bits field can be up to 127, which is one bit less than 16 bytes.

For the case of decrypt-decompress, one could use Method 1, but this would require the software to decrypt the initial cryptographic block and then extracting the decrypted data.

# 3.4 Compression

Intel IAA supports compression compatible with the Deflate compression standard described in RFC 1951. The compression unit can operate in three modes: Huffman-mode, Statistics-mode, or Huffman-Generation mode.

In Huffman-mode, it will read a stream of input bytes, generate a stream of literals and matches, encode them using Huffman tables read from the AECS, and write those Huffman codes into the output buffer.

In Statistics-mode, rather than writing the Huffman Tokens to the output buffer, it will instead compute a histogram of how many times each Huffman code appears. At the end of processing, the histogram table is written to the output buffer.

Huffman Generation Mode is described in Section 3.4.5.

To generate a dynamic Deflate block, the software should do one pass in Statistics-mode, use the statistics to generate a set of Huffman Tables optimized for those statistics, and then do a second pass (with the same input data) in Huffman-mode. Alternatively, if Huffman Generation is supported, software can use this hardware capability.

The hardware will optionally add an EOB (End of Block) token to the output or add an EOB and a zero-length Stored Block to the output. The block header, however, should be added to the output accumulator in the AECS by software before submitting the descriptor.

#### **3.4.1** Statistics Mode Output

The format of the histogram table output in Statistics-mode is as a table of 318 32-bit words:

| Byte Offset | Description        |  |

|-------------|--------------------|--|

| 0           | LitLen[0] count    |  |

|             |                    |  |

| 1140        | LitLen[285] count  |  |

| 1144        | Reserved           |  |

| 1148        | Reserved           |  |

| 1152        | Distance[0] count  |  |

|             |                    |  |

| 1268        | Distance[29] count |  |

Table 3-4

Histogram Table Output in Statistics Mode

These give the number of times each of 286 Literal/Length Tokens appeared, and the number of times the 30 Distance Tokens appeared. Note that while each count occupies a 32-bit field, the actual counts are 19-bits wide. If 219 or more of a given token appears, the count saturates at (2<sup>19</sup>-1).

#### **3.4.2 Compression Output Overflow**

For compression, "output overflow" is a non-recoverable error, and the AECS is not written.

The output buffer should be sized slightly larger than the input buffer, such that the input buffer could be encoded as a Deflate stored-block, written to the output buffer, and fit. In that case, if the compression operation actually results in data expansion such that the compressed data would not fit into the output buffer, the software (library or application) should ignore any partial results that the compressor generated and add the current input to the output stream as a stored block. This would result in a better compression ratio than keeping the "compressed" data.

#### 3.4.3 Compression Indexing

The IAA compression logic supports "Indexing." When this is enabled, it also defines a "miniblock size." The meaning of this is that no match will cross a miniblock boundary, and no match will reference data in a different miniblock. This will allow a decompressor to start decompression at a miniblock boundary at the cost of a slightly reduced compression ratio.

Note that the compressed data stream generated is a valid Deflate stream. It can be decompressed in the same manner as any other Deflate stream. In addition, any arbitrary miniblock can also be decompressed without decompressing the rest of the stream.

In order for indexing to work properly, the application must know the block structure of the output. This means that either the compressed output must fit within the provided output buffer (i.e., no "output overflow") or the input buffer must be smaller than 64kB so that it will fit into a single stored block.

If Compression Indexing is enabled, the input buffer must be a multiple of the miniblock size, except for the last descriptor of a sequence. This is accomplished in some generations with a "Last Descriptor" bit in the Compress AECS (see Section 3.4.7).

The structure of the index table is described in Section 3.3.2.

### **3.4.4** Compression with a Dictionary

Intel IAA supports Deflate compression with a dictionary. The same dictionary must be used for both compression and decompression. Dictionary compression is most useful when compressing small buffers.

The dictionary itself is just a block of text conceptually prepended to the input stream. The combined dictionary and input stream is compressed, and the compressed tokens associated with the dictionary are dropped. Another way to look at this is that, with dictionary compression, a given bit of data to be compressed can be matched against a location before the start of the buffer.

To compress with a dictionary, the Load Dictionary compression flag must be set, and the dictionary data is placed at the end of normal compression AECS (see Section 6.4.2). I.e., the dictionary data starts in the AECS at byte offset 1568. The dictionary data can be constructed in three different formats with three different sizes. The trade-off is that a larger size for the dictionary data will generally result in a better compression ratio, but it will also cause a longer latency for the compress operation. Some applications may find that the improvement in compression ratio is not worth the increase in compress latency and so opt for a smaller amount of dictionary data.

The dictionary data consists of two variable-length regions. The first is the portion of the dictionary text that is actually being used. The second is a representation of the corresponding hash tables as they would have been created by the hardware. The hash table region can be built with either 2 or 4 pointers per entry. The selection of how big the actual dictionary and hash table entries is called the dictionary "style" and is specified with descriptor flag bits.

The dictionary styles and the corresponding sizes are given in Table 3-5.

| Dictionary Style            | Size of Dictionary | Size of Hash Table | Total Size |

|-----------------------------|--------------------|--------------------|------------|

| 2K Dictionary, 2 Ptrs/Entry | 2kB                | 4kB                | 6kB        |

| 4K Dictionary, 2 Ptrs/Entry | 4kB                | 4kB                | 8kB        |

| 4K Dictionary, 4 Ptrs/Entry | 4kB                | 8kB                | 12kB       |

#### Table 3-5 Dictionary Styles and Sizes

If the raw dictionary is larger than the size of the dictionary as specified by the style, the final bytes of the raw dictionary should be used. If the raw dictionary is smaller, it should be prepended with zero bytes.

## 3.4.5 Compression Header Generation

Intel IAA has the ability to generate Huffman Tables based on the generated statistics or based on statistics directly input, and to optionally generate a Deflate header corresponding to those tables.

Header Generation can operate in either of two modes: 1-Pass or 2-Pass.

In the 2-Pass mode, dynamic compression with Header Generation is similar to compression without Header Generation. The same input is submitted twice. In the first pass, no compressed output is generated. Instead, the statistics/tables of the output are produced. The second pass actually does the compression.

The difference is that without header generation, the first pass returns the statistics to the software, which must compute the Huffman tables itself. With 2-Pass Header Generation, the first pass returns the Huffman Tables (and optionally the Deflate header), so that the software does not need to perform the Huffman calculations. This both reduces the latency of doing both passes and reduces the CPU load.

The second pass is the same in both cases—it doesn't matter whether the tables and header were created by software or the hardware.

In 1-Pass mode, the compression is done with only one descriptor. In this mode, the hardware will internally do one pass through the data, compute the Huffman Tables, then automatically do a second pass through the data, generating the final compressed output. This is obviously better for the application, but the limitation is that this can only be used if the amount of data to be compressed is no larger than 4kB.

There are three variations of each mode:

- Don't generate a Deflate Header.

- Generate a Deflate Header that is not marked as bFinal.

- Generate a Deflate Header that is marked as bFinal.

In some cases, such as if the input is being compressed in Huffman-only mode with no EOB, it may not be possible to produce a valid Deflate header. Processing such tables should be done without Deflate header generation. If a Deflate header is requested and cannot be created, the descriptor terminates with an error.

Normally, there are no Huffman Codes assigned to tokens with statistics counts of 0. In some cases, the application may want to ensure that all of the tokens are present in the generated tables. This could be used, for example, for "semi-dynamic" compression, where the first portion of a large file is compressed dynamically, and then the same Huffman tables are used for the rest of the file. In this case, all tokens must be represented by Huffman codes, because they might appear later in the file even if they did not in the earlier section.

If the Make Complete Tables bit in the Compress 2 Flags is set, then some of the statistics counters that have 0 values are changed to 1. This means that none of these counters will have a 0 count, and so all tokens will have codes created for them. The counters so changed are the Literal/Length counters up to the last counter that has a non-zero count, or up to counter 272, whichever is greater; and the distance counters up to the last counter that has a non-zero count, or up to counter 23, whichever is greater.

## 3.4.5.1 2-Pass Header Generation

In 2-Pass Header Generation mode, nothing is written to the destination, and both the destination address and size should be set to 0. Source 2 should be written as AECS. The results are found in the written AECS.

The generated codes are found in the Huffman Tables section of the AECS, as described in Section 6.4.2. The Deflate header is found in the Output Accumulator section. If the Deflate header is not requested, the Output Accumulator section is left unchanged.

Note that because of this, the AECS that is written by the first pass is in the correct format to be read in for the second pass.

In this mode, the Write AECS Huffman Tables flag should be set in the descriptor Compress 2 Flags so that the table portion of the AECS will be written (cf. Section 3.2).

### 3.4.5.2 1-Pass Header Generation

In 1-Pass mode, there is no restriction on whether Source 2 is read or written. Normally, the Write AECS Huffman Tables flag is not used, as the application would typically not care what the generated Huffman tables were.

If the application does care what tables were used, it can set the Write AECS Huffman Tables flag and have the tables written as part of the AECS. Note, however, that the output accumulator will contain the end of the output bit stream, not the Deflate header.

### 3.4.5.3 Header Generation with Statistics Input

Normally, the statistics used to construct the Huffman Tables are the counts of the tokens generated by the compressor. If the Header Gen Stats Input bit is set in the Compress Flags, then the normal compress operation is suppressed, and Source 1 and Destination are not used.

Instead, Source 2 must be read and written as AECS. On input, the Huffman Table section (see Section 6.4.2) contains the statistics count values. In each DWORD, bits 18:0 contain the counts, and bits 31:19 should be 0. On output, the AECS contains the generated Huffman Tables and optionally a Deflate header, as is produced with 2-Pass header generation.

In this mode, the Enable Header Generation field must specify one of the 2-Pass modes.

## 3.4.6 Compression Early Abort

In certain cases, an application may be compressing data that might or might not be compressible to a given level. In such a case, the application might want to abort the compression early if the compression job looks likely to not achieve the desired level of compression.

The advantage of doing this is that if the compression does not achieve the desired level of compression, the application can be notified sooner, and thus the compression latency can be reduced. The disadvantage of doing this is that since the

level of compression is only being estimated, and the estimate will in general be based on only a portion of the input file, then it is possible that a file that actually does achieve the desired level of compression might be considered "incompressible" and aborted, when (in hindsight) it shouldn't have been.

The estimate of the compressed size of the output is the number of literals plus twice the number of references. In other words, it approximates the size of the output by assuming that each literal will take one byte, that each reference will take two bytes, and disregarding the block header.

This feature is controlled by two fields in the Compression 2 Flags (Section 6.3.5.2).

The Early Abort Size field determines when the compressor will perform the check. It can check as soon as 512, 1024, 2048, or 4096 input bytes have been processed. It only checks once, when the specified threshold is passed.

When the check occurs, the size estimate is compared against the input size (as measured at the input of the Deflate compressor) multiplied by the Early Abort Threshold. If the estimate is greater than or equal to the threshold, the compression job is aborted with an error.

Note that the estimated size can never be greater than the input size and can only be equal if no matches were found.

If the input size is equal to the Early Abort Size, then the check is done at the end of the input. This probably only makes sense to do if one is doing Header Generation. In this case, an abort would avoid the header generation and the 2nd half of the processing if any. Otherwise, rather than setting the Early Abort Size to the input size, the application is probably better off setting the Max Destination Size to the desired limit and getting an output overflow if that size is exceeded.

## 3.4.7 Last Descriptor Bit

In general, a compression job can be continued across multiple descriptors, but there is a case where this cannot be done.

When Compression with Indexing is being done (cf. Section 3.4.3), all of the descriptors require their Source 1 size to be a multiple of the miniblock size, except for the last one. This means that if in this mode a Source 1 size is not a multiple, then this descriptor cannot be continued with a following descriptor.

Starting with Generation 2, this is enforced with a new Compression AECS bit (cf. Section 6.4.2): Last Descriptor Bit. If a compression operation reads an AECS that has this bit set, then the operation is terminated with an error. Conversely, when a compression descriptor cannot be continued with a following descriptor, this bit is set when writing the AECS.

When the Last Descriptor Bit feature is not present, then continuing a compression job when it is not allowed will not result in an error, but it will also not generate correct results. In this case, this restriction must be enforced by software.

The presence of the Last Descriptor Bit is indicated by IAACAP bit 0 (see Section 7.2.2).

# 3.5 Encryption/Decryption

Intel IAA can perform data encryption. It can also perform data decryption, in which case the decrypted output can be written to the destination buffer, sent to the filter unit, or sent to the decompress unit.

A large encryption/decryption job can be divided into a series of separate descriptors, with the internal state passed between them via the AECS.

Three encryption algorithms are supported: GCM (Galois Counter Mode), AES-CFB (AES Cipher Feedback Mode), and AES-XTS. In each case, supported key sizes are 128 and 256 bits.

Due to space limitations in the descriptor structure, most of the flags and parameters associated with encryption/decryption are contained in the AECS. This is described in Section 6.4.1. Decryption can only be used with the following opcodes: Decrypt, Decompress, CRC64, Scan, or Extract.

AES-XTS cannot be used with indexing.

Decryption can be piped into other operations, so for example, one descriptor can do a decrypt-decompress operation. But encryption cannot be piped, so to do the inverse of the above would take two descriptors: one to do the compression and one to do the encryption.

Cryptographic processing is done one cryptographic block at a time (i.e., 16-bytes at a time). This means that when one crypto job is spread over multiple descriptors, partial blocks are stored in the "Crypto Input Accumulator" within the AECS, and then this data gets processed with the start of the data from the next descriptor. The last descriptor in the job should set the "Flush Crypto Accumulator" flag in the crypto flags in the AECS, so that the final partial block will be processed.

Note that this means the amount of output generated for an Encrypt or Decrypt operation might vary from the input size by up to 31 bytes. For example, on the first descriptor of a multi-descriptor decrypt job, the input could be 31 bytes long, and the output size would be 0. Conversely, on the last descriptor, the input could be 1 byte long, and the output size be 32 bytes.

## 3.5.1 AES-CFB

For encryption in CFB mode, the Initialization Vector (IV) is encrypted and then XORed with the plaintext to generate the ciphertext. Additionally, the ciphertext becomes the "IV" for the following block. The final ciphertext is returned as the final "IV."

This same process is done for decryption. The difference is that the ciphertext (which becomes the "IV" of the next block) is an input rather than an output.

## 3.5.2 GCM

GCM provides both encryption and authentication. The encryption is just AES in Counter Mode. The authentication is provided by computing a cryptographic hash.

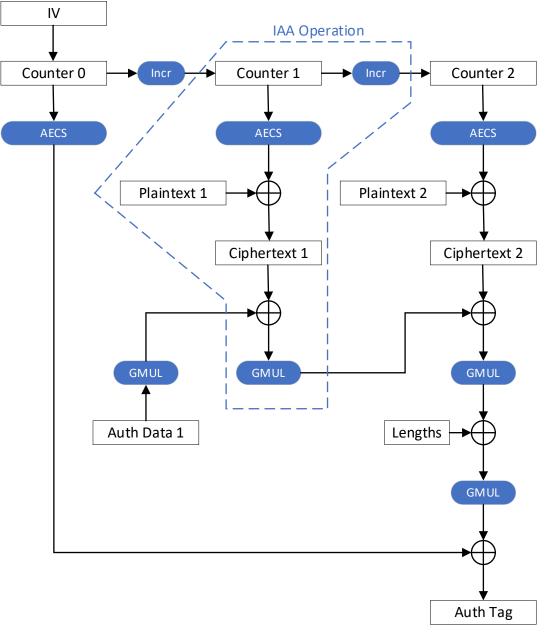

In this mode, the hardware only does the processing associated with the bulk data; the rest of the calculations must be done by software. The GCM calculations for encryption are show in Figure 3-3.

#### Figure 3-3 GCM Calculations

The dashed section indicates the operations done by the accelerator hardware. In particular, for each block of input data, it will encrypt the IV/counter, XOR that with the input text, XOR the ciphertext with the hash to get a new hash and increment the IV/counter. The initial counter increment, the encryption of Counter 0, and the final addition/hashing of the lengths and encrypted Counter 0 must be done by software. Similarly, the initial hashing of the Additional Authentication Data must be done in software.

## 3.5.3 XTS

AES-XTS is a block-oriented cipher mode. This means that normally it could only handle buffers that were a multiple of the cipher block size. To allow it to handle arbitrary sized buffers, XTS uses "ciphertext stealing" (CTS) at the end of the stream when the stream size is not a multiple of the cipher block size.

The practical implication of this is that XTS cannot be used on buffers that are smaller than 16 bytes. An attempt to do so will result in an error.

Ciphertext Stealing is invoked at the end of the input stream if the Flush Crypto Accumulator flag is set, and the total number of bytes in this job (i.e., the number of input bytes in this descriptor and in previous linked descriptors) is not a multiple of 16 (i.e., not a multiple of the cipher block size).

## 3.5.4 Decryption with Indexing

When using index mode to access encrypted data randomly (cf. Section 3.3.2), extra steps must be taken.

In particular, the actual data sent to the accelerator must start at an AES block boundary (16-byte boundary). Then the "Drop Initial Bits" feature (cf. Section 3.7) should be used to skip over the start of generated plaintext, so that the subsequent processing will start at the appropriate location.

Finally, the IV or initial counter value must be calculated appropriately. For CFB, this will generally be the previous block's ciphertext, except for the first block where it is the IV. For GCM (where only the AES Counter Mode portion is useful), the IV stored in the AECS must be the original IV added to the appropriate number of increments, based on the index of the block starting the decryption.

# **3.6 Checksum Calculations**

As a check, the accelerator generates a pair of checksums of the "raw" data. In particular, there are "compress-like" operations (i.e., Encrypt, Compress) that take original "raw" user data and create a processed version of it. For these functions, the checksums are computed on the original input data. Then there are "decompress-like" operations (i.e., Decrypt, Decompress) that take the processed data and try to recreate the original raw data. For these functions, the checksums are computed on the output data. Finally, there are the filter operations, which take "raw" data and process it further. For these functions, the checksums are computed on the input to the filter processor (i.e., after any decryption or decompression). The basic idea is that the checksums between complementary operations should match. The details of where the checksums are computed is given in Table 3-6.

| Operation                            | Туре            | Checksum Location |

|--------------------------------------|-----------------|-------------------|

| Encrypt, Compress                    | Compress-like   | Input             |

| Decrypt, Decompress                  | Decompress-like | Output            |

| CRC64, Scan, Extract, Select, Expand | Filter          | Input to Filter   |

#### Table 3-6 Checksum Location

The accelerator can generate either of two 32-bit CRCs: using the polynomial defined in ITU-T recommendation V.42, or in RFC 3720. It also computes the XOR checksum of the data. For this, the data are treated as 16-bit words. If there are an odd number of bytes, the final byte is zero-extended to 16 bits. Then these 16-bit words are all XORed together.

The initial values of the CRC and XOR checksum are read from the AECS for operations where the AECS is read; otherwise, initial values of 0 are used. The final values of the checksums are written to the completion record. They are also written to the AECS, for any operation where the AECS is written. The latter allows the values to be linked across the descriptors in a job, while the former allows the software to get the values even when the AECS is not written.

## 3.7 Drop Initial Bits vs. Drop Initial Bytes

There are two similar fields found in the AECS (cf. Section 6.4.1): Drop Initial Bytes and Drop Initial Bits<sup>1</sup>.

The Drop Initial <u>Bytes</u> field applies **only** to the input to the filter unit. The Drop Initial Bits field usually applies to the input to the decompress unit. However, if the opcode specifies a filter operation and the decompressor is not enabled, then the Drop Initial Bits field applies to the input of the filter unit.

If both of these fields ("Drop Initial Bits" and "Drop Initial Bytes") are being applied to the input to the filter unit, then at least one must be zero. If both are non-zero, the accelerator will return an error.

The primary use for Drop Initial Bits is to enable indexing on encrypted data (Section 3.5.4). Thus, it would typically be used for the input of the decompressor or filter unit, whichever is immediately downstream from the decryption unit.

Note that if Drop Initial Bits applies to the input of the filter unit, and the filter parser is PRLE, then Drop Initial Bits must be 0.

For a filter operation without decompression, the Source 1 size must be greater than the amount of data being dropped, except for EXPAND, where the Source 1 size must be greater or equal to the amount of data being dropped.

If decompression is enabled without decryption, then the sum of the Drop Initial Bits + Ignore End Bits cannot be greater than the Source 1 Size. If decompression is enabled with decryption, and Flush Crypto Input Accumulator is set, then the sum cannot be greater than the Source 1 Size plus the size of the Crypto Input Accumulator.

## 3.8 Filter Functions

The filter functions take one or two inputs, a primary input, and an optional secondary input. The primary input may be read from memory or received from the output of decompression or decryption. The primary input is parsed as described in 3.8.1. The output of the parser is an array of unsigned integers.

If the secondary input is used, depending on the operation type, it may be a bit vector or an array of packed unsigned integers. It can be packed in either little-endian format (starting at bit 0 of each byte) or big-endian format (starting at bit 7). When the secondary input is used, the operation cannot also use the AECS. Thus, any filter operation that uses the secondary input uses default values for any configuration information that would have been read from the AECS. This means that such operations cannot be used with decryption.

The output of the filter function may be either an array or a bit vector depending on the function.

For filter operations, the output buffer size specified in the descriptor must be large enough to hold the entire output of the operation. If the output does not fit into the specified output buffer, the operation fails with an unknown amount of the input processed. In this case, the software must resubmit the descriptor with a larger output buffer.

### 3.8.1 Parser

One of the following parsers may be selected to process the primary input to the filter function. The parser reads a byte stream and outputs a series of unsigned integers.

### 3.8.1.1 Packed Array

This is the standard parser. The input is a packed array of unsigned integers with a specified bit width. (The bit width need not be a multiple of the size of a byte.) The data can be packed in little-endian format (starting at bit 0 of each byte) or bigendian format (starting at bit 7).

<sup>&</sup>lt;sup>1</sup> Drop Initial Bits is not available on all IAA implementations. The availability of this feature is indicated by IAACAP bit 1 (see Section 7.2.2).

#### 3.8.1.2 Parquet RLE

The input is in the Parquet RLE format. The first byte of the data stream gives the bit width. This is followed by the encoded data. The bit-width cannot exceed 32-bits.

The format is:

```

parquet-rle: <bit-width> <encoded-data>

bit-width := bit-width of data stored as one byte

encoded-data := <run>*

run := <bit-packed-run> | <rle-run>

bit-packed-run := <bit-packed-header> <bit-packed-values>

bit-packed-header := varint-encode(<bit-pack-count> << 1 | 1)

// we always bit-pack a multiple of 8 values at a time, so we only store the number of values / 8

bit-packed-values := data stored as a packed array of bit-width values

rle-run := <rle-header> <repeated-value>

rle-header := varint-encode( (number of times repeated) << 1)

repeated-value := value that is repeated, using a fixed-width of round-up-to-next-byte(bit-width)

```

#### 3.8.2 Output Modification

Output Modification is an SQL filter feature that allows optionally generating an alternative representation of the result of the query being performed. In general, a SQL filter function results in two forms of output: 1) a bit vector (where the output bit-width is 1) or 2) an array of elements (where the output bit-width is greater than 1). For example, functions that perform a scan query, i.e., "is an element within a given range?," generate a bit vector, where each bit represents membership in that range. Functions that extract elements from an input array result in an output that could be either a bit-vector or an array depending on the bit-width of the input.

An optional flag bit forces the output to be considered an array, even if the bit-width is 1. This can be used to unpack a bit vector into an array of bytes, words, or DWORDs. Use of the Force Array Output Mod flag does not change whether one can apply the Invert Output flag. That is, if a nominal bit-vector output is forced to use array output modification, it can still be inverted.

#### 3.8.2.1 Modification When Output is Normally a Bit Vector

If the output of a function is normally a bit vector, the output can be modified in the following ways.

First, the bit vector can be optionally inverted (i.e., each bit is flipped).

Secondly, the output can be modified to consist of an array, where the array elements are the indices of the "1" bits of the bit vector. This can be used when the output bit vector is expected to be sparse in nature. The index of the first element (bit 0 of the bit vector) can be set to an arbitrary value instead of the default start index of 0. If the index of any output element is too large for the specified output width, the operation stops and reports an error.

#### 3.8.2.2 Modification When Output is Normally an Array

If the output of a function is normally an array of elements, then the bit width of the output elements is normally the same as the input bit width; i.e., the output is packed. When the output modification feature is enabled, output bit width can be adjusted to 8, 16, or 32 (with the high order bits padded with zeroes). This unpacks the output array into a desired word size. Using this feature makes the output array larger, but it makes it easier for software to process the data. The specified output bit width must be no smaller than the input bit width.

If the output bit width is 1, the output is treated as a bit vector, and the output modifications described in Section 3.8.2.1 apply, unless the Force Array Output flag is set.

## 3.8.3 Aggregation

In addition to generating the output data, the accelerator also computes several "aggregates" of the data. The type of aggregation depends on the type of output. In particular, it depends on the nominal, pre-modified output width: whether it is 1-bit wide or wider.

If the "pre-modification" output is a bit vector or an array output whose bit width is 1, then the following data are accumulated:

- Population count (the number of 1 bits).

- First (the index of the first 1 bit).

- Last (the index of the last 1 bit).

This data can be used to determine the sparsity of the output. If the output is sparse, software can use it to determine where to start and end processing, so that it doesn't need to process the 0 bits at the start or end of the vector.

If the "pre-modification" output is an array whose bit-width is greater than 1, then the following data are accumulated:

- Sum (the sum mod 232 of the output values).

- Minimum value.

- Maximum value.

Note that the population count is actually a special case of "sum."

Note that if the Force Array Output flag is set, then the array aggregates are computed. So, in most cases, the min and max values would be 0 and 1, rather than the indices of the first and last 1-bit.

# 3.9 Chaining of Functions

- If IAACAP bit 2 is 0, the output of decryption/decompression can be chained into the input of the filter unit for all operations other than CRC64.

- If IAACAP bit 2 is 1, the output of decryption/decompression can be chained into the input of the filter unit for all operations.

# 3.10 Operation Types

The operations No-op, Drain, and Translation Fetch are the same as in Intel<sup>®</sup> DSA.

### 3.10.1 Decompress

The Decompress operation decompresses the input and writes the decompressed data to memory. The Source 1 Address and Source 1 Transfer Size specify the location of the compressed input data. The Destination Address and Maximum Destination Size specify the location of the decompressed output data. The Source 2 Address and Source 2 Transfer Size optionally specify the AECS. The Read Source 2 and Write Source 2 fields indicate the usage of the AECS (read, written, neither, or both). Decompression Flags control aspects of the decompression operation. The "Enable Decompression" flag must be set.

Optionally the input to the decompressor can be taken from the output of the decryption unit.

If the Status of the operation is Output buffer overflow, the decompression job can be resumed by submitting a follow-on descriptor with a new buffer to contain the remaining decompressed output. The Write Source 2 flag should be 2 for the final (or only) descriptor in a decompression job, to ensure that the state of the decompressor can be saved in the AECS in case of output buffer overflow. The Write Source 2 flag should be 1 for descriptors before the final descriptor in a multiple-descriptor job.

The output may be suppressed (for verification purposes) or replaced with index output (see Section 3.3.2). If the Enable Indexing flag is set, then the Suppress Output flag must also be set.

## 3.10.2 Compress

The Compress operation compresses the input and writes the compressed data to memory. The Source 1 Address and Source 1 Transfer Size specify the location of the input data. The Destination Address and Maximum Destination Size specify the location of the compressed output data. The Source 2 Address and Source 2 Transfer Size optionally specify the AECS. The Read Source 2 and Write Source 2 fields indicate the usage of the AECS (read, written, neither, or both). The Compression Flags and Compression Flags 2 control aspects of the compression operation.

If the compressed output does not fit into the output buffer, the operation fails with an error.

In one usage, the output buffer is sized large enough to store the input as a "stored block." If the compressed output is too large to fit into this buffer, then the partial results of the compression should be thrown away by software and replaced by a stored block.

Usage of the Source 2 / AECS is:

| Condition                               | Source 2 Read | Source 2 Write |

|-----------------------------------------|---------------|----------------|

| Statistics Mode w/o dictionary          | Not allowed   | Not allowed    |

| Statistics Mode with dictionary         | Required      | Not allowed    |

| 1-Pass Header Gen Mode, w/o dictionary  | Optional      | Optional       |

| 1-Pass Header Gen Mode, with dictionary | Required      | Optional       |

| 2-Pass Header Gen Mode                  | Optional      | Required       |

| Otherwise                               | Required      | Optional       |

## 3.10.3 CRC64

The CRC64 operation computes an arbitrary CRC up to 64-bits in width.

The CRC Bit Order flag indicates whether bit-0 in each data byte is the least-significant or the most-significant bit. Having bit-0 be least-significant corresponds to the "normal form" of the data, whereas having bit-0 be most-significant corresponds to the "bit-reversed form" of the data. This field also impacts the byte order of the CRC output. If bit-0 is least-significant, then the least significant bit of the CRC is bit-0 of byte-0. If bit-0 is most significant, then the least significant bit of the CRC.

The CRC is essentially the residue (remainder) after polynomial division. The "initial value" of the CRC is essentially a constant that is XORed with the initial data bytes. This constant has the same size in bits as the polynomial. In some CRCs, this initial value is zero. In others, it is all 1's. This is determined by the "invert CRC" flag bit. If this flag bit is 0, then the initial value is 0. If the flag bit is set, then the initial value is the "bitwise inverse of 0" or all 1's. As described below, this feature can be used to compute the CRC for polynomials smaller than 64-bits. Because of this, when the "invert CRC" flag is set, the initial value will only have 1-bits from the least-significant 1-bit in the polynomial to the most significant bit. E.g., if the polynomial represents a 32-bit CRC, the initial value will only have 32 1-bits.

Additionally, if the invert CRC flag is set, the final residue is XORed with the initial value before being returned.

The CRC Polynomial field defines the CRC polynomial in normal (not bit-reversed) form, regardless of the state of the CRC Bit Order flag. In the polynomial definition, bit-63 is always most significant.

Although this operation is designed to generate 64-bit CRCs, it can also be used to generate smaller arbitrary CRCs. In that case, the polynomial is placed in the most-significant portion of the CRC Polynomial field (i.e., starting at bit 63), and the results are found in the most-significant portion of the CRC64 field in the completion record, whose location does depend on the value of the CRC Bit Order flag.

The following are some well-known CRCs and the programming required to generate them:

| CRC           | Polynomial       | Bit Order | Invert CRC | Output           |

|---------------|------------------|-----------|------------|------------------|

| CRC32 (gzip)  | 04C11DB700000000 | 1         | 1          | 00000000XXXXXXXX |

| CRC32 (wimax) | 04C11DB700000000 | 0         | 1          | XXXXXXXX00000000 |

| CRC32 (iSCSI) | 1EDC6F4100000000 | 1         | 1          | 00000000XXXXXXXX |

| T10DIF        | 8BB7000000000000 | 0         | 0          | XXXX000000000000 |

| CRC-16-CCITT  | 1021000000000000 | 1         | 1          | 000000000000XXXX |

| Table 2-7 | Examples o | F CPC64  | Parameters |

|-----------|------------|----------|------------|

| ladie 3-7 | Examples c | DT LKL64 | Parameters |

### 3.10.4 Scan

The Scan operation determines whether each element in the input data stream is in the inclusive range defined by the configuration variables Low Filter Param and High Filter Param (i.e., if (Low Filter Param  $\leq$  element value  $\leq$  High Filter Param)). The output is a bit vector where each 1 indicates that the corresponding input element is in the range.

The output may be modified by inverting each bit and/or by converting to an array of indices.

By selecting suitable values for the parameters and the Invert Output Bits flag, any of the following filter functions may be realized: =,  $\neq$ , <,  $\leq$ ,  $\geq$ , >, within a range, and outside a range.

#### 3.10.5 Extract

The Extract operation returns the elements in the input data stream whose indices fall within the range defined by the configuration variables Low Filter Param and High Filter Param. The indices of the input values are assigned sequentially starting with 0. The output is an array of the input values whose indices fall within the range.

By default, the output bit width is the same as the input bit width. The output may be modified as described in Section 3.8.2.

If Low Filter Param is 0 and High Filter Param is at least the number of elements in the input, then all elements are extracted. With output modification, this can be used to unpack a packed array to a desired word size (byte, word, or DWORD).