# **Product Marking Information for Intel® MAX® Series Devices**

MAX® II, MAX® V

Version: 1.0

Last updated: April, 2022

Reference Number: 11G-00016

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, the Intel logo, Agilex, Altera, Arria, Cyclone, Enpirion, eASIC, easicopy, MAX, Nios, Quartus, Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

Copyright © 2022, Intel Corporation. All rights reserved.

### **Contents**

| 1.0 | Top Mark Layout for Intel MAX II & MAX V Devices | 4 |

|-----|--------------------------------------------------|---|

| 2.0 | Document Revision History                        | 7 |

# 1.0 Top Mark Layout for Intel MAX II & MAX V Devices

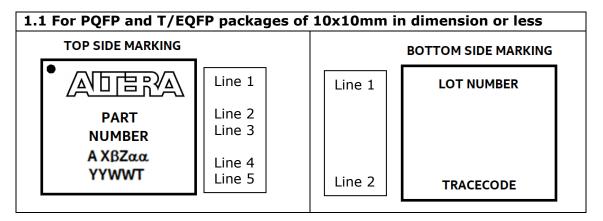

| Line 1                     | Company logo (ALTERA®)  |

|----------------------------|-------------------------|

| Line 2                     | Part Number             |

| Line 3                     | Part Number (continued) |

| Line 4                     | Date Code               |

| Line 5                     | Date Code (continued)   |

| Bottom side marking Line 1 | Lot Number              |

| Bottom side marking line 2 | Tracecode               |

| Date Code: A Xβ Z αα YYWWT |                                            |  |

|----------------------------|--------------------------------------------|--|

| Α, Χ, β, Ζ, αα, Τ          | Manufacturing Identifiers                  |  |

| YYWW                       | YY = Year,                                 |  |

|                            | WW = Workweek in a 6-week date code window |  |

| Work Week | Date Code |

|-----------|-----------|

| 1 - 6     | YY01      |

| 7 - 12    | YY07      |

| 13 - 18   | YY13      |

| 19 - 24   | YY19      |

| 25 - 30   | YY25      |

| 31 - 36   | YY31      |

| 37 - 42   | YY37      |

| 43 - 48   | YY43      |

| 49 - 53   | YY49      |

# 1.2 For MBGA 64,68 and 100 pin count Line 1 Line 2 NUMBER XYYWW LOT NUMBER Line 4 Line 5

| Line 1                  | Company logo (ALTERA®)  |

|-------------------------|-------------------------|

| Line 2                  | Part Number             |

| Line 3                  | Part Number (continued) |

| Line 4                  | Date Code               |

| Line 5                  | Lot Number              |

| Left side vertical mark | Tracecode               |

| Date Code: CWWYY |                                            |  |

|------------------|--------------------------------------------|--|

| Χ                | X Manufacturing Identifiers                |  |

| YYWW YY = Year,  |                                            |  |

|                  | WW = Workweek in a 6-week date code window |  |

| Work Week | Date Code |

|-----------|-----------|

| 1 - 6     | YY01      |

| 7 - 12    | YY07      |

| 13 - 18   | YY13      |

| 19 - 24   | YY19      |

| 25 - 30   | YY25      |

| 31 - 36   | YY31      |

| 37 - 42   | YY37      |

| 43 - 48   | YY43      |

| 49 - 53   | YY49      |

#### Top Mark Layout for Intel MAX II & MAX V Devices

### 1.3 All other MAX II and MAX V packages and pin count

**PART NUMBER**

Α ΧβΖααΥΥWWT COUNTRY

**FPO NUMBER** TRACECODE

Line 1

Line 2

Line 3

Line 4 Line 5

Line 6

Line 7

| Line 1                                 | Company logo (ALTERA®)                 |

|----------------------------------------|----------------------------------------|

| Line 2                                 | Device Family logo (MAX® II or MAX® V) |

| Line 3                                 | Part Number                            |

| Line 4                                 | Date Code                              |

| Line 5                                 | Country of Origin (COO)                |

| Line 6                                 | Top ID* (FPO/Lot#)                     |

| Line 7                                 | Top ID* (Tracecode)                    |

| *Certain packages (RQFP, EQUAD) will h | ave the Top ID marked in a single line |

| Date Code: A Xβ Z αα YYWWT |                                            |  |

|----------------------------|--------------------------------------------|--|

| Α, Χ, β, Ζ, αα, Τ          | Manufacturing Identifiers                  |  |

| YYWW                       | YY = Year,                                 |  |

|                            | WW = Workweek in a 6-week date code window |  |

| Work Week | <b>Date Code</b> |

|-----------|------------------|

| 1 - 6     | YY01             |

| 7 - 12    | YY07             |

| 13 - 18   | YY13             |

| 19 - 24   | YY19             |

| 25 - 30   | YY25             |

| 31 - 36   | YY31             |

| 37 - 42   | YY37             |

| 43 - 48   | YY43             |

| 49 - 53   | YY49             |

## **2.0 Document Revision History**

| Date       | Version | Changes          |

|------------|---------|------------------|

| April 2022 | 1.0     | Initial release. |