## FFT Beamforming Reference Design

Reference Design Datasheet

## Description

10

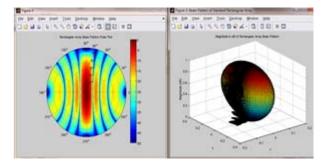

The FFT beamforming demo generates multiple beams simultaneously for spatial filtering. This allows coverage of the same volume with fewer dwell positions, resulting in reduced search frame time and quick target detection. In multi-mode radar, this allows the tracking of multiple targets simultaneously. The number of beams formed is equal to the number of elements in the phase array, and the direction of the beams are formed at fixed angles. Since the beam angle resolution is dependent on the number of elements in the phase array, it typically requires a large number of elements in the phase array to improve the beam resolution using this technique.

Beamforming in the frequency domain has less stringent requirements on the input data sample rate compared to the time domain technique. The input sampling frequency does not have an impact on the beam steering angle resolution. With FFT beamforming, there is potential reduction in computation workload as the size of the phase array increases. This translates to better performance which is an essential requirement for real-time systems. The benefit becomes more apparent with radar applications requiring large phase array systems.

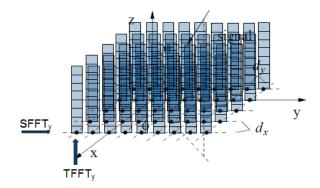

The multibeam beamformer involves two-dimensional (2D) FFT, which can be decomposed into two separate

one-dimensional (1D) FFT processes: temporal FFT, followed by spatial FFT. For planar arrays, the process can be decomposed further to 2D FFT in the x-axis, followed by another 2D FFT in the y-axis.

In order to support wider bandwidth, the analog-todigital converter (ADC) for these phase array systems are running in the giga samples per second (GSPS) rate. In order to support fast fourier transform (FFT) beamforming with data sample rates in the GSPS, this requires a super sample rate architecture that is able to process multiple phases in parallel. This demo highlights the highly parameterizable super sample rate FFT IP in DSP Builder Advanced Blockset. This allows the designer to select the number of phases, size of the FFT, and fixed or floating point implementation.

## Features

- Programmable super sample rate FFT IP

- FFT beamforming targeting linear array

- FFT beamforming targeting planar array

- Altera's System-in-the-loop with MATLAB

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE,

NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor

now part of Intel 101 Innovation Drive San Jose, CA 95134 www.altera.com

products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.