# **PRODUCT BRIEF**

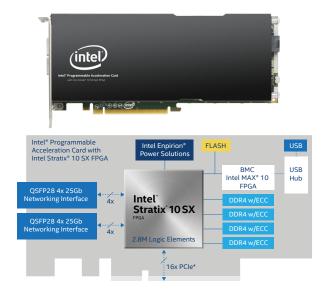

# Intel<sup>®</sup> Programmable Acceleration Card (PAC) with Intel Stratix<sup>®</sup> 10 SX FPGA

# Introduction

This high-performance FPGA acceleration card for data centers offers both inline and lookaside acceleration. Expanding upon the Intel<sup>®</sup> FPGA Programmable Acceleration Card (PAC) portfolio, it offers inline high-speed interfaces up to 100 Gbps for video transcode and streaming analytics applications. It provides the performance and versatility of FPGA acceleration and is one of several platforms supported by the Acceleration Stack for Intel Xeon® CPUs with FPGAs. This acceleration stack provides a common developer interface for both application and accelerator function developers, and includes drivers, application programming interfaces (APIs), and an FPGA interface manager. Together with acceleration libraries and development tools, the acceleration stack saves developer's time and enables code re-use across multiple Intel FPGA platforms.

# **Targeted Workloads**

- Streaming analytics

- Video transcoding

- Financial technology (FinTech)

- Genomics

- Artificial intelligence

# **Key Components and Interfaces**

- Intel Stratix<sup>®</sup> 10 SX FPGA 1SX280HN2F43E2VG device

- 32 GB DDR4 memory banks with error correction code (ECC) (4 banks, 2,400 Mbps)

- x2 quad small form factor pluggable (QSFP) with interface speeds up to 100G

- PCIe Gen3 x16 interface

#### **Form Factor**

• Standard PCIe (3/4 length, full height, dual slot)

#### **Board Management**

- Intel MAX<sup>®</sup> 10 FPGA Baseboard Management Controller (BMC)

- Temperature and voltage readout

- Platform Level Data Model (PLDM)

- Intelligent Platform Management Interface (IPMI 2.0)

- Remote update of FPGA flash and BMC

# Power and Thermals

- Intel Enpirion<sup>®</sup> digital PowerSoC modules

- 225W Thermal Design Power (TDP)

- 55°C Temp Local Ambient (TLA); 650 Linear Feet per Minute (LFM)

# **FPGA Interface Manager**

- Common developer interface for Intel FPGAs

- Dynamically reconfigure the FPGA to suit the application workload acceleration demands

#### **Developer Tools and Libraries for Acceleration Function Developers**

- Intel Quartus® Prime software and the Intel FPGA SDK for OpenCL<sup>™</sup> Application Developers

- **Open Programmable Acceleration Engine (OPAE)**

- Intel-provided libraries

- Ability to co-simulate acceleration function with application

#### Availability

- Production programmable acceleration cards available through select original equipment manufacturers (OEMs) in 1H19

- Contact an Intel sales representative for inquiries

# For More Information

www.intel.com/stratix10sxpac •

Intel, the Intel logo, the Intel Inside mark and logo, the Intel. Experience What's Inside mark and logo, Altera, Arria, Enpirion, Intel, Intel Core, Intel Xeon, MAX, Nios, Quartus and Stratix are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others.

© Intel Corporation.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Features and benefits of Intel's technologies depend on system configuration, hardware, software and services. No computer system can be absolutely secure. Learn more at www.intel.com OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission by Khronos.