# **4th Gen Intel** <sup>®</sup> **Xeon** <sup>®</sup> **Processor Scalable Family**

**Specification Update**

Rev. 012US

December 2024

# Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel technologies may require enabled hardware, software or service activation.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure.

Performance varies by use, configuration, and other factors. Learn more on the Performance Index site.

Your costs and results may vary.

"Conflict-free" refers to products, suppliers, supply chains, smelters, and refiners that, based on our due diligence, do not contain or source tantalum, tin, tungsten or gold (referred to as "conflict minerals" by the U.S. Securities and Exchange Commission) that directly or indirectly finance or benefit armed groups in the Democratic Republic of the Congo or adjoining countries.

All product plans and roadmaps are subject to change without notice.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visiting the Resource and Documentation Center.

${\sf SPEC^{\$},\,SPECint^{\$},\,and\,\,SPECfp^{\$}\,\,are\,\,registered\,\,trademarks\,\,of\,\,the\,\,Standard\,\,Performance\,\,Evaluation\,\,Corporation.}$

Intel, the Intel logo, Xeon, Intel Core, Pentium, Intel Optane, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

December 2024

Doc. No.: 772415, Rev.: 012US

Copyright © 2024, Intel Corporation. All rights reserved.

# **Contents**

December 2024

| Revision History                                       | 6  |

|--------------------------------------------------------|----|

| 1.0 Preface                                            | 7  |

| 1.1 Related Documents                                  | 7  |

| 2.0 Identification Information                         | 9  |

| 2.1 Component Identification via Programming Interface |    |

| 3.0 Component Marking Information                      | 12 |

| 4.0 Summary Tables of Changes                          | 13 |

| 4.1 Codes Used in Summary Tables                       | 13 |

| 4.2 Errata Summary Table                               | 13 |

| 5.0 Errata Details                                     | 20 |

| 6.0 Specification Changes                              | 60 |

| 7.0 Specification Clarifications                       | 61 |

| 8.0 Documentation Changes                              | 62 |

December 2024

Doc. No.: 772415, Rev.: 012US

| Εı | u | r | e | S |

|----|---|---|---|---|

1 Processor Preliminary Top Side Marking (Example)......12

#### Tables—4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids

### **Tables**

| 1 | Component Identification via Capability Registers | . 10 |

|---|---------------------------------------------------|------|

|   | Errata Summary Table                              |      |

|   | Specification Changes                             |      |

|   | Specification Clarifications                      |      |

|   | Documentation Changes                             |      |

# **Revision History**

| Date          | Revision | Description                                                                                                              |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------|

| December 2024 | 012US    | Added errata SPR141 and SPR143.                                                                                          |

| November 2024 | 011US    | Added errata SPR137 to SPR140.                                                                                           |

| August 2024   | 010US    | Added errata SPR134 to SPR136.                                                                                           |

| June 2024     | 009US    | Added errata SPR129 to SPR133.                                                                                           |

| May 2024      | 008US    | Added errata SPR125 to SPR128.                                                                                           |

| March 2024    | 007US    | Added errata SPR123 and SPR124.                                                                                          |

| October 2023  | 006      | Added errata SPR120. to SPR122.                                                                                          |

| August 2023   | 005      | <ul><li>Added errata SPR118. to SPR119.</li><li>Updated errata SPR91.</li></ul>                                          |

| July 2023     | 004      | Added errata SPR115. to SPR117.                                                                                          |

| May 2023      | 003      | <ul> <li>Added errata SPR89. to SPR114.</li> <li>Updated errata status for SPR44., SPR66., SPR80., and SPR81.</li> </ul> |

| April 2023    | 002      | Added errata SPR82.to SPR88.     Updated the Component Identification via Registers                                      |

| February 2023 | 001      | Initial Release                                                                                                          |

December 2024

### 1.0 Preface

This document is an update to the specifications contained in the following table. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature on page 7 are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### 1.1 Related Documents

| Document Title                                                                                                                    | Document Number/<br>Location |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture                                       | 671436 <sup>1</sup>          |

| Intel® 64 and IA-32 Architectures Software Developer's Manual Combined Volumes 2A, 2B, 2C, and 2D: Instruction Set Reference, A-Z | 671110 <sup>1</sup>          |

| Intel® 64 and IA-32 Architectures Software Developer's Manual Combined Volumes 3A, 3B, 3C, and 3D: System Programming Guide       | 671447 <sup>1</sup>          |

| Eagle Stream Platform BIOS Writer's Guide                                                                                         | 613938 <sup>1</sup>          |

| ACPI Specifications                                                                                                               | www.acpi.info <sup>2</sup>   |

- Documents are available at https://www.intel.com/content/www/us/en/design/ resource-design-center.html.

- 2. Document available at www.uefi.org.

#### 1.2 Nomenclature

**Errata** are design defects or errors. These may cause the 4th Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processors' behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics, such as, core speed, L2 cache size, all notes associated with each S-Spec number.

**QDF Number** is a several-digit code used to distinguish between engineering samples. These processors are used for qualification and early design validation. The functionality of these parts can range from mechanical only to fully functional. The NDA specification update has a processor identification information table that lists these QDF numbers and the corresponding product sample details.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family

December 2024

Specification Update

Doc. No.: 772415, Rev.: 012US

4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family

Specification Update

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

#### **NOTE**

Errata remain in the specification update throughout the product's life cycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so forth).

December 2024

## 2.0 Identification Information

### 2.1 Component Identification via Programming Interface

The 4th Gen Intel® Xeon® Scalable Processors stepping can be identified by the following register contents:

| CPUID<br>(Offset:1A<br>h-19h)                   | Extended<br>Family ID <sup>1</sup> | Extended<br>Model <sup>2</sup> | Reser<br>ved | Processor<br>Type <sup>3</sup> | Processor<br>Family <sup>4</sup> | Processor<br>Model <sup>5</sup> | Processor<br>Stepping <sup>6</sup> |

|-------------------------------------------------|------------------------------------|--------------------------------|--------------|--------------------------------|----------------------------------|---------------------------------|------------------------------------|

| Bit                                             | 27:20                              | 19:16                          | 15:14        | 13:12                          | 11:8                             | 7:4                             | 3:0                                |

| XCC E-5/<br>E-4,<br>MCC S-3/<br>S-2,<br>HBM B-3 | 00000000Ь                          | 1000b                          |              | 0b                             | 0110b                            | 1111b                           | 1111b                              |

#### **NOTES**

- The Extended Family, bits [27:20] are used in conjunction with the Processor Family, specified in bits [11:8], to indicate whether the processor belongs to the Intel<sup>®</sup> 386<sup>™</sup>, Intel<sup>®</sup> 486<sup>™</sup>, Pentium<sup>®</sup>, Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> 4, Intel<sup>®</sup> Core<sup>™</sup> processor families, Intel<sup>®</sup> Core<sup>™</sup> ix families, and Intel<sup>®</sup> Xeon<sup>®</sup> processor families.

- 2. The Extended Model, bits [19:16] in conjunction with the Model Number, specified in bits [7:4], are used to identify the model of the processor within the processor's family.

- 3. The Processor Type, specified in bit [12] indicates whether the processor is an original OEM processor, an Intel® OverDrive processor, or a dual processor (capable of being used in a dual processor system).

- 4. The Processor Family corresponds to bits [11:8] of the EDX register after RESET, bits [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register accessible through Boundary Scan.

- 5. The Processor Model, bits [7:4] corresponds to bits [7:4] of the EDX register after RESET, bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register accessible through Boundary Scan.

- The Processor Stepping, bits [3:0] indicates the revision number of that model. See Table 1 on page 10 for the processor stepping ID number in the CPUID information.

To find the mapping between a processor's CPUID and its Family/Model number, see the Intel® 64 and IA-32 Architectures Software Developer Manual Combined Volumes.

4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family

December 2024

Doc. No.: 772415, Rev.: 012US

4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family

Specification Update

A complete description of the processor identification and feature determination is located in Chapter 20.

When EAX is set to a value of '1,' the CPUID instruction returns the Processor Family, Extended Model ID, Processor Type, Family, Model, and Stepping together referred as the processor signature value, in the EAX register. Note that after reset, the EDX processor will report the processor signature value in both the EDX and the EAX registers.

Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX, and EDX general purpose registers after the CPUID instruction is executed with a 2 in the EAX register. Special uses of general purpose registers include: EAX (Accumulator for operands and results data), EBX (Pointer to data in the DS segment), ECX (Counter for string and loop operations), and EDX (I/O pointer).

The 4th Gen Intel® Xeon® Scalable Processors Stepping can also be identified in 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids Registers Specification

Table 1. Component Identification via Capability Registers

|                  |          |                     |                 | SEGM | ENT¹ [Bit   | s 5:3]    | l         | SS <sup>2</sup> [Bits<br>0] |                                   | AL_CHO<br>ts 7:6] |

|------------------|----------|---------------------|-----------------|------|-------------|-----------|-----------|-----------------------------|-----------------------------------|-------------------|

| Physical<br>Chip | Stepping | SEGMENT,<br>WAYNESS | CPUID           | C    | Offset [B:3 | 31, D:30, | F:3] + 84 | h                           | Offset [B:31,<br>D:30, F:3] + 94h |                   |

|                  |          |                     |                 | 5    | 4           | 3         | 1         | 0                           | 7                                 | 6                 |

| XCC              | E-5/E-4  | Server, 1S          | 806F8/806<br>F7 | 1    | 1           | 1         | 0         | 0                           | 1                                 | 1                 |

| XCC              | E-5/E-4  | Server, 2S          | 806F8/806<br>F7 | 1    | 1           | 1         | 0         | 1                           | 1                                 | 1                 |

| XCC              | E-5/E-4  | Server, 4S          | 806F8/806<br>F7 | 1    | 1           | 1         | 1         | 0                           | 1                                 | 1                 |

| XCC              | E-5/E-4  | Server, 8S          | 806F8/806<br>F7 | 1    | 1           | 1         | 1         | 1                           | 1                                 | 1                 |

| MCC              | S-3/S-2  | Server, 1S          | 806F8/806<br>F7 | 1    | 1           | 1         | 0         | 0                           | 0                                 | 1                 |

| MCC              | S-3/S-2  | Server, 2S          | 806F8/806<br>F7 | 1    | 1           | 1         | 0         | 1                           | 0                                 | 1                 |

| MCC              | S-3/S-2  | Server, 4S          | 806F8/806<br>F7 | 1    | 1           | 1         | 1         | 0                           | 0                                 | 1                 |

| НВМ              | B-3      | Server, 1S          | 806F8           | 1    | 1           | 1         | 0         | 0                           | 1                                 | 1                 |

| НВМ              | B-3      | Server, 2S          | 806F8           | 1    | 1           | 1         | 0         | 1                           | 1                                 | 1                 |

| НВМ              | B-3      | Server, 4S          | 806F8           | 1    | 1           | 1         | 1         | 0                           | 1                                 | 1                 |

December 2024

#### **NOTES**

- 1. The SEGMENT, bits [5:3] corresponds to 111: Server; 011: Server-FPGA; 001: Server-Fabric; 100: HPC; 110: Server-Atom; 010: Workstation; 000: HEDT; Others: Reserved.

- 2. The WAYNESS, bits [1:0] corresponds to 00=1S, 01=2S, 10=4S, 11=8S.

- 3. The PHYSICAL\_CHOP, bits [7:6] corresponds to 11:XCC; 01:MCC; 11:HBM.

The 4th Gen Intel® Xeon® Scalable Processors Capability Registers can also be identified in 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids Registers Specification .

4th Gen Intel ® Xeon ® Processor Scalable Family

December 2024 Specification Update

Doc. No.: 772415, Rev.: 012US

# 3.0 Component Marking Information

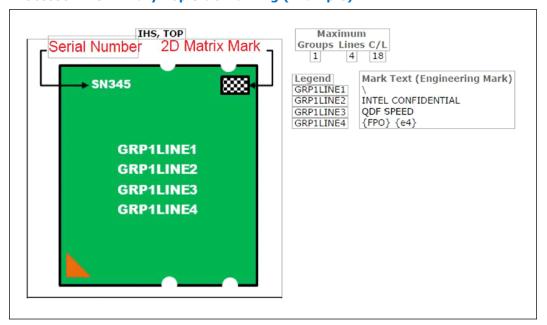

The 4th Gen Intel<sup>®</sup> Xeon<sup>®</sup> Processor Scalable Family can be identified by the following register markings.

Figure 1. Processor Preliminary Top Side Marking (Example)

For 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids SKUs, see 4th Gen Intel® Xeon® Scalable Processors.

December 2024

#### 4.0 **Summary Tables of Changes**

The following tables indicate the Specification Changes, Errata, Specification Clarifications, or Documentation Changes which apply to the 4th Gen Intel® Xeon® Scalable Processors product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables use the following notations:

#### **Codes Used in Summary Tables** 4.1

| Stepping                 | Description                                                                                         |

|--------------------------|-----------------------------------------------------------------------------------------------------|

| (No mark) or (Blank box) | This erratum is fixed in listed stepping or specification change does not apply to listed stepping. |

| Status      | Description                                                    |  |  |  |  |

|-------------|----------------------------------------------------------------|--|--|--|--|

| Doc         | Document change or update will be implemented.                 |  |  |  |  |

| Planned Fix | This erratum may be fixed in a future stepping of the product. |  |  |  |  |

| Fixed       | This erratum has been previously fixed.                        |  |  |  |  |

| No Fix      | There are no plan to fix this erratum.                         |  |  |  |  |

#### 4.2 **Errata Summary Table**

#### Table 2. **Errata Summary Table**

| Erratum<br>ID | Proces<br>sor<br>Steppi<br>ng XCC<br>E-5 | Proces<br>sor<br>Steppi<br>ng MCC<br>S-3 | Processor<br>Stepping<br>HBM B-3 | Title                                                                                                                         |

|---------------|------------------------------------------|------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPR1          | No Fix                                   | No Fix                                   | No Fix                           | IPSR May Not Function Correctly                                                                                               |

| SPR2          | No Fix                                   | No Fix                                   | No Fix                           | Poison Data Reported Instead of a CS Limit Violation                                                                          |

| SPR3          | No Fix                                   | No Fix                                   | No Fix                           | Monitor Instructions to Legacy VGA Region May Fail                                                                            |

| SPR4          | No Fix                                   | No Fix                                   | No Fix                           | TILEDATA State May Be Saved Incorrectly                                                                                       |

| SPR5          | No Fix                                   | No Fix                                   | No Fix                           | A Poison Data Event May Not be Serviced if a Data Breakpoint Occurs on an AMX Tile-Load or AVX Gather or REP MOVS Instruction |

| SPR6          | No Fix                                   | No Fix                                   | No Fix                           | IFS MSRs Will Ignore a Non-Zero EDX Value And Not Signal a #GP                                                                |

| SPR7          | No Fix                                   | No Fix                                   | No Fix                           | Processor May Signal Spurious #GP Fault                                                                                       |

| SPR8          | No Fix                                   | No Fix                                   | No Fix                           | A Break Point May be Hit Twice When a VM Exit Without Commit Occurs                                                           |

| SPR9          | No Fix                                   | No Fix                                   | No Fix                           | Faulted XRSTORS Instruction May Result in Unexpected X87 FTW Value                                                            |

| SPR10         | No Fix                                   | No Fix                                   | No Fix                           | Error Conditions Detected During Cold Reset May Not be Cleared by Subsequent Warm Reset                                       |

|               |                                          |                                          |                                  | continued                                                                                                                     |

December 2024 Doc. No.: 772415, Rev.: 012US

| Erratum<br>ID | Proces<br>sor<br>Steppi<br>ng XCC<br>E-5 | Proces<br>sor<br>Steppi<br>ng MCC<br>S-3 | Processor<br>Stepping<br>HBM B-3 | Title                                                                                                                                                          |  |

|---------------|------------------------------------------|------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SPR11         | No Fix                                   | No Fix                                   | No Fix                           | DSA/IAX Does Not Log The E2E Prefix Bit And The Prefix-Type Bits in AERTLPPLOG1                                                                                |  |

| SPR12         | No Fix                                   | No Fix                                   | No Fix                           | The Processor May Drop Noncompliant Posted Peer-to-peer Transactions                                                                                           |  |

| SPR13         | No Fix                                   | No Fix                                   | No Fix                           | Certain Bits in IA32_MC5_STATUS Register Will Always Return 0                                                                                                  |  |

| SPR14         | No Fix                                   | No Fix                                   | No Fix                           | Occupancy Interrupt Handle is Not Checked Against Interrupt Table Size                                                                                         |  |

| SPR15         | No Fix                                   | No Fix                                   | No Fix                           | Processor May Incorrectly Set PFD Assisted in Correction Bit in Memory Controller                                                                              |  |

| SPR16         | No Fix                                   | No Fix                                   | No Fix                           | DSA CMDSTATUS Register May Not Reflect Correct Hardware Status                                                                                                 |  |

| SPR17         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware May Set Access/Dirty Bits in a First-stage Page-table Entry                                                                                 |  |

| SPR18         | No Fix                                   | No Fix                                   | No Fix                           | System Software May Not Receive Intel® Virtualization Technology (Intel® VT) for Directed I/O (Intel® VT-d) Fault SPT.3 For Non-Zero Writes to b[191:HAW +128] |  |

| SPR19         | No Fix                                   | No Fix                                   | No Fix                           | APCTL.APNGE Should be RW Instead of RWS                                                                                                                        |  |

| SPR20         | No Fix                                   | No Fix                                   | No Fix                           | CXL Device May Not Receive Viral                                                                                                                               |  |

| SPR21         | No Fix                                   | No Fix                                   | No Fix                           | OOBMSM TSC Will be 320ns Behind The Globally Aligned Counter                                                                                                   |  |

| SPR22         | No Fix                                   | No Fix                                   | No Fix                           | Performance Monitoring Event Coherent_ops May Undercount                                                                                                       |  |

| SPR23         | No Fix                                   | No Fix                                   | No Fix                           | PCIe Link Re-Equalization May Not Occur if Link is in L1 State                                                                                                 |  |

| SPR24         | No Fix                                   | No Fix                                   | No Fix                           | Machine Check Bank 4 UCNA Errors May Not be Signaled                                                                                                           |  |

| SPR25         | No Fix                                   | No Fix                                   | No Fix                           | DSA/IAA Use of Priv and PASID                                                                                                                                  |  |

| SPR26         | No Fix                                   | No Fix                                   | No Fix                           | Reserved(0) Check For a PASID Table Entry May Not Happen For a DMA Request                                                                                     |  |

| SPR27         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware May Not Generate a Page Request Group Response<br>Message While Operating in Legacy Mode or Abort DMA Mode                                  |  |

| SPR28         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware May Abort ZLR to Second-Stage Write Only Pages                                                                                              |  |

| SPR29         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware with Major Version Number 6 Incorrectly Advertises the ESRTPS Support                                                                       |  |

| SPR30         | No Fix                                   | No Fix                                   | No Fix                           | Platform May Hang if System Software Sends a Page Group Response or DevTLB Invalidation to Non-existent Requester ID                                           |  |

| SPR31         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware Does Not Perform Reserved (0) Check in Page Response Descriptor                                                                             |  |

| SPR32         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware Implements b[31:16] of the three Event Data Registers (VTDBAR offsets 0x3C, 0xA4, and 0xE4) as Read-Writable                                |  |

| SPR33         | No Fix                                   | No Fix                                   | No Fix                           | IAA Do Not Report Overlap Errors For AECS Size of 2GB or Greater                                                                                               |  |

| SPR34         | No Fix                                   | No Fix                                   | No Fix                           | DSA/IAA Invalid TC Not Reported in The SWERROR Register                                                                                                        |  |

| SPR35         | No Fix                                   | No Fix                                   | No Fix                           | IAA Unaligned Completion Record Address Error is Not Reported in SWERROR Register                                                                              |  |

| SPR36         | No Fix                                   | No Fix                                   | No Fix                           | Intel® UPI Link Not Resetting When L1 Mismatch Occurs Between Local and Remote Sockets                                                                         |  |

| SPR37         | No Fix                                   | No Fix                                   | No Fix                           | DSA/IAA May Fail to Log an MDPE Error For Back-to-Back Parity Errors                                                                                           |  |

December 2024 Doc. No.: 772415, Rev.: 012US

| Erratum<br>ID | Proces<br>sor<br>Steppi<br>ng XCC<br>E-5 | Proces<br>sor<br>Steppi<br>ng MCC<br>S-3 | Processor<br>Stepping<br>HBM B-3 | Title                                                                                                              |

|---------------|------------------------------------------|------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------|

| SPR38         | No Fix                                   | No Fix                                   | No Fix                           | Relaxed Ordering Not Disabled by DEVCTL.ERO bit for DSA/IAA Upstream Transactions                                  |

| SPR39         | No Fix                                   | No Fix                                   | No Fix                           | System Address Logged For WDB Parity Errors May be Incorrect                                                       |

| SPR40         | No Fix                                   | No Fix                                   | No Fix                           | Incorrect MCACOD For L2 MCE                                                                                        |

| SPR41         | No Fix                                   | No Fix                                   | No Fix                           | System May Hang Due to Full LLRB                                                                                   |

| SPR42         | No Fix                                   | No Fix                                   | No Fix                           | IAA May Fail to Properly Decode Data With a Large Header                                                           |

| SPR43         | No Fix                                   | No Fix                                   | No Fix                           | Memory Controller Violates JEDEC RCD tCSALT Timing                                                                 |

| SPR44         | Fixed                                    | Fixed                                    | Fixed                            | Wrong CKE Signal Used on 1 DPC 3DS 4H Configs                                                                      |

| SPR45         | No Fix                                   | No Fix                                   | No Fix                           | Address May Not be Logged For a UCR Error Detected in The MLC                                                      |

| SPR46         | No Fix                                   | No Fix                                   | No Fix                           | VT-d DMA Remapping Hardware May Hang if it Encounters Page Request<br>Queue Overflow Condition                     |

| SPR47         | No Fix                                   | No Fix                                   | No Fix                           | Receiver Common Mode Input Impedance May be Below Specification When Interface is Powered Down                     |

| SPR48         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware Will Not Report The PASID Value For RTA.2 Faults in Modes Other Than Scalable Mode              |

| SPR49         | No Fix                                   | No Fix                                   | No Fix                           | Remapping Hardware Does Not Perform a Reserved(0) Check in Interrupt<br>Remap Table Entry                          |

| SPR50         | No Fix                                   | No Fix                                   | No Fix                           | Processor PCIe Root Port Link Spurious Data Parity Error May be Reported                                           |

| SPR51         | No Fix                                   | No Fix                                   | No Fix                           | Mismatch Between UboxErrMisc and MCI_STATUS Registers Error Logs                                                   |

| SPR52         | No Fix                                   | No Fix                                   | No Fix                           | CHA UCNA Errors May be Incorrectly Controlled by MCi_CTL Enable Bits                                               |

| SPR53         | No Fix                                   | No Fix                                   | No Fix                           | Reading The PPERF MSR May Not Return Correct Values                                                                |

| SPR54         | No Fix                                   | No Fix                                   | No Fix                           | No #GP Will be Signaled When Setting MSR_MISC_PWR_MGMT.ENABLE_SDC if MSR_MISC_PWR_MGMT.LOCK is Set                 |

| SPR55         | No Fix                                   | No Fix                                   | No Fix                           | System May Experience an Internal Timeout Error When an Internal Parity Error Occurs While Working With Intel® AMX |

| SPR56         | No Fix                                   | No Fix                                   | No Fix                           | Last Branch Records May Not Survive Warm Reset                                                                     |

| SPR57         | No Fix                                   | No Fix                                   | No Fix                           | Single Step on Branches Might be Missed When VMM Enables Notification On VM Exit                                   |

| SPR58         | No Fix                                   | No Fix                                   | No Fix                           | Incorrect #CP Error Code on UIRET                                                                                  |

| SPR59         | No Fix                                   | No Fix                                   | No Fix                           | #GP May be Serviced Before an Instruction Breakpoint                                                               |

| SPR60         | No Fix                                   | No Fix                                   | No Fix                           | Unexpected #PF Exception Might Be Serviced Before a #GP Exception                                                  |

| SPR61         | No Fix                                   | No Fix                                   | No Fix                           | VMX-Preemption Timer May Not Work if Configured With a Value of 1                                                  |

| SPR62         | No Fix                                   | No Fix                                   | No Fix                           | User Interrupt Might be Delayed                                                                                    |

| SPR63         | No Fix                                   | No Fix                                   | No Fix                           | VM Exit Qualification May Not be Correctly Set on APIC Access While Serving a User Interrupt                       |

| SPR64         | No Fix                                   | No Fix                                   | No Fix                           | Software Tuning That Relies on PCLS Values May Experience Inaccurate Event Counts                                  |

| SPR65         | No Fix                                   | No Fix                                   | No Fix                           | Multiple SGX_Doorbell_Errors on Ubox Response Mismatch                                                             |

| SPR66         | Fixed                                    | Fixed                                    | Fixed                            | ECS Readout Fails on Mixed Mode Systems                                                                            |

|               |                                          |                                          |                                  | continued                                                                                                          |

December 2024 Specification Update

Doc. No.: 772415, Rev.: 012US

4th Gen Intel ® Xeon ® Processor Scalable Family

Specification Update

| SPR68 No Fix No Fix No Fix Intel® IAA Expand Operation With PRLE Format Input May Return an Er SPR69 No Fix No Fix No Fix No Fix Intel® IAA Expand Operation With PRLE Format Input May Return an Er Intel® IAA Compression with Compress Bit Order Set May Produce an Compression No Fix No Fix No Fix No Fix Intel® IAA Source 2 Not Written Properly When Source 2 Size is 32 Byth SPR71 No Fix No Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source 2 Size is 32 Byth Spr72 No Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source 2 Size is 32 Byth Spr73 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation Spr873 No Fix No Fix No Fix Invalid Flags Field of The Completion Registers May be Incorrect Updated  Spr874 No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Intel® IAA Compression Operation  Spr875 No Fix No Fix No Fix With Intel® SGX Disabled, Software That Relies on ENCLVexiting May No Function as Expected  Spr876 No Fix No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message If a Nor Error Docurs in The Same Cycle  Spr878 No Fix No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  Spr879 No Fix No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  Spr880 No Fix No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate Pa Supervisor Privilege Translations  Spr881 No Fix No Fix No Fix No Fix UPI Machine Check Bank May Not Report an Incorrect Value  Spr883 No Fix No Fix No Fix No Fix PECT Wire Host may Continuously Receive a Completion Code of 0x80  Spr884 No Fix No Fix No Fix No Fix PECT Wire Host may Continuously Receive a Completion Code of 0x80  Spr885 No Fix No Fix No Fix No Fix PECT Wire Host may Continuously Receive a Com | Erratum<br>ID | Proces<br>sor<br>Steppi<br>ng XCC<br>E-5 | Proces<br>sor<br>Steppi<br>ng MCC<br>S-3 | Processor<br>Stepping<br>HBM B-3 | Title                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| SPR69 No Fix No Fix No Fix Intel® IAA Compression with Compress Bit Order Set May Produce and Number of Bytes  SPR70 No Fix No Fix No Fix Intel® IAA Source 2 Not Written Properly When Source 2 Size is 32 Bytes  SPR71 No Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source Coder Field is Set  SPR72 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation  SPR73 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation  SPR74 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation  SPR75 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation  SPR76 No Fix No Fix No Fix Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrect Intel IAA Compression Operation  SPR77 No Fix No Fix No Fix Intel® DSA/Intel® SGX Disabled, Software That Relies on ENCLVexiting May No Function as Expected  SPR77 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR84 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR85 No Fix No Fix No Fix No Fix Intel® PECI Wire Host may Continuously Receive a Completion Code of 0x80  SP | SPR67         | No Fix                                   | No Fix                                   | No Fix                           | Intel® DSA/Intel® IAA Completion Record is Not Written For Non-Completion Record Invalid Traffic Classes                          |

| SPR70 No Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source 2 Not Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source 2 Not Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source 2 Not Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation Spr73 No Fix No Fix No Fix Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrect Updated  Spr74 No Fix No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Fintel IAA Compression Operation  Spr75 No Fix No Fix No Fix With Intel® SGX Disabled, Software That Relies on ENCLVexiting May No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Fintel IAA Compression Operation  Spr76 No Fix No Fix No Fix With Intel® SGX Disabled, Software That Relies on ENCLVexiting May No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nore Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nore Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  Spr79 No Fix No Fix No Fix Intel® Aps. Intel® DASA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  Spr80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  Spr81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidation Completion Ordering  Spr83 No Fix No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  Spr88 Fixed Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  Spr883 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of Ox80  Spr885 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of Ox80  Spr886 No Fix No Fix No Fix No | SPR68         | No Fix                                   | No Fix                                   | No Fix                           | Intel® IAA Expand Operation With PRLE Format Input May Return an Error                                                            |

| SPR71 No Fix No Fix No Fix Intel® IAA May Not Report Invalid Filter Flags Status Code When Source SPR72 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrect Updated  SPR73 No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Intel IAA Compression Operation  SPR74 No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Intel IAA Compression Operation  SPR75 No Fix No Fix No Fix No Fix With Intel® SQX Disabled, Software That Relies on ENCLVexiting May No Fix Function as Expected  SPR76 No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect  SPR77 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Ferror Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly SPR86 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR85 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR86 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR87 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR88 No Fix No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC_DDR5_9x4_half_device Bit Maybe Incorrect  | SPR69         | No Fix                                   | No Fix                                   | No Fix                           | Intel® IAA Compression with Compress Bit Order Set May Produce an Odd Number of Bytes                                             |

| SPR72 No Fix No Fix No Fix Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrect Updated  SPR74 No Fix No Fix No Fix Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrect Updated  SPR75 No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly fintel IAA Compression Operation  SPR76 No Fix No Fix No Fix No Fix With Intel® SGX Disabled, Software That Relies on ENCLVexiting May Not Described Function as Expected  SPR77 No Fix No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix No Fix DR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR84 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR85 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR86 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR87 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR88 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Corde of 0x80  SPR88 No Fix No Fix No Fix No Fix PROM_IP Value For an RTM Abort in BTM or BTS May be Obserted S | SPR70         | No Fix                                   | No Fix                                   | No Fix                           | Intel® IAA Source 2 Not Written Properly When Source 2 Size is 32 Bytes                                                           |

| SPR73 No Fix No Fix No Fix Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrect Updated  SPR74 No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Fintel IAA Compression Operation  SPR75 No Fix No Fix No Fix Intel® SGX Disabled, Software That Relies on ENCLVexiting May Ne Function as Expected  SPR76 No Fix No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect  SPR77 No Fix No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate Passupervisor Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No F | SPR71         | No Fix                                   | No Fix                                   | No Fix                           | Intel® IAA May Not Report Invalid Filter Flags Status Code When Source 2 Bi<br>Order Field is Set                                 |

| SPR74 No Fix No Fix No Fix Invalid Flags Field of The Completion Record May Not be Set Correctly Fintel ItaA Compression Operation  SPR75 No Fix No Fix No Fix No Fix Punction as Expected  SPR76 No Fix No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect  SPR77 No Fix No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrect SPR85 No Fix  | SPR72         | No Fix                                   | No Fix                                   | No Fix                           | Intel® IAA Does Not Allow Source 1 Size to be 0 For Expand Operation                                                              |

| SPR75 No Fix No Fix No Fix With Intel® SGK Disabled, Software That Relies on ENCLVexiting May No Fix Punction as Expected  SPR76 No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect  SPR77 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR85 No Fix No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect SPR87 No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obser SPR90 No Fix No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obser SPR91 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obser SPR91 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obser SPR91 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                       | SPR73         | No Fix                                   | No Fix                                   | No Fix                           | Intel® DSA/Intel® IAA And WQ Configuration Registers May be Incorrectly Updated                                                   |

| Function as Expected  SPR76 No Fix No Fix No Fix Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may Incorrect  SPR77 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA Compression Output Buffer Overflow Error May be Incorrect Reported  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR85 No Fix No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR86 No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect  SPR87 No Fix No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obsel  SPR89 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obsel  SPR90 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                       | SPR74         | No Fix                                   | No Fix                                   | No Fix                           | Invalid Flags Field of The Completion Record May Not be Set Correctly For Intel IAA Compression Operation                         |

| Incorrect  SPR77 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Nor Error Occurs in The Same Cycle  SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PAS SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Error SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80 SPR85 No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR86 No Fix No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obserted Document of Ways For The Load DTLB  SPR90 No Fix No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obserted Document of Ways For The Load DTLB  SPR91 No Fix No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPR75         | No Fix                                   | No Fix                                   | No Fix                           | With Intel® SGX Disabled, Software That Relies on ENCLVexiting May Not Function as Expected                                       |

| SPR78 No Fix No Fix No Fix Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error Invalid ATS Response  SPR79 No Fix No Fix No Fix Intel® DSA/Intel® IAA Compression Output Buffer Overflow Error May be Incorrectly Reported  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR85 No Fix No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR86 No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect SPR87 No Fix No Fix No Fix An MDF Parity Error May Incorrect Set The Overflow Bit  SPR88 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obset SPR90 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SPR76         | No Fix                                   | No Fix                                   | No Fix                           | Headers Logged in AERHDRLOG for an AER Error for Intel DSA/IAA may be Incorrect                                                   |

| SPR80 No Fix No Fix No Fix Intel® IAA Compression Output Buffer Overflow Error May be Incorrectly Reported  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PAS SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Error SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80 SPR85 No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR86 No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect SPR87 No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obsel SPR90 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obsel SPR91 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPR77         | No Fix                                   | No Fix                                   | No Fix                           | Intel® DSA/Intel® IAA May Fail to Send an ERR_FATAL Message if a Non-Fat Error Occurs in The Same Cycle                           |

| Reported  SPR80 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator May Violate ATS Invalidation Completion Ordering  SPR81 No Fix No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80 SPR85 No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR86 No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect SPR87 No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obset SPR90 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SPR78         | No Fix                                   | No Fix                                   | No Fix                           | Intel® DSA/Intel® IAA May Fail to Log an Unexpected Completion Error For a Invalid ATS Response                                   |

| SPR81 No Fix No Fix Intel® QuickAssist Technology Accelerator Device May Not Invalidate PA SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR85 No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR86 No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect  SPR87 No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix An MDF Parity Error May Incorrect Set The Overflow Bit  SPR89 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obsel  SPR90 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPR79         | No Fix                                   | No Fix                                   | No Fix                           | Intel® IAA Compression Output Buffer Overflow Error May be Incorrectly Reported                                                   |

| SupervisorPrivilege Translations Privilege Translations  SPR82 Fixed Fixed Fixed The Time-Stamp Counter May Report an Incorrect Value  SPR83 No Fix No Fix No Fix UPI Machine Check Bank May Not Report The Most Recently Logged Err  SPR84 No Fix No Fix No Fix PECI Wire Host may Continuously Receive a Completion Code of 0x80  SPR85 No Fix No Fix No Fix DDR5 9x4 DIMMs ECS Data May be Reported Incorrectly  SPR86 No Fix No Fix No Fix RETRY_RD_ERR_LOG_MISC.DDR5_9x4_half_device Bit Maybe Incorrect  SPR87 No Fix No Fix No Fix PIROM Reports The Wrong 2 DPC Speed For Processors With Less Than MT/s 1 DPC Speed  SPR88 No Fix No Fix No Fix An MDF Parity Error May Incorrect Set The Overflow Bit  SPR89 No Fix No Fix No Fix Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Obsel  SPR90 No Fix No Fix No Fix Intel® PT Trace May Contain Incorrect Data When Configured With Sing Range Output Larger Than 4KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPR80         | No Fix                                   | No Fix                                   | No Fix                           |                                                                                                                                   |