### **Product Brief**

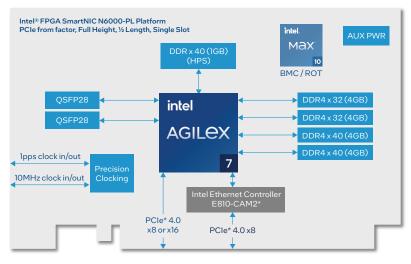

Intel® FPGA SmartNIC N6000-PL Platform

# intel

## A SmartNIC for Accelerating Communications and Networking Workloads

### 2x100Gb Ethernet Connectivity

IEEE 1588v2 PTP O-RAN/Broadcast

#### PCIe Form Factor FHHL

On-board Intel® Ethernet Controller E810\* Easy System Integration The Intel® FPGA SmartNIC N6000-PL Platform is Intel's 3rd generation SmartNIC providing 2x100 Gbps Ethernet connectivity. It is based on Intel Agilex® 7 FPGA F-Series family built with advanced 10 nm SuperFin technology delivering ~2X better fabric performance per watt compared to competing 7 nm FPGAs.

#### \*The N6000-based SmartNICs come in two configurations:

- $N6000-based\,SmartNIC\,with\,an\,Intel^{\circledast}\,Ethernet\,Controller\,E810\,and\,bifurcated\,PCIe\,4.0\,x8\,Ianes\,to\,FPGA\,and\,x8\,Ianes\,to\,the\,Ethernet\,controller$

- N6001-based SmartNIC without an Ethernet controller, PCIe 4.0 x16 lanes to FPGA

### Accelerate Data From Edge to Cloud

#### **Flexible and Scalable Platform**

- Reference workloads available on production-ready boards

- Open FPGA Interface Manager (FIM) available for custom workload development

- Board design licensed to accelerate any custom board variant

#### **Easy Software Integration**

- SR-IOV-based standard host Interface using Intel Ethernet controller E810 requires no application code changes

- Open and standardized application programming interfaces (APIs) for Data Plane Development Kit (DPDK) PMD, and BBDev (vRAN only)

#### Synchronized Timing Solution

- Support 1588v2 PTP synchronization PRTC/T-GM, T-BC, T-TC, T-TSC clocks

- SyncE support

- On-board oven-controlled oscillator provides timing accuracy and extended hold-over

Product Brief | A SmartNIC for Accelerating Communications and Networking Workloads

### Use Cases

$Work load \ designs \ for \ the \ N6000 \ Platform \ are \ developed \ and \ available \ through \ Intel \ and \ Partners.$

| Use cases                                                                                                                                                                                            | Configurations          | Key Features                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>5G vRAN</b><br>All-in-one architecture encompassing<br>xHaul+ FEC + 1588 reduces total cost of<br>ownership (TCO)                                                                                 | 2x4x10G<br>2x2x25G      | <ul> <li>Support for Split 7-2X ORAN radios</li> <li>G.8273.2 1588 PTP conformance testing</li> <li>LDPC Gen 3.0 with URLLC support</li> <li>Open APIs for DPDK PMD and BBDev to ease software integration</li> </ul>                                                                                                                           |

| Accelerated Virtual Cell Site Router<br>(vCSR)<br>All-in-one architecture encompassing<br>vRouter + 1588 +optional FHGW <sup>(1)</sup> + Optional<br>FEC <sup>(1)</sup> offering lower latency & TCO | 4x25G<br>2x25G<br>7x10G | <ul> <li>Control &amp; Data Plane run on N6000</li> <li>G.8273.2 PTP Conformance testing</li> <li>Optional hierarchical quality of service (HQoS)</li> <li>Open APIs for easy software integration</li> <li>Ready for network slicing</li> <li>MPLS auto provisioning</li> </ul>                                                                |

| <b>5G User Plane Function (UPF) Offload</b><br>Low latency/jitter solution optimized for<br>edge deployment where space and power<br>are constrained                                                 | 2x100GbE                | <ul> <li>Flow-based approach with 8M flows</li> <li>VLAN for N3/N6 identification, IPv4 and IPv6, GTPv1</li> <li>Up to 1 million policers</li> <li>Each flow supports up to 2 policers</li> <li>Up to 8 million counters, 2 counters per flow</li> <li>100G ingress NAT for IPv4</li> </ul>                                                     |

| SMTE ST2110 Offload with JPEG-XS<br>Nearly zero host core are used in<br>professional video production workloads                                                                                     | 2x100GbE                | <ul> <li>Video, audio, ancillary data and RTP header processing</li> <li>Packet pacer compliant with ST2110-21 (Type N, NL)</li> <li>Hitless protection switching (ST2022-7, up to class-C)</li> <li>High performant MCDMA</li> <li>Complete SDK including C/C++ API and Gstreamer plugin</li> <li>NMOS IS-04/IS-05 node application</li> </ul> |

$^{(\mathrm{l})}\mathsf{Additional}\,\mathsf{functionality}\,\mathsf{can}\,\mathsf{be}\,\mathsf{added}\,\mathsf{depending}\,\mathsf{on}\,\mathsf{available}\,\mathsf{device}\,\mathsf{resources}$

### Ordering Information

#### Production-Ready COTS Board

N6000-based SmartNIC commercial-off-the-shelf (COTS) board and workloads are available through ODM partners. Open FPGA Stack (OFS)-based FPGA Interface Manager (FIM) designs are also available to accelerate custom workload development.

|                     |                                       | Silicom Led.<br>Connectivity Solutions<br>N6010 SmartNIC |                           |  |

|---------------------|---------------------------------------|----------------------------------------------------------|---------------------------|--|

| Intel ODM Partner   | WNC                                   | Silicom                                                  | Art/za<br>Networks        |  |

| FPGA Device on Boar | Intel Agilex <sup>®</sup> FPGA AGF014 | Intel Agilex® FPGA AGF014                                | Intel Agilex® FPGA AGF027 |  |

| Form Factor         | FHHL                                  | FHHL                                                     | FH3/4L                    |  |

| ODM/Partner Website | FPGA SmartNIC WSN6050<br>Series       | Silicom FPGA SmartNIC                                    | Artiza FPGA SmartNIC      |  |

#### **Licensed Design**

Accelerate custom board design by re-using the N6000 board design and tailoring it to your unique requirements. The Intel FPGA SmartNIC N6000-PL Platform consists of:

- Board design files

- OFS, FIM designs

- BMC design

- Reference workloads

- Documentation

- Sample card

To license the Intel FPGA SmartNIC N6000-PL/N6001-PL Platform design, contact an Intel sales representative.

### Intel FPGA SmartNIC N6000-PL Platform Specifications

| Configurations                  | Intel® FPGA SmartNIC N6000-PL Platform                                                                                                                                                                                                                                                                                                                                                            | Intel® FPGA SmartNIC N6001-PL Platform                                                                                                                                 |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                 | Hardware                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |

| FPGA                            | <ul> <li>Intel Agilex FPGA F-Series AGF014 (AGFB014R24A2E2V)</li> <li>High-performance F-Series FPGAs, multi-gigabit SERDES transceivers up to 58 Gb</li> <li>Integrated 64-bit quad core Arm® Cortex A-53 MP core Hard Process System (HPS)</li> <li>1,437K logic elements</li> <li>190 Mb on-chip memory</li> <li>4,510 DSP blocks</li> </ul>                                                   |                                                                                                                                                                        |  |  |  |

| Onboard Memory                  | <ul> <li>16 GB DDR4 to FPGA         <ul> <li>2 Channels x40 (x32 Data + x8ECC), 1200 MHz (2400Mbps) 4 GB (Total 8GB)</li> <li>2 Channels x32 (x32 Data no ECC), 1200 MHz (2400Mbps), 4 GB (Total 8 GB)</li> </ul> </li> <li>1 GB DDR4 to HPS         <ul> <li>1 Channel x40 (x32 Data + x8ECC), 1200 MHz (DDR4-2400) 1GB</li> </ul> </li> </ul>                                                   |                                                                                                                                                                        |  |  |  |

| PCIe Interface                  | PCIe 4.0 bifurcated x8/x8                                                                                                                                                                                                                                                                                                                                                                         | PCIe 4.0 X16                                                                                                                                                           |  |  |  |

| Network Interface               | <ul> <li>Two QSFP 28/56 connectors</li> <li>2x1x100 Gbps, 2x2x50 Gbps, 2x4x25 Gbps, 2x4x10 Gbps</li> <li>Support for CPRI, eCPRI</li> </ul>                                                                                                                                                                                                                                                       |                                                                                                                                                                        |  |  |  |

| Network Interface<br>Controller | <ul> <li>On-board Intel E810-CAM2 Ethernet Controller         <ul> <li>Extensive OS support and SR-IOV enables easier system integration</li> <li>100 Gbps Packet processing Pipeline and Virtualization support</li> </ul> </li> </ul>                                                                                                                                                           | <ul> <li>No on-board Ethernet controller</li> </ul>                                                                                                                    |  |  |  |

| Timing Synchronization          | <ul> <li>IEEE 1588v2 support for PRTC/T-GM, T-BC, T-TSC, T-TC</li> <li>O-RAN S-Plane PTP support (G.8275.1) for LLS-C1, -C2, -C3, -C4</li> <li>Support for Synchronous Ethernet (SyncE)</li> <li>Class B frequency and phase timing accuracy</li> <li>Integrated OCXO for holdover performance</li> <li>Timing interface for local PRTC support for ToD with 1PPS/10MHz SMA connectors</li> </ul> |                                                                                                                                                                        |  |  |  |

| Form Factor                     | Full Height Half Length (FHHL) Single Slot                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                        |  |  |  |

| Thermal/Power                   | <ul> <li>Passively cooled</li> <li>Thermal design power(TDP*) – 125W</li> <li>Scenario design power (SDP) &lt;100 W (Power consumption dependent on workload)</li> <li>NEBS Class 1 compliance support</li> </ul>                                                                                                                                                                                 | <ul> <li>Passively cooled</li> <li>Thermal design power(TDP*) – 75W</li> <li>Scenario design power (SDP) &lt;75 W (Power consumption dependent on workload)</li> </ul> |  |  |  |

| ATX Connector                   | 2x3 Pin 12V Aux Connector                                                                                                                                                                                                                                                                                                                                                                         | Not Required                                                                                                                                                           |  |  |  |

| Board Management                | <ul> <li>Intel® MAX 10 FPGA BMC</li> <li>Full security implementation using Intel MAX 10 FPGA as RoT</li> <li>Remote update capabilities for FPGA flash memory and BMC</li> <li>Full card BMC solution host communication via SMBus and PCIe VDM</li> </ul>                                                                                                                                       |                                                                                                                                                                        |  |  |  |

| Power Management                | Intelligent system power management with real-time telemetry and system health monitoring                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                        |  |  |  |

Product Brief | A SmartNIC for Accelerating Communications and Networking Workloads

| Configurations     | Intel® FPGA SmartNIC N6000-PL Platform                                                                                                                                                               | Intel® FPGA SmartNIC N6001-PL Platform                                                              |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| Software           |                                                                                                                                                                                                      |                                                                                                     |  |  |  |  |

| Software           | <ul> <li>Data Plane Development Kit (DPDK)</li> <li>FlexRAN (BBDev (pf-bb-config)) for vRAN only</li> <li>Open Programmable Acceleration Engine<br/>(OPAE)</li> <li>Open FPGA Stack (OFS)</li> </ul> | <ul> <li>Open Programmable Acceleration Engine<br/>(OPAE)</li> <li>Open FPGA Stack (OFS)</li> </ul> |  |  |  |  |

| Design Entry Tools |                                                                                                                                                                                                      |                                                                                                     |  |  |  |  |

| Design Entry Tool  | <ul> <li>Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition Software</li> <li>oneAPI</li> </ul>                                                                                                 |                                                                                                     |  |  |  |  |

\*TDP not relevant to deployment power. TDP only used for server thermal design

#### **Custom Workload Development**

Develop custom workloads by leveraging pre-built FPGA Interface Manager (FIM) designs created by Open FPGA Stack (OFS). OFS is a scalable, source-accessible hardware and software reference infrastructure that provides all components to interface custom workloads to the host. FIMs are designed to be modular and scalable to help ease development. FIMs, OFS Software & documentation are available through Intel ODM partners.

FIMs include one or all of the following subsystems

- Platform Management

- Clocks/Resets

- HPS Subsystem

- PCIe Subsystem

- Memory Subsystem

- Transceiver Subsystem

#### **FIM Configurations Provided**

| Configurations                             | N6000 FIMS                       |         |                  |             | N6001 FIMs  |         |

|--------------------------------------------|----------------------------------|---------|------------------|-------------|-------------|---------|

| Hard Processor (HPS)<br>Subsystem          | No 1588 PTP                      |         | 1588 PTP Enabled |             | No 1588 PTP |         |

| Transceiver Subsystem                      | 2x4x10G                          | 2x2x25G | 2x1x100G         | 2x4x10G     | 2x2x25G     | 2x4x25G |

| PCIe Subsystem                             | 4.0 x8                           |         |                  |             | 4.0 x16     |         |

| Memory Subsystem                           | <ul> <li>2 Channels x</li> </ul> |         |                  |             |             |         |

| SR-IOV Support                             | 5-PF, 3-VF[PF0]                  |         |                  |             |             |         |

| AXI ST Datapath                            | 512b@350MHz                      |         |                  | 512b@400MHz |             |         |

| Intel E810 Ethernet<br>Controller (100GbE) | Yes                              |         |                  |             | No          |         |

### Learn more at intel.com/n6000

## intel.

Performance varies by use, configuration and other factors. Learn more at www.intel.com/PerformanceIndex.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure.

$Your \, costs \, and \, results \, may \, vary.$

Intel technologies may require enabled hardware, software or service activation.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.