Reconstructing Power Efficiency

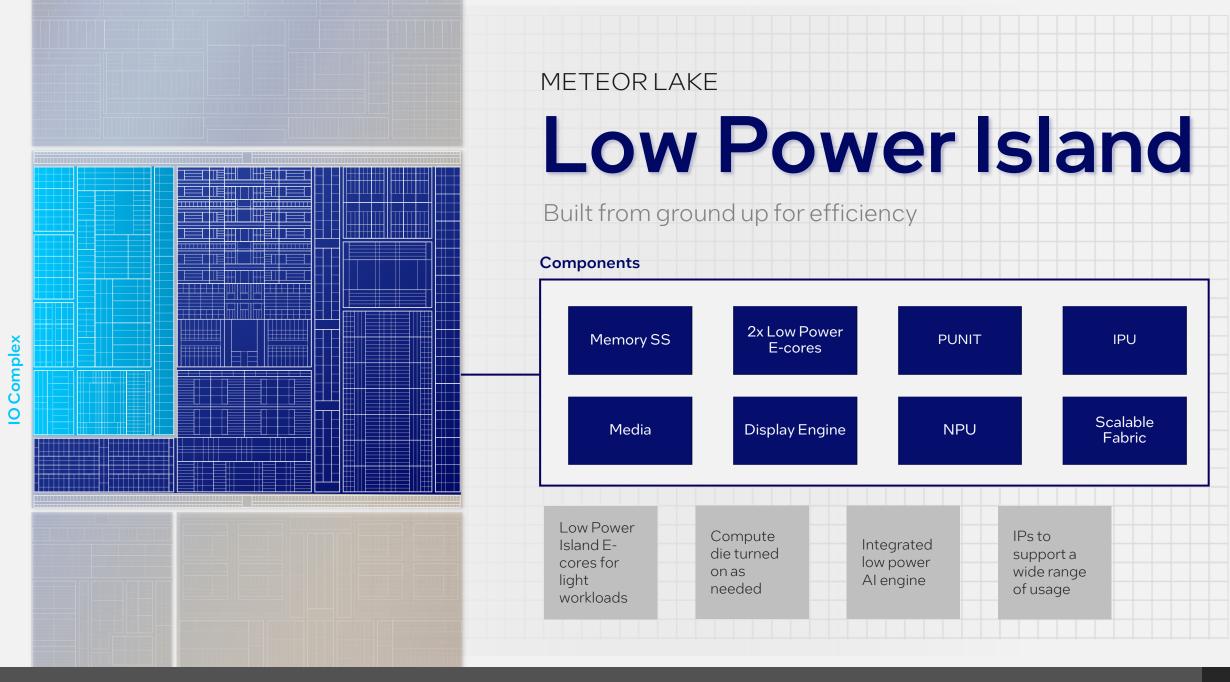

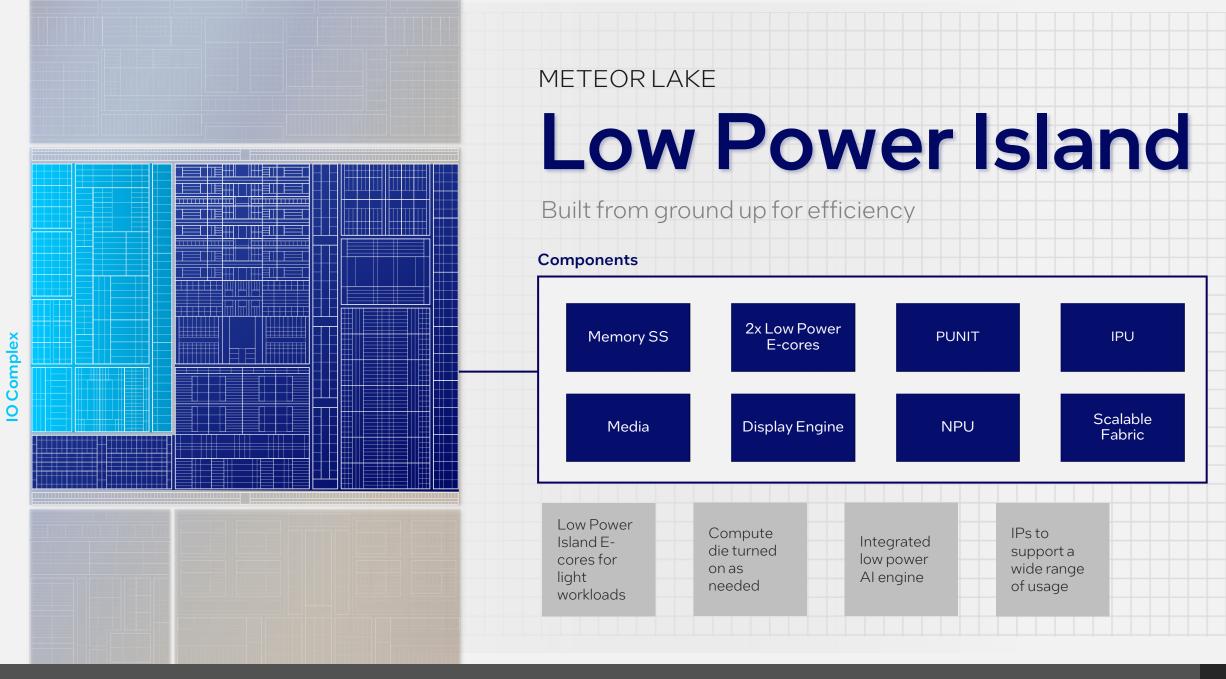

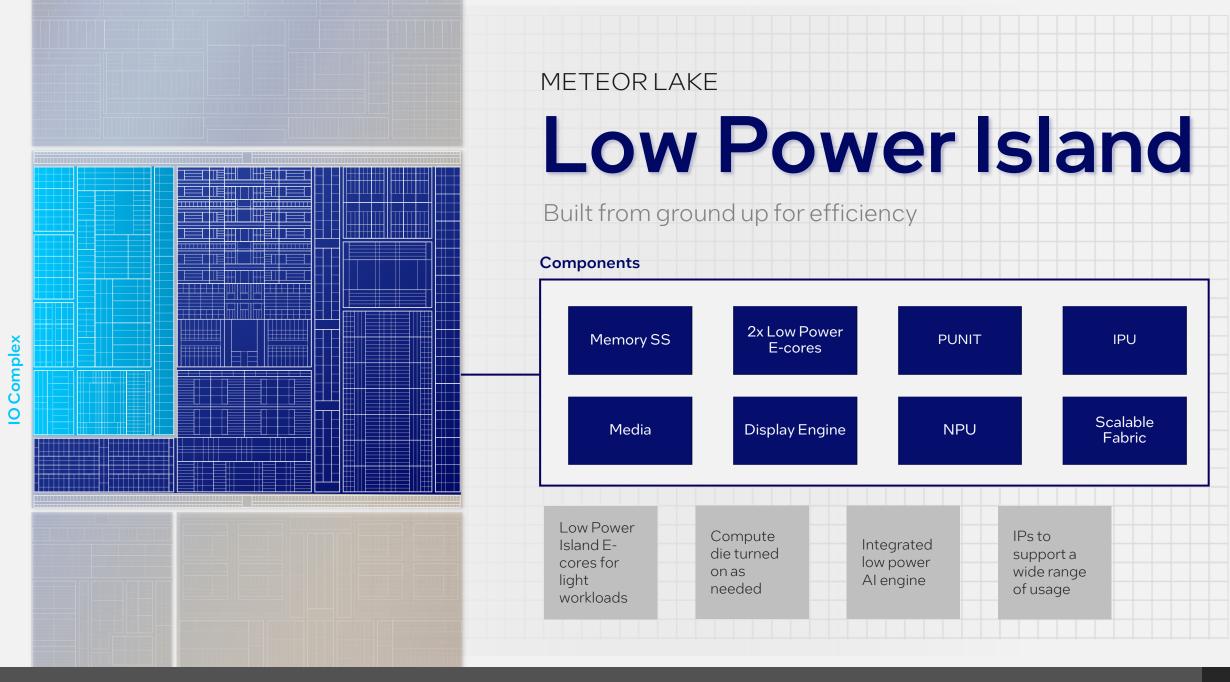

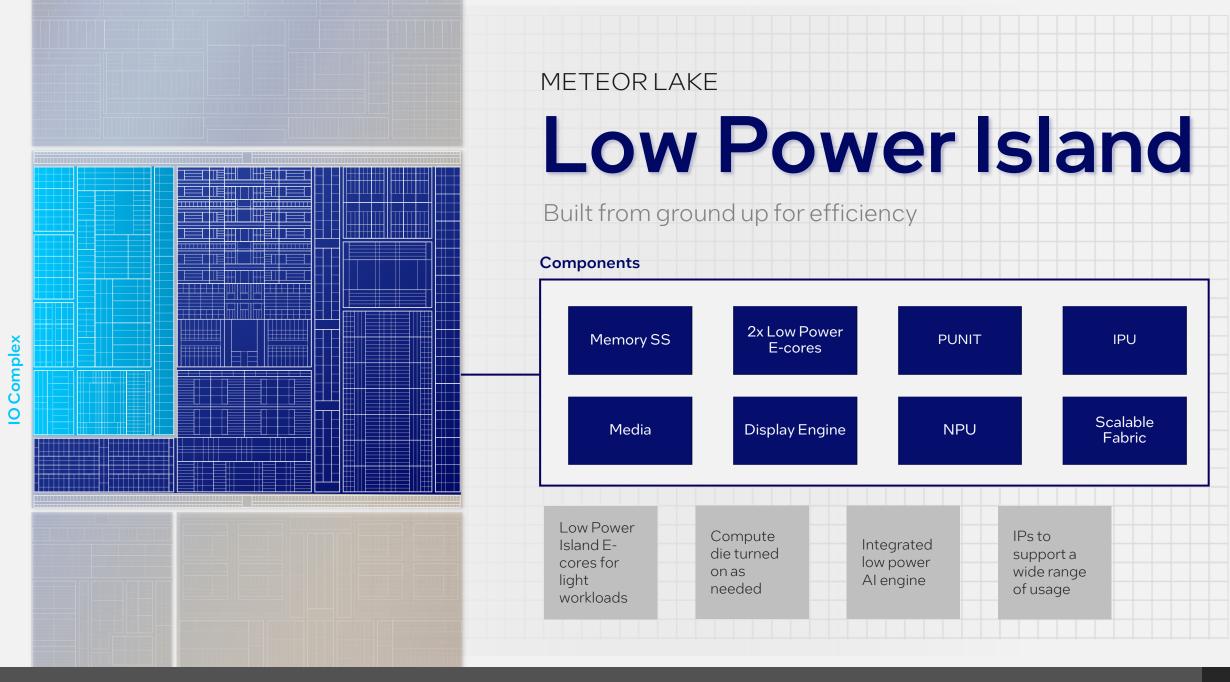

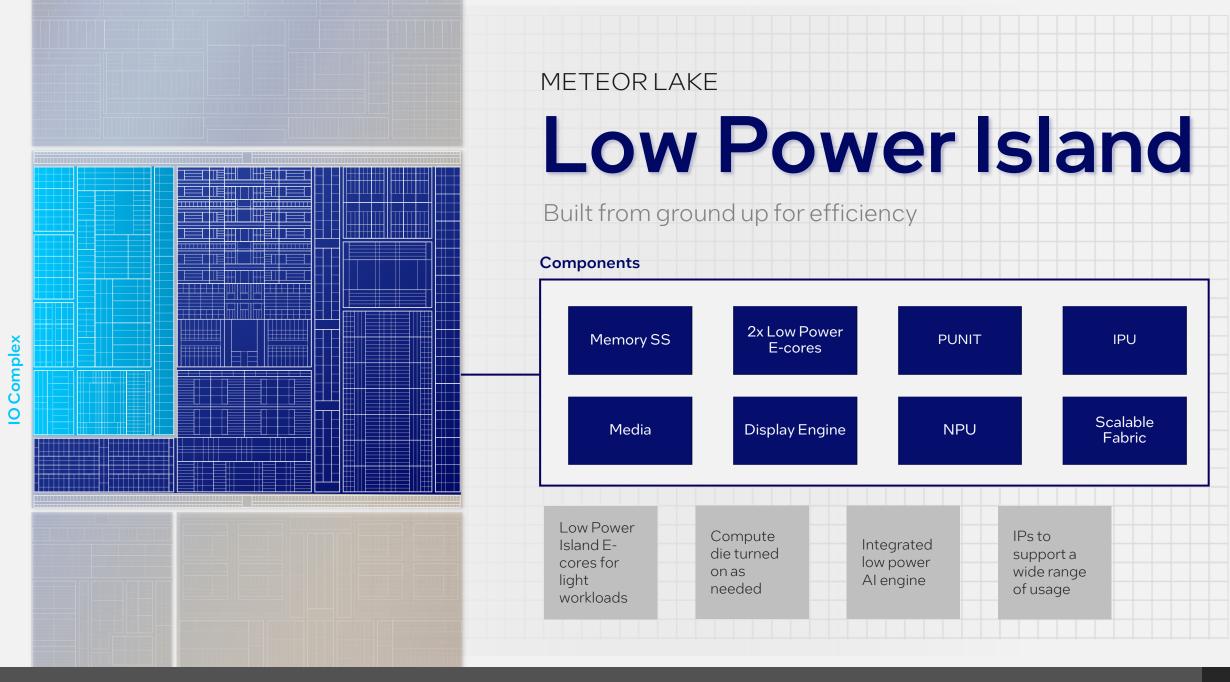

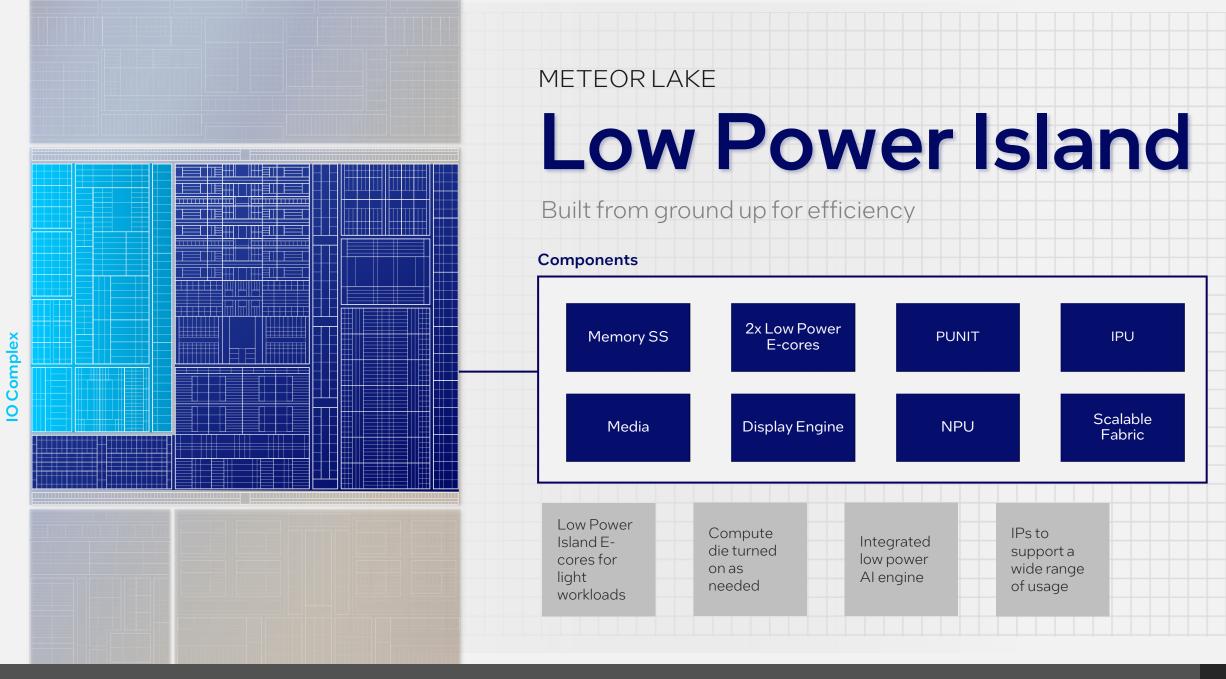

Low Power Island

Hybrid Architecture Vision

Primer on 3D Performance Hybrid Architecture

Unpacking Intel® Thread Director

OS Optimizations

Rest of SoC and Platform Technologies

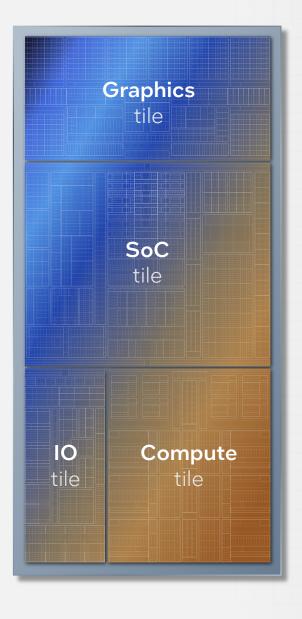

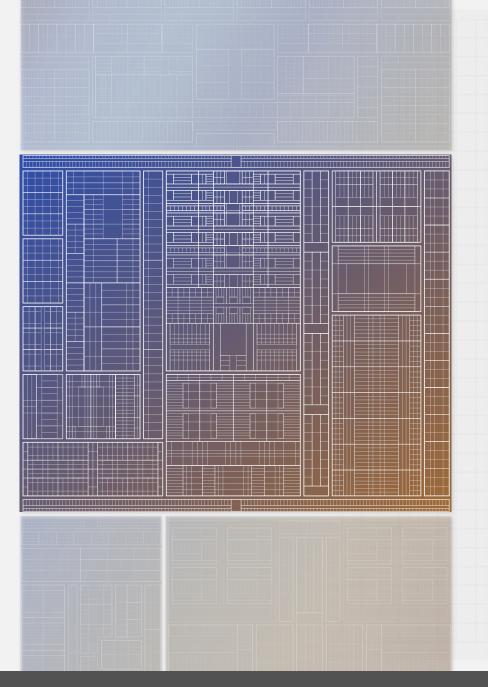

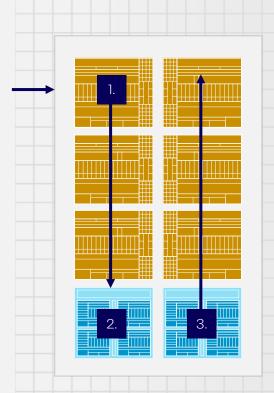

#### Tile Architecture

IPs matched to process for performance and energy efficiency

**Graphics tile** - optimized for 3D performance

**SoC tile -** optimized for power

**Compute tile** – optimized for CPU performance

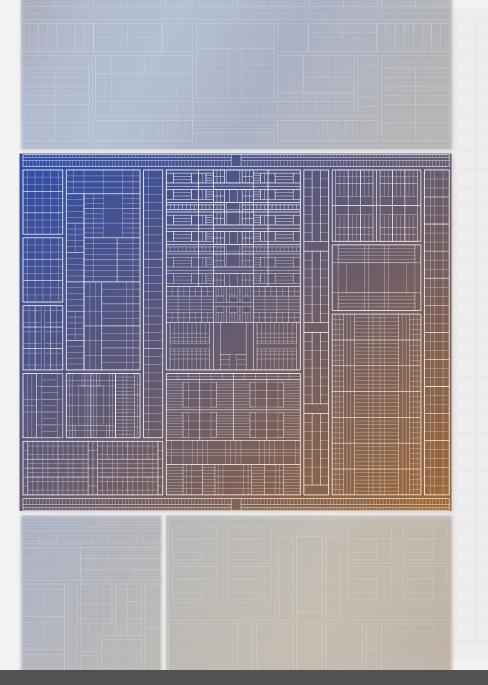

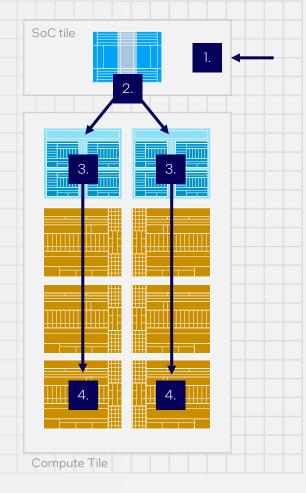

#### Tile Architecture

IPs matched to process for performance and energy efficiency

**Graphics tile** - optimized for 3D performance

**SoC tile -** optimized for power

**Compute tile** – optimized for CPU performance

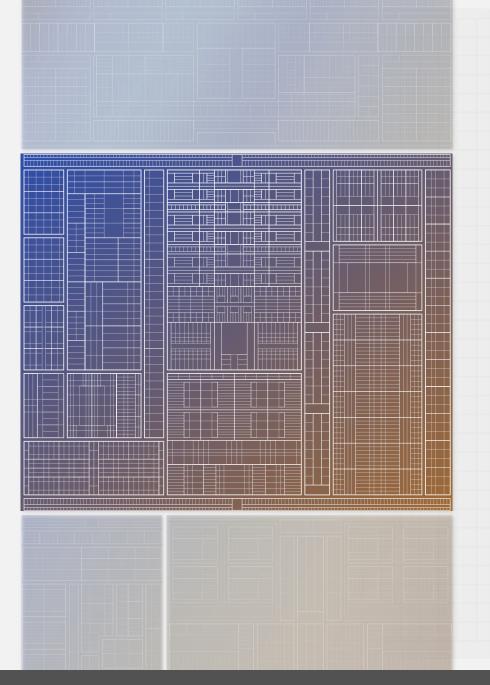

#### Tile Architecture

IPs matched to process for performance and energy efficiency

**Graphics tile** - optimized for 3D performance

**SoC tile -** optimized for power

**Compute tile** – optimized for CPU performance

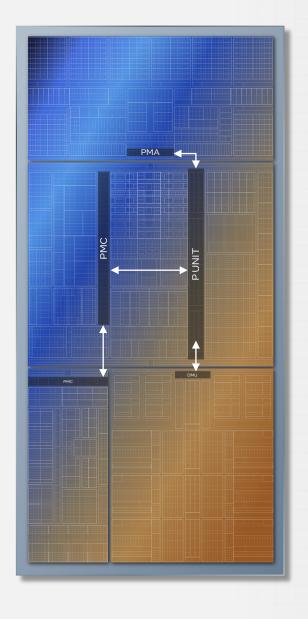

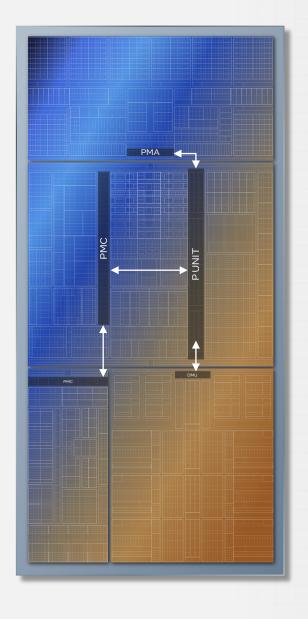

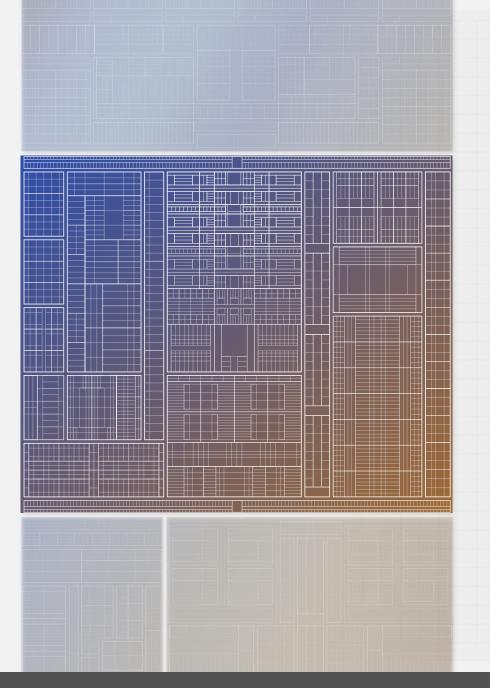

#### Power Efficiency

New foundations for energy efficiency

Grounds up **modular and scalable PM** architecture for disaggregation

New **scalable fabric** for improved bandwidth and energy efficiency

Coordination between multiple PM controllers on different tiles

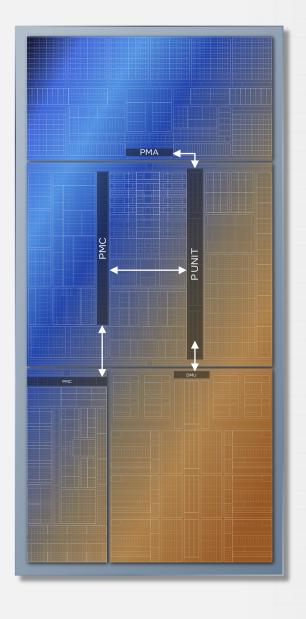

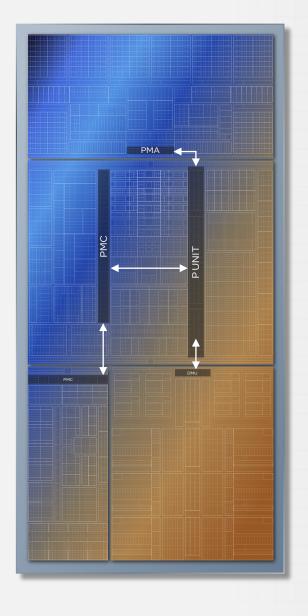

#### Power Efficiency

New foundations for energy efficiency

Grounds up **modular and scalable PM** architecture for disaggregation

New **scalable fabric** for improved bandwidth and energy efficiency

Coordination between multiple PM controllers on different tiles

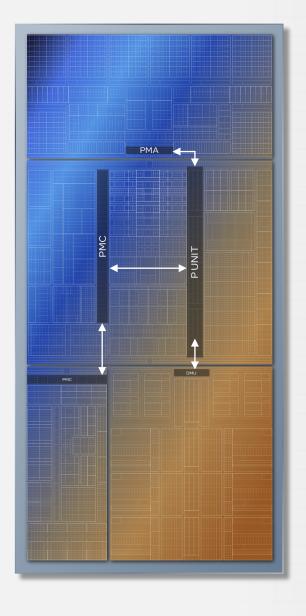

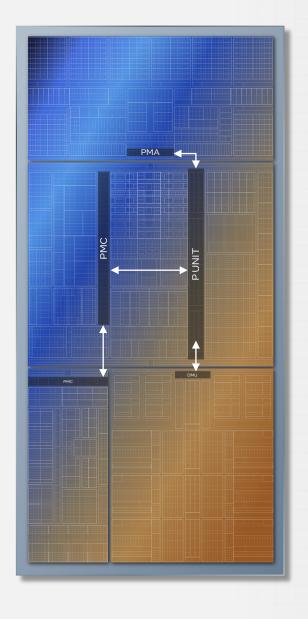

#### Power Efficiency

New foundations for energy efficiency

Grounds up **modular and scalable PM** architecture for disaggregation

New **scalable fabric** for improved bandwidth and energy efficiency

Coordination between multiple PM controllers on different tiles

#### Power Efficiency

New foundations for energy efficiency

Grounds up **modular and scalable PM** architecture for disaggregation

New **scalable fabric** for improved bandwidth and energy efficiency

Coordination between multiple PM controllers on different tiles

#### Power Efficiency

New foundations for energy efficiency

Grounds up **modular and scalable PM** architecture for disaggregation

New **scalable fabric** for improved bandwidth and energy efficiency

Coordination between multiple PM controllers on different tiles

#### Power Efficiency

New foundations for energy efficiency

Grounds up **modular and scalable PM** architecture for disaggregation

New **scalable fabric** for improved bandwidth and energy efficiency

Coordination between multiple PM controllers on different tiles

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

## Power Efficiency Features

Integrated DLVRs

for fine grained voltage control

Dynamic

Fabric

Frequency

Bandwidth and

QoS based

SoC algorithms shaped by Internal WL type inference

Reconstructing Power Efficiency

Low Power Island

#### **Hybrid Architecture Vision**

Primer on 3D Performance Hybrid Architecture

Unpacking Intel Thread Director

OS Optimizations

Platform Technologies

## 3D Performance Hybrid Architecture Vision

Optimize power efficiency while delivering best adaptive performance

#### **Intel Thread Director**

hardware that provides feedback to OS for optimal scheduling decisions

#### Symmetric ISA

exposed to OS as individual logical processors with capabilities enumerated

#### Optimized OS scheduler

unlocks great performance benefits

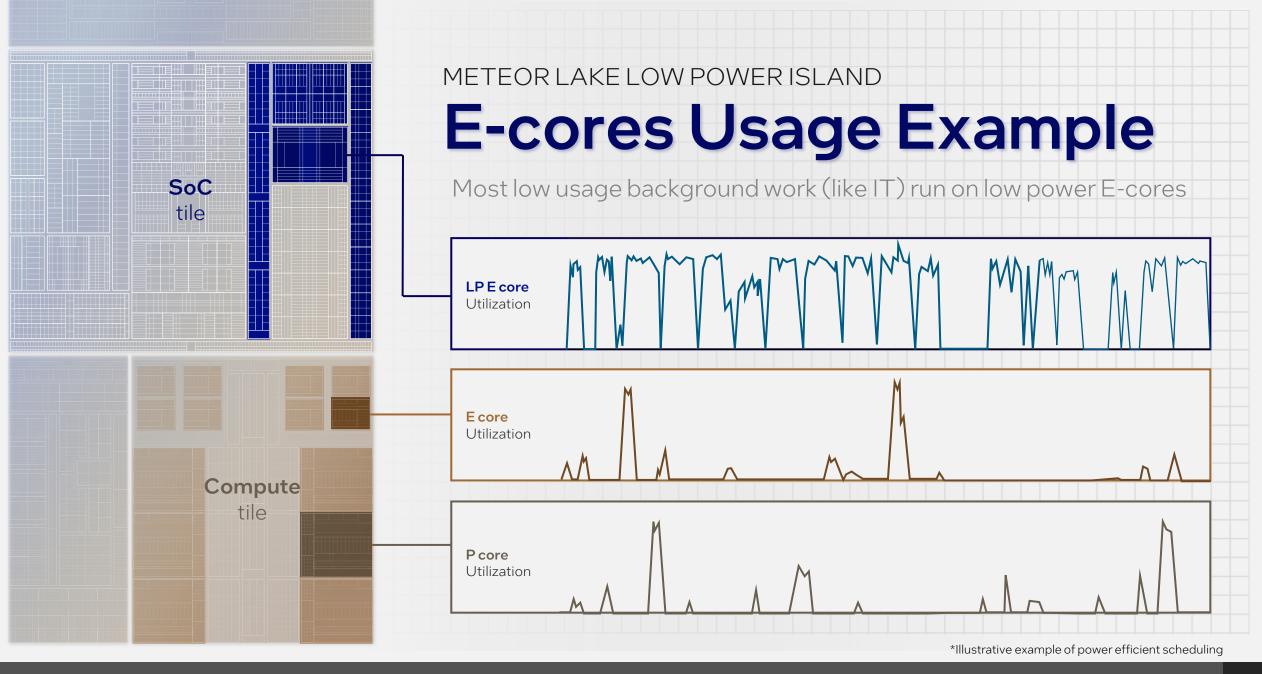

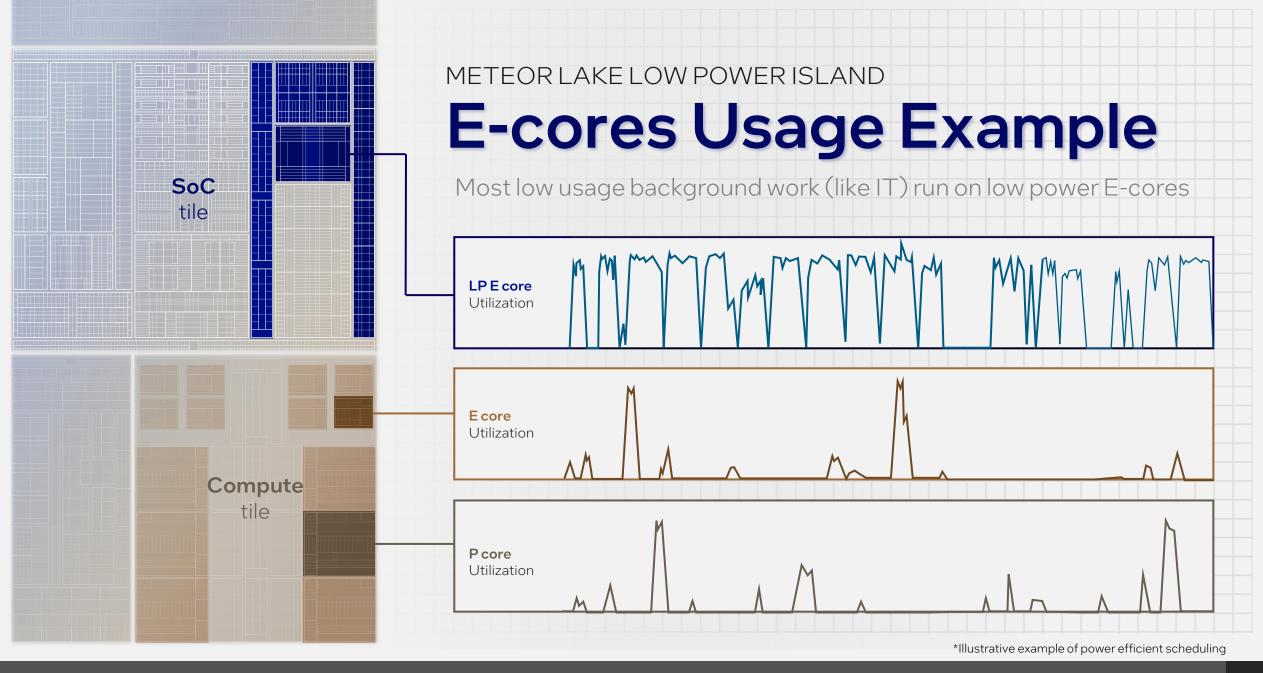

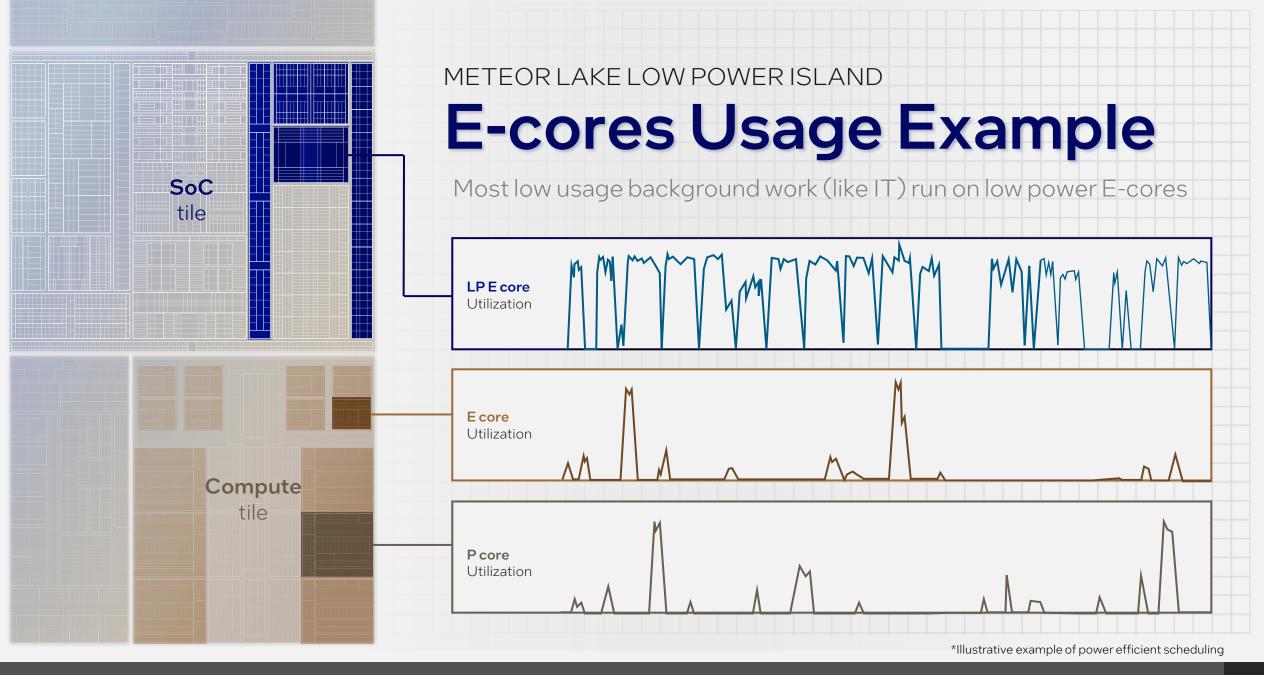

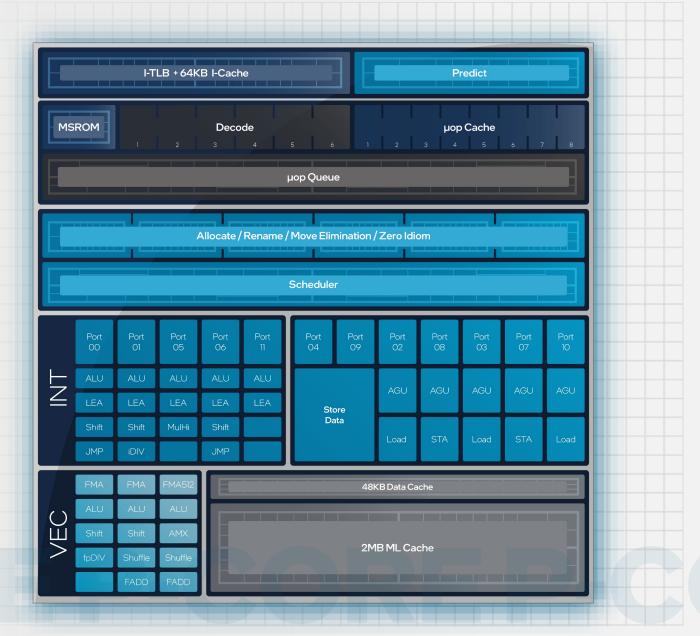

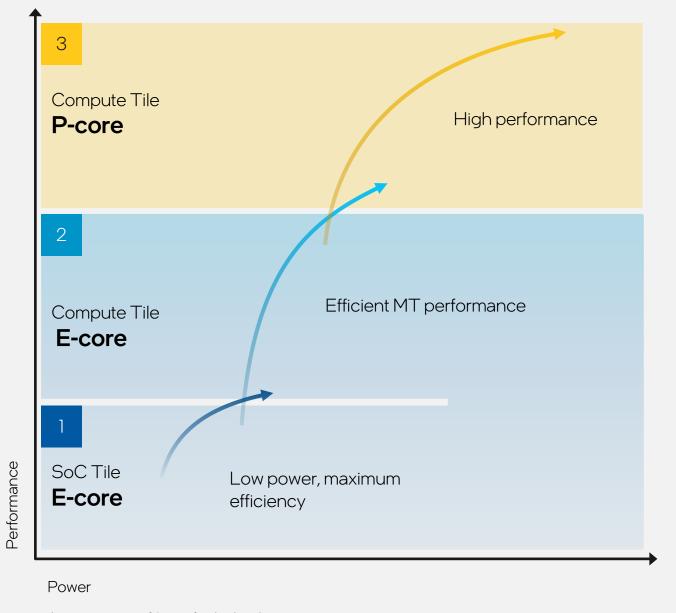

#### Compute tile P-cores

heavy lifting power for **single** & limited threading perf

Compute tile E-cores provide efficient MT throughput

SoC tile E-cores provide low power and energy efficiency

Primer on 3D Performance Hybrid Architecture Agenda

3D

# Performance Hybrid Architecture

A New Foundation for PC Performance, Efficiency & Battery Life E-core

Crestmont

Low Power

Crestmont

E-core

P-core

Redwood Cove

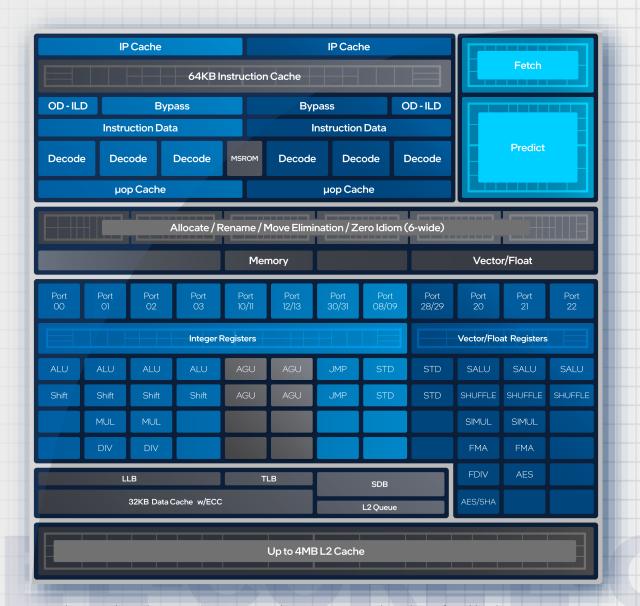

#### **REDWOOD COVE**

#### **New P-core**

Targeted for efficient performance

Improved performance efficiency\*

Increased BW per core package\*

Improved

Performance

Monitoring Unit

Improved feedback Intel Thread Director

${}^* Architectural \ simulation \ vs. \ Golden \ Cove \ architecture. \ Results \ may \ vary \ across \ workloads.$

CRESTMONT

#### **New E-core**

Significant improvements over prior E-core

IPC gains over prior Ecores\* AI acceleration VNNI, ISA improvements\*

Enhanced branch prediction

Enhanced Feedback Intel Thread Director

<sup>\*</sup>Architectural simulation vs. Gracemont architecture across a broad set of workloads. VNNI improvements based on doubling the number of VNNI ports. Results may vary.

$^* Conceptual \, representation \, of \, 3D \, Perf \, Hybrid \, Arch$

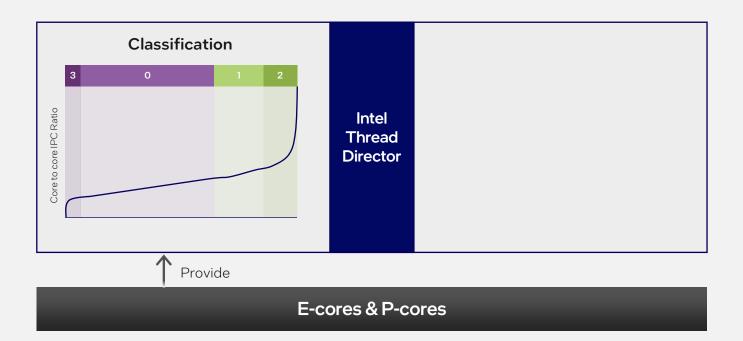

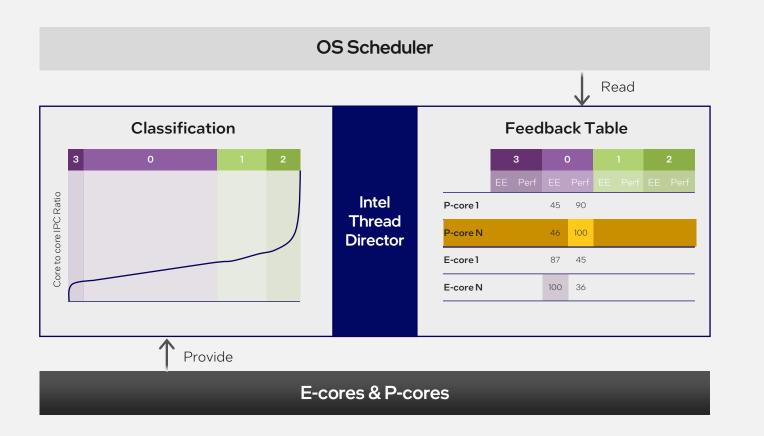

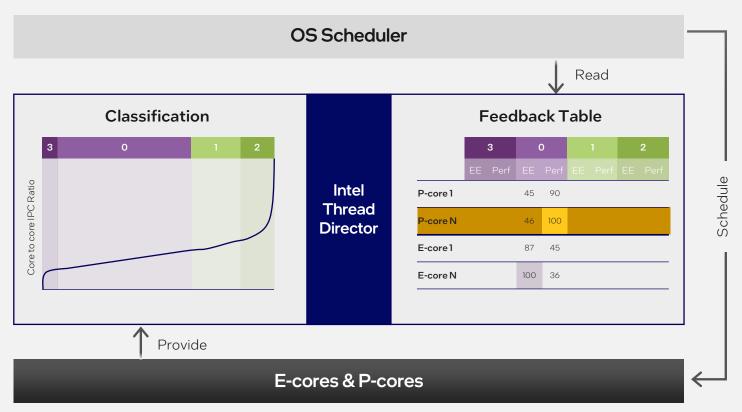

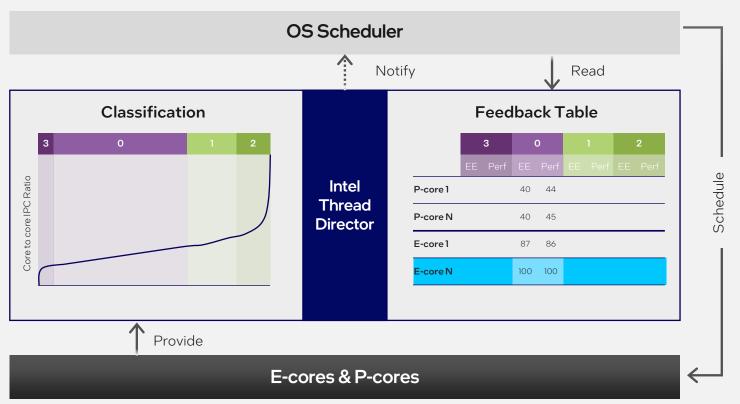

INTEL THREAD DIRECTOR

## Architecture

**OS Scheduler**

**Intel Thread Director**

E-cores & P-cores

#### **OS Scheduler**

#### INTEL THREAD DIRECTOR

## Scheduling Improvements

#### Raptor Lake

- 1. Higher QoS work moves to P-cores

- 2. Lower QoS work moves to **E-cores**

- 3. Periodically move **E-core** threads to **P-core** to reclassify and move if necessary

#### **Meteor Lake**

- 1. Try to contain on SoC E-cores

- 2. When work cannot be contained move to compute tile

- 3. Use compute tile **E-cores** if the work fits there

- 4. Higher demand work to **P-cores** that can benefit from those

#### Incorporation SoC tile

(low power domain) feedback from Intel Thread Director

## Processor power management optimizations

for battery life in DC and perf in AC

Maximizing power and performance for SoC and compute tile activities

METEOR LAKE

## Scheduling Example Perfor

Performance

Low Utilization app (2 Threads on LP E-cores)

New High Utilization app (4 Threads on P-cores)

HW updates Intel Thread Director, TD notifies OS

Removal of hard affinity in software

Leverage power throttling (QoS) APIs Optimized spinwait via updated threading libraries

Integration of optimized SDKs & frameworks in ISV apps

Detect hybrid architecture through MS API

AVX-VNNI and new ISA feature

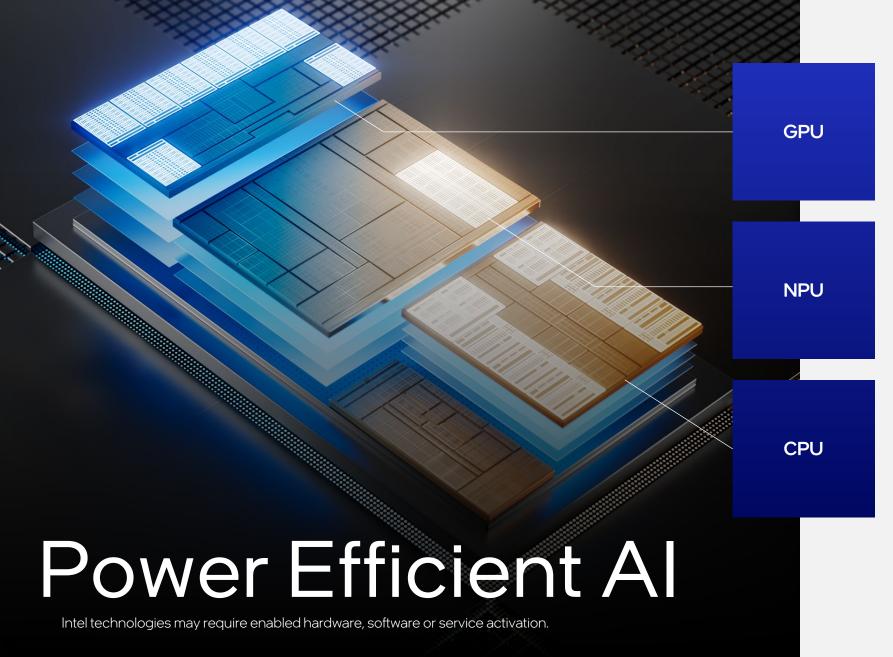

#### Performance Parallelism & Throughput

Ideal for AI infused in Media/3D/render pipeline

#### Dedicated Low Power Al Engine

Designed for performance and power efficiency Ideal for sustained Al and Al offload

#### **Fast Response**

Ideal for light-weight, single inference low-latency Al tasks

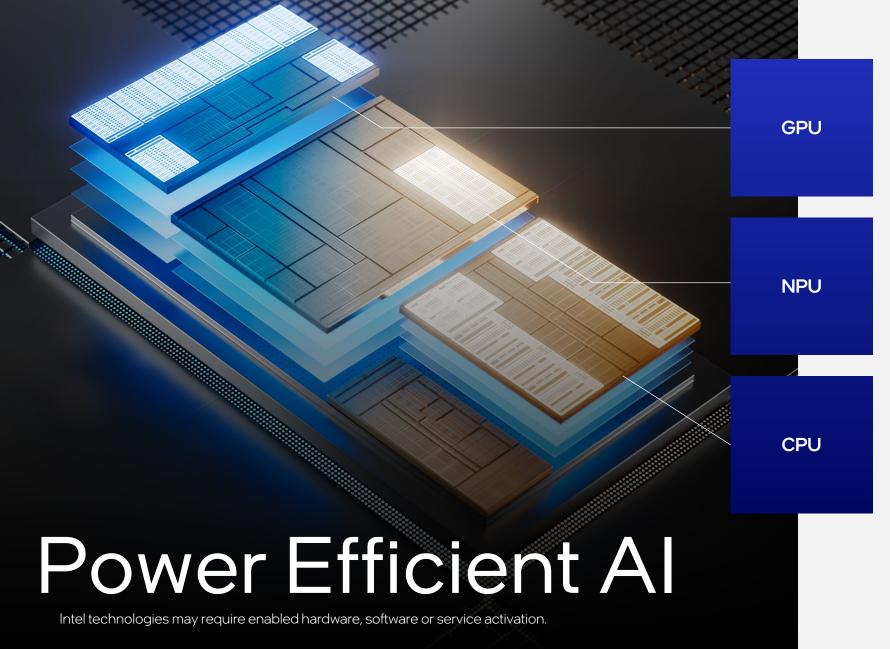

#### Performance Parallelism & Throughput

Ideal for AI infused in Media/3D/render pipeline

#### Dedicated Low Power Al Engine

Designed for performance and power efficiency Ideal for sustained Al and Al offload

#### **Fast Response**

Ideal for light-weight, single inference low-latency Al tasks

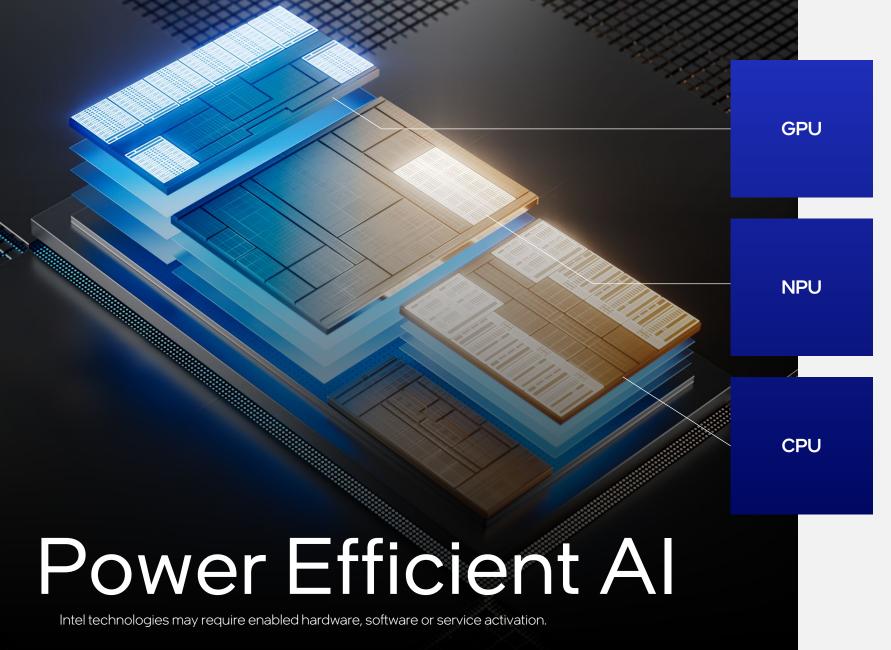

#### Performance Parallelism & Throughput

Ideal for AI infused in Media/3D/render pipeline

#### Dedicated Low Power Al Engine

Designed for performance and power efficiency Ideal for sustained Al and Al offload

#### **Fast Response**

Ideal for light-weight, single inference low-latency AI tasks

INTEL

## Intelligent Display

Combining ecosystem display panel innovation with Intel software to enable

- battery life boost

- enhanced visual experience

- sustainability benefits

#### **Autonomous Low** Refresh Rate

Display panel dynamically changes refresh rate based on rendered content

#### **User Based** Refresh Rate

Display panel adjusts backlight and refresh rate based on user status and engagement

#### **Dynamic Visual Enhancements**

Display panel dynamically adjusts contrast and brightness based on content

\*Some Intel Intelligent Display features may require additional panel enhancements.

INTEL

## Intelligent Display

Combining ecosystem display panel innovation with Intel software to enable

- battery life boost

- enhanced visual experience

- sustainability benefits

#### **Autonomous Low** Refresh Rate

Display panel dynamically changes refresh rate based on rendered content

#### **User Based** Refresh Rate

Display panel adjusts backlight and refresh rate based on user status and engagement

#### **Dynamic Visual Enhancements**

Display panel dynamically adjusts contrast and brightness based on content

\*Some Intel Intelligent Display features may require additional panel enhancements.

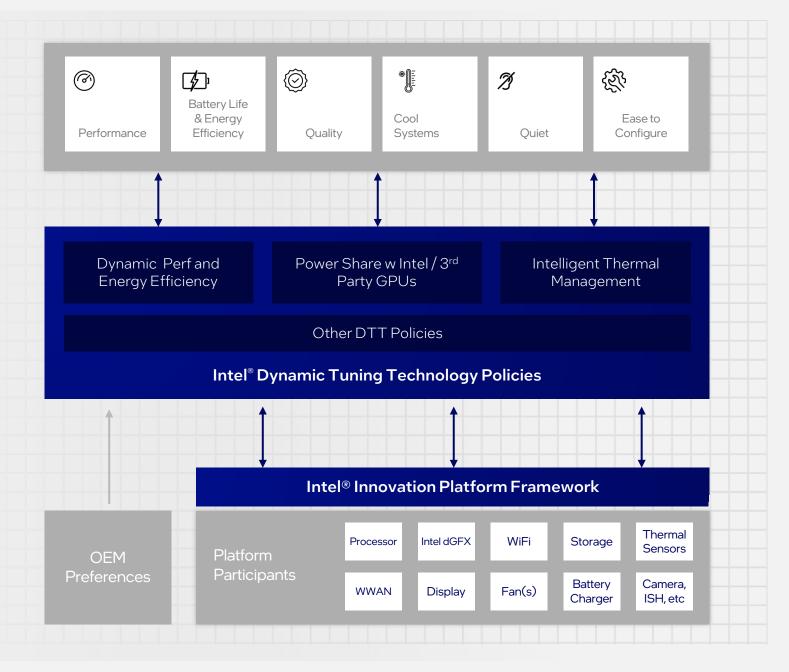

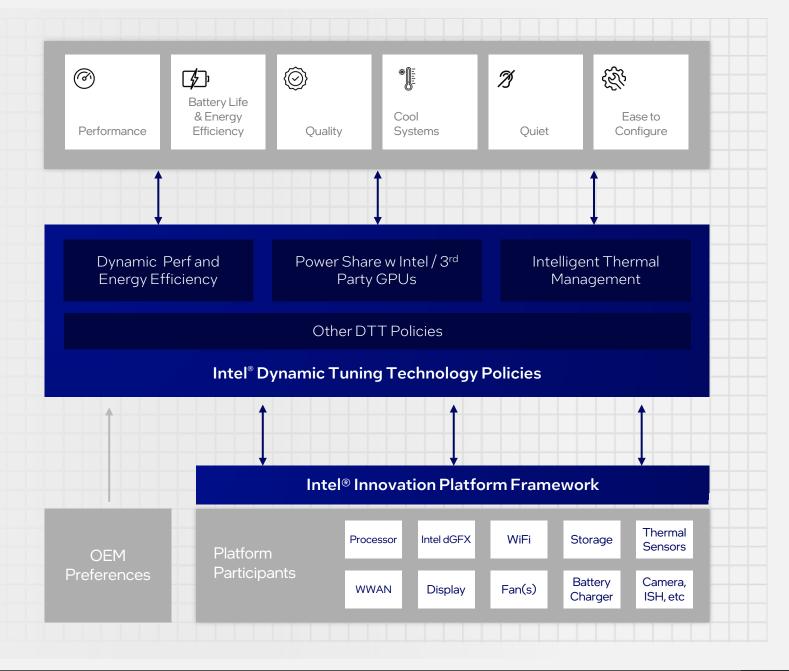

# Intel® Dynamic Tuning Technology Software

# Intel® Dynamic Tuning Technology Software

## Advancing Moore's Law 5 NODES IN 4 YEARS

In High Volume Manufacturing **Today**

Ramping Production **Today**

Manufacturing Ready **H2 2023**

Manufacturing Ready H1 2024

Manufacturing Ready H2 2024

## Advancing Moore's Law 5 NODES IN 4 YEARS

In High Volume Manufacturing **Today**

Ramping Production **Today**

Manufacturing Ready **H2 2023**

Manufacturing Ready H12024

Manufacturing Ready H2 2024

## Advancing Moore's Law 5 NODES IN 4 YEARS

In High Volume Manufacturing **Today**

Ramping Production **Today**

Manufacturing Ready **H2 2023**

Manufacturing Ready H12024

Manufacturing Ready H2 2024

## Power Effici Our most power-efficient Rest of SoC and Low Platform Reconstructing **Power**

Island

**Technologies**

**Power Efficiency**

#### Intel Thread Director

Right thread on the right core at the right time

Runtime Instruction

Mix Monitoring

nanosecond

precision

Runtime Feedback to OS for optimal scheduling

Dynamic intelligent guidance without user input

#### 3D Performance Hybrid

Right cores for the right work

For high-Performance

**NEW** E-cores

Efficient MT performance

SoC TILE E-cores

Low power, maximum efficiency

## Power Effici Our most power-efficient Rest of SoC and Low Platform Reconstructing **Power**

Island

**Technologies**

**Power Efficiency**

#### Intel Thread Director

Right thread on the right core at the right time

Runtime Instruction

Mix Monitoring

nanosecond

precision

Runtime Feedback to OS for optimal scheduling

Dynamic intelligent guidance without user input

#### 3D Performance Hybrid

Right cores for the right work

For high-Performance

**NEW** E-cores

Efficient MT performance

SoC TILE E-cores

Low power, maximum efficiency

## Power Effici Our most power-efficient Rest of SoC and Low Platform Reconstructing **Power**

Island

**Technologies**

**Power Efficiency**

#### Intel Thread Director

Right thread on the right core at the right time

Runtime Instruction

Mix Monitoring

nanosecond

precision

Runtime Feedback to OS for optimal scheduling

Dynamic intelligent guidance without user input

#### 3D Performance Hybrid

Right cores for the right work

For high-Performance

**NEW** E-cores

Efficient MT performance

SoC TILE E-cores

Low power, maximum efficiency

#### Notices and Disclaimers

Performance varies by use, configuration and other factors. Learn more at <a href="www.intel.com/PerformanceIndex">www.intel.com/PerformanceIndex</a>.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details.

Results that are based on pre-production systems and components as well as results that have been estimated or simulated using an Intel Reference Platform (an internal example new system), internal Intel analysis or architecture simulation or modeling are provided to you for informational purposes only. Results may vary based on future changes to any systems, components, specifications or configurations.

All product and service plans, and roadmaps are subject to change without notice. Any forecasts of products, services or technologies needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Code names are often used by Intel to identify products, services or technologies that are in development and usage may change over time. Product, service and technology performance varies by use, configuration and other factors. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Learn more at <a href="https://www.intel.com/PerformanceIndex">www.intel.com/PerformanceIndex</a> and <a href="https://www.intel.com/ProcessInnovation">www.intel.com/ProcessInnovation</a>.

Reference to research results, including comparisons to products, services or technology performance are estimates and do not imply availability. The products and services described may contain defects or errors which may cause deviation from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and annual report on form 10-K and other SEC filings at <a href="https://www.intc.com">www.intc.com</a>.

Intel contributes to the development of benchmarks by participating in, sponsoring, and/or contributing technical support to various benchmarking groups, including the BenchmarkXPRT Development Community administered by Principled Technologies.

Altering clock frequency or voltage may void any product warranties and reduce stability, security, performance, and life of the processor and other components. Check with system and component manufacturers for details.

Intel is committed to the continued development of more sustainable products, software, and processes and working with suppliers and customers as we strive to lower the greenhouse gas footprint of our entire value chain. Where applicable, environmental attributes of a product family or specific SKU will be stated with specificity. Refer to the 2022 Corporate Responsibility Report for further information.

Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

Your costs and results may vary. No product or component can be absolutely secure. Intel technologies may require enabled hardware, software or service activation.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

##