# Intel<sup>®</sup> Resource Director Technology (Intel<sup>®</sup> RDT) Architecture Specification

September 2023

**Revision 1.0**

Document Number: 356688-001US

# Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

Intel is a sponsor and member of the Benchmark XPRT Development Community and was the major developer of the XPRT family of benchmarks. Principled Technologies is the publisher of the XPRT family of benchmarks. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting <a href="https://www.intel.com/design/literature.htm">www.intel.com/design/literature.htm</a>.

Intel, the Intel logo, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others

Copyright  $\ensuremath{\text{@}}$  2023, Intel Corporation. All Rights Reserved.

# **Contents**

| 1 | Intro | oduction                                             | 10 |

|---|-------|------------------------------------------------------|----|

|   | 1.1   | High Level Usage Models                              | 10 |

|   | 1.2   | Scope                                                | 11 |

|   | 1.3   | Audience                                             | 12 |

|   | 1.4   | References                                           | 12 |

| 2 | Intel | l® Resource Director Technology Overview             | 13 |

|   | 2.1   | Common Tags                                          |    |

|   | 2.2   | L3 Configurations                                    | 13 |

|   | 2.3   | Intel® RDT Monitoring Technologies                   |    |

|   |       | 2.3.1 Intel® RDT Monitoring Key Ingredients          |    |

|   |       | 2.3.2 Shared-L3 versus Multiple-L3 Configuration     |    |

|   | 2.4   | Intel® RDT Allocation Technologies                   |    |

|   |       | 2.4.1 Intel® RDT Allocation Key Ingredients          |    |

|   |       | 2.4.2 Shared-L3 versus Multiple-L3 Configuration     |    |

| 3 | Inte  | l® Resource Director Technology for CPU Agents       |    |

|   | 3.1   | Intel® RDT Monitoring Features                       |    |

|   |       | 3.1.1 Common Framework                               |    |

|   |       | 3.1.2 Cache Occupancy Monitoring Technology          |    |

|   | 2.2   | 3.1.3 Memory Bandwidth Monitoring                    |    |

|   | 3.2   | Intel® RDT Allocation Features                       |    |

|   |       | 3.2.1 Common Framework                               |    |

|   |       | 3.2.3 Memory Bandwidth Allocation                    |    |

|   |       | 3.2.4 Cache Bandwidth Allocation                     |    |

| 4 | Inte  | l® Resource Director Technology for Non-CPU Agents   | 36 |

|   | 4.1   | Introduction                                         |    |

|   | 4.2   | Features                                             |    |

|   | 4.3   | Enumeration                                          |    |

|   | 4.4   | Interface                                            | 38 |

|   | 4.5   | Common Tags                                          | 40 |

|   | 4.6   | I/O Blocks and Channels                              | 40 |

|   | 4.7   | I/O Block Configuration                              |    |

|   | 4.8   | Shared-L3 Configuration                              |    |

|   |       | 4.8.1 Software Flow                                  |    |

|   |       | 4.8.2 Monitoring: Data Flows for RMIDs               |    |

|   | 4.0   | 4.8.3 Allocation: CLOS-based Control Interfaces      |    |

|   | 4.9   | CXL-Specific Considerations                          |    |

|   |       | 4.9.2 Integrated Accelerators                        |    |

|   | 4.10  | Use Cases                                            |    |

| _ |       |                                                      |    |

| 5 |       | S Considerations                                     |    |

|   | 5.1   | Architectural Intel® RDT Features for Non-CPU Agents |    |

|   |       | 5.1.1 RMID/CLOS tagging - ACPI Enumeration           | 50 |

# intel

|                | 5.2        | Model-Specific Intel® RDT Features for CPU Agents                                                                     |    |

|----------------|------------|-----------------------------------------------------------------------------------------------------------------------|----|

|                |            | 5.2.1 BIOS knobs for Resource Aware MBA                                                                               |    |

| 6              |            | Register Descriptions                                                                                                 |    |

|                | 6.1        | Non-CPU Agent Intel® RDT Register Location                                                                            |    |

|                |            | 6.1.1 Software Access to Registers                                                                                    |    |

| _              | _          |                                                                                                                       |    |

| 7              |            | ramming Guidelines                                                                                                    |    |

|                | 7.1        | Intel <sup>®</sup> RDT Monitoring Software Flows for CPU Agents                                                       |    |

|                |            | 7.1.1 Intel® RDT Monitoring Software Flows for CPO Agents                                                             |    |

|                |            | 7.1.3 Virtualization Scenarios                                                                                        |    |

|                | 7.2        | Intel® RDT Allocation Software Flows for CPU Agents                                                                   |    |

|                |            | 7.2.1 Intel® RDT Software Allocation Flows for CPU Agents                                                             |    |

|                | 7.3        | Intel® RDT Software Flows for Non-CPU Agents                                                                          | 72 |

| A              | Intel®     | <sup>®</sup> RDT Feature Details                                                                                      | 74 |

|                | A.1        | Intel® RDT Feature Evolution                                                                                          |    |

|                | A.2        | Intel® RDT Architectural Features and Supported Products                                                              |    |

|                | A.3<br>A.4 | Intel® RDT Model-Specific Features and Supported Products Feature Mapping: CPU Agents, Non-CPU Agents in Different L3 | /8 |

|                | A.4        | Configurations                                                                                                        | 79 |

|                | A.5        | Architectural MSRs used with Intel® RDT Features                                                                      |    |

|                | A.6        | Model-Specific Registers for Intel® RDT Model Specific Features                                                       | 80 |

| В              | Mode       | el-Specific Intel® RDT Features                                                                                       | 81 |

|                | B.1        | Model-Specific Intel® RDT Features for CPU Agents                                                                     | 81 |

|                |            | B.1.1 Resource Aware MBA                                                                                              | 81 |

|                |            | B.1.2 Intel® RDT and Sub-NUMA Clustering Compatibility                                                                |    |

|                |            | B.1.3 STLB QoS B.1.4 L3 Cache Allocation Technology                                                                   |    |

|                |            | 2111 LS edelic / mocdelon recimology                                                                                  | 55 |

| <b>Figures</b> |            |                                                                                                                       |    |

|                |            |                                                                                                                       |    |

|                |            | e 2-1. Shared-L3 Configuration System Model and Presence of Intel® RDT Features                                       |    |

|                |            | e 2-2. Multiple-L3 Configuration System Model and Presence of Intel                                                   |    |

|                |            | RDT Features                                                                                                          |    |

|                | Figure     | e 2-3. Intel® RDT Monitoring – Enabling RMID-Based Monitoring for                                                     |    |

|                | Figuro     | Shared Resources<br>2-4. Intel® RDT Allocation – Enabling CLOS-based Allocation for Sh                                |    |

|                | rigure     | Resources                                                                                                             |    |

|                | Figure     | e 3-1. Resource Monitoring IDs (RMIDs) Assignment Flow                                                                |    |

|                | Figure     | e 3-2. IA32_PQR_ASSOC MSR to Set RMID                                                                                 | 20 |

|                |            | e 3-3. IA32_QM_EVTSEL and IA32_QM_CTR MSRs                                                                            |    |

|                |            | e 3-4. Classes of Service (CLOS) Association Flow                                                                     |    |

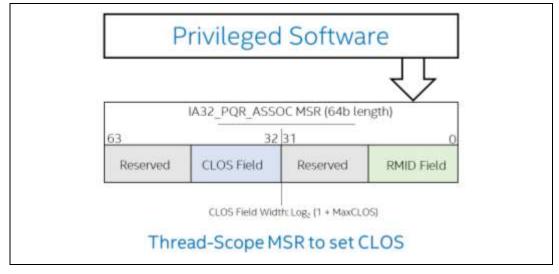

|                | _          | e 3-5. The IA32_PQR_ASSOC MSR to Set CLOS                                                                             |    |

|                | rigure     | $\geq$ 3-6. A High-Level Overview of the First-Generation MBA Feature $\ldots$                                        | Z/ |

|        | Figure 3-7. Second Generation MBA, Including a Fast-Responding Hardware                          |

|--------|--------------------------------------------------------------------------------------------------|

|        | Controller                                                                                       |

|        | Figure 3-8. Figure 3-9. Example of CBA Throttling between L2 and L3 caches                       |

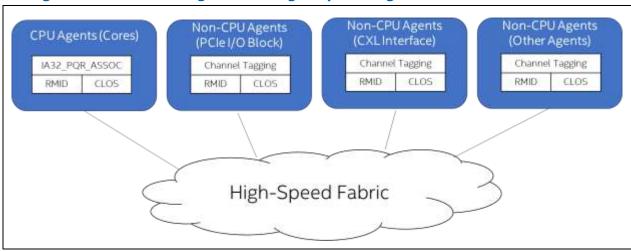

|        | Figure 4-1. Non-CPU Agent Building Atop CPU Agent Intel® RDT Features 36                         |

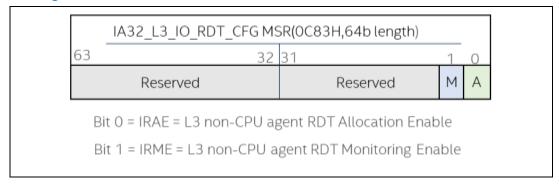

|        | Figure 4-2. The IA32_L3_IO_QOS_CFG MSR for Enabling Non-CPU Agent                                |

|        | Intel® RDT                                                                                       |

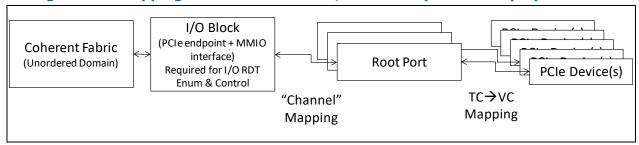

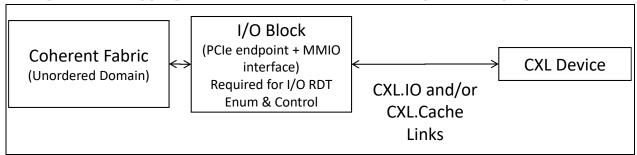

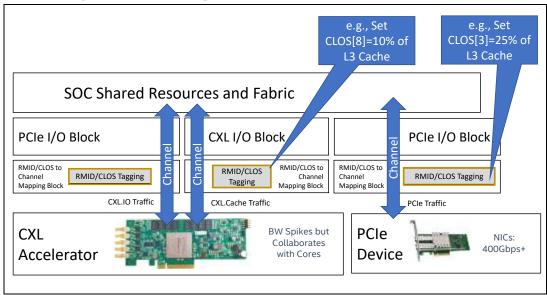

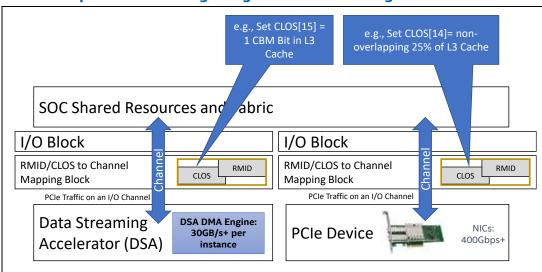

|        | Figure 4-3. Tagging for PCIe and CXL Devices40                                                   |

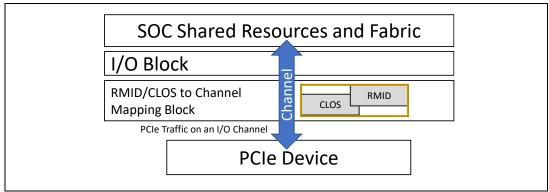

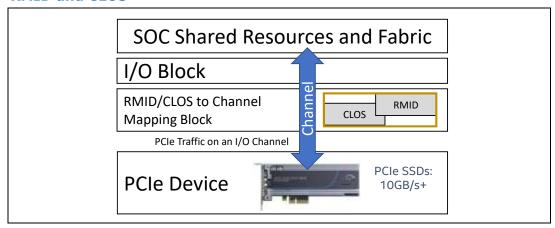

|        | Figure 4-4. Mapping of Channels in the I/O Domain (PCIe Example) 41                              |

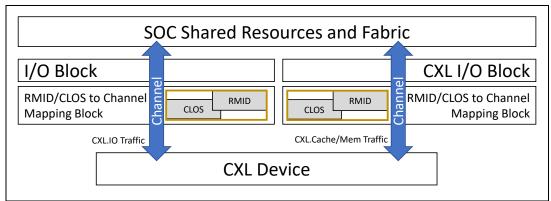

|        | Figure 4-5. Mapping of Channels in the I/O Domain (CXL Example) 41                               |

|        | Figure 4-6. Resource Monitoring and Control for PCIe and CXL Endpoints 42                        |

|        | Figure 4-7. Reuse of the IA32_L3_QOS_MASK_n MSRs for L3 CAT Control 45                           |

|        | Figure 4-8. Device Traffic Tagging Model with PCIe as the Sole Traffic Path . 46                 |

|        | Figure 4-9. PCIe Device Example, with Traffic on a Channel Tagged with an                        |

|        | RMID and CLOS                                                                                    |

|        | CXL.Cache Traffic Paths                                                                          |

|        | Figure 4-11. Example of Controlling Two Different PCIe Devices                                   |

|        | Figure 4-12. Example of Controlling a CXL Accelerator                                            |

|        | Figure 4-13. Example of Controlling a High-Bandwidth Integrated Accelerator                      |

|        | 48                                                                                               |

|        | Figure 4-14. MBA to Control a CXL.Mem Pooling Device                                             |

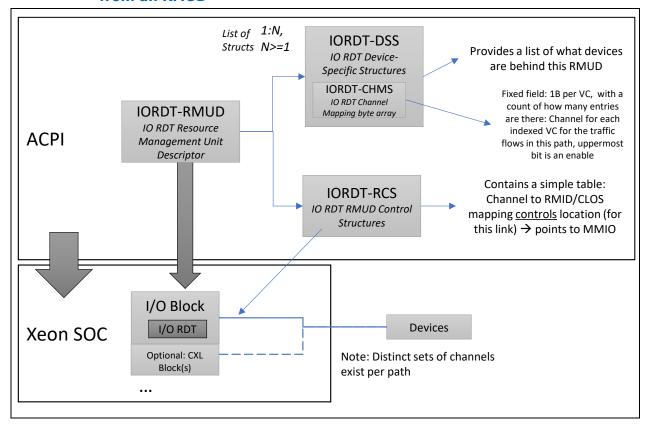

|        | Figure 5-1. Non-CPU Agent Intel® RDT ACPI Enumeration                                            |

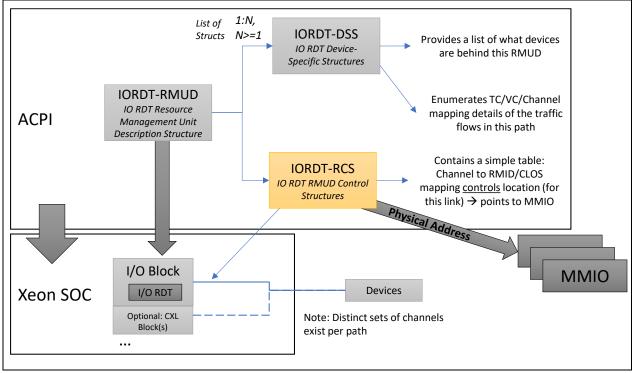

|        | Figure 5-2. ACPI Enumeration – Detail of DSS and RCS Structures                                  |

|        | Downstream from an RMUD52 Figure 5-3. Mapping from RCS Structures to MMIO Addresses for Per-link |

|        | Control                                                                                          |

|        | Figure 5-4. CXL Enumeration Example with CXL.IO and CXL.Cache Links 53                           |

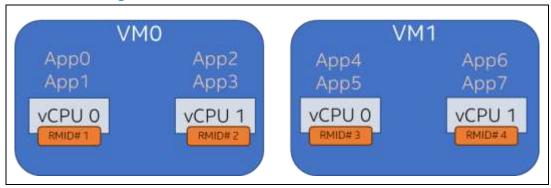

|        | Figure 7-1. RMIDs Assigned to vCPUs                                                              |

|        | Figure B-1. High-Level Overview of the Resource Aware MBA (MBA 4.0) 82                           |

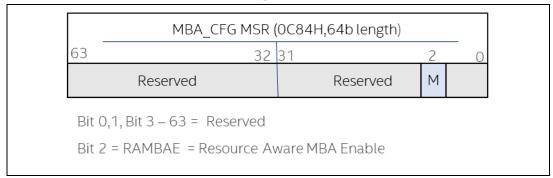

|        | Figure B-2. The MBA_CFG MSR for Enabling Resource Aware MBA Feature 83                           |

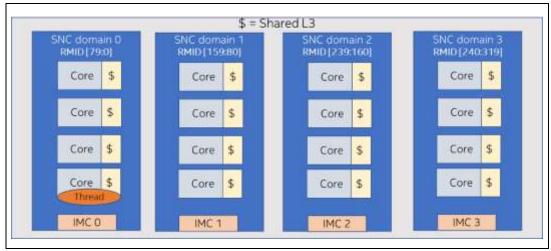

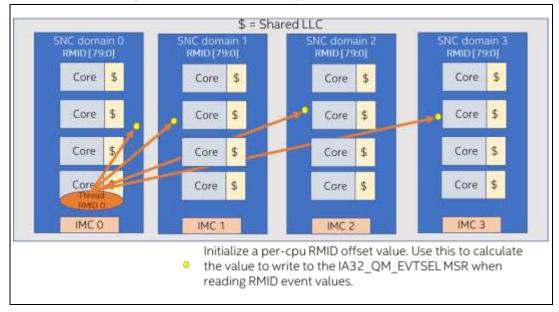

|        | Figure B-3. Default Mode Demonstrating SNC-4 and RMID Distribution 85                            |

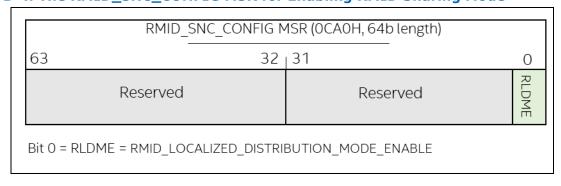

|        | Figure B-4. The RMID_SNC_CONFIG MSR for Enabling RMID Sharing Mode . 85                          |

|        | Figure B-5. RMID Sharing Mode Demonstrating SNC-4 and RMID Distribution                          |

|        |                                                                                                  |

| Tables |                                                                                                  |

| rabics |                                                                                                  |

|        | Table 1-1 Glossary                                                                               |

|        | Table 1-1. References                                                                            |

|        | Table 3-1. MBA_CFG MSR Definition                                                                |

|        | Table 5-1. IRDT Table Format (Variable Length)54                                                 |

|        | Table 5-2. RMUD Table Format (Variable length)55                                                 |

|        | Table 5-3. DSS Table Format (Variable length)                                                    |

|        | Table 5-4. RCS Table Format (Currently 40B)                                                      |

|        | Table 6-1. MMIO Table Format                                                                     |

|        | Table 7-1. Example CMT and MBM Counter Values                                                    |

|        | Table B-1. SNC Enabled and RMID Distribution Mode Summary                                        |

|        | Table b 2. Local and Total Could Increment90                                                     |

# intel

| Table B-3. Local and Total Bandwidth Example                  | . 90 |

|---------------------------------------------------------------|------|

| Table B-4. STLB QoS Enumeration in IA32_CORE_CAPABILITIES MSR |      |

| Table B-5. STLB_QOS_INFO MSR Definition                       | . 92 |

| Table B-6. STLB_QOS_MASK_N MSR Definition                     | . 93 |

| Table B-7. STLB_FILL_TRANSLATION MSR Definition               | . 93 |

| Table B-8. Processor support list                             | . 94 |

# **Revision History**

| Revision<br>Number | Description                      | Date           |

|--------------------|----------------------------------|----------------|

| 001                | Initial release of the document. | September 2023 |

Document Number: 356688-001US, Revision: 1.0

# intel. *Glossary*

**Table 1-1 Glossary**

| Acronym                                                          | Term                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI                                                             | Advanced Configuration and Power Interface           | Advanced Configuration and Power Interface is an open standard that operating systems can use to discover and configure computer hardware components, to perform power management, auto configuration, and status monitoring.                                                                                                                                                               |

| CAT                                                              | Cache Allocation<br>Technology                       | Software-guided redistribution of cache capacity is enabled by CAT, enabling important data center VMs, containers or applications to benefit from improved cache capacity and reduced cache contention. CAT may be used to enhance runtime determinism and prioritize important applications.                                                                                              |

| CDP                                                              | Code and Data<br>Prioritization                      | As a specialized extension of CAT, Code and Data Prioritization (CDP) enables separate control over code and data placement in the L2 cache and the last-level (L3) cache. Certain specialized types of workloads may benefit with increased runtime determinism, enabling greater predictability in application performance.                                                               |

| СН                                                               | Channel                                              | An I/O device channel, used to communicate between a device and an I/O Block and onto the coherent fabric.                                                                                                                                                                                                                                                                                  |

| CLOS                                                             | Class(es) of Service                                 | A fundamental tag in RDT used for resource controls                                                                                                                                                                                                                                                                                                                                         |

| СМТ                                                              | Cache Monitoring<br>Technology                       | Monitors the last-level cache (L3) utilization by individual threads, applications, or Virtual Machines, CMT improves workload characterization, enables advanced resource-aware scheduling decisions, aids "noisy neighbor" detection and improves performance debugging.                                                                                                                  |

| Intel® RDT                                                       | Intel® Resource Director<br>Technology               | Intel® RDT is the "umbrella" technology name for Intel's Platform Quality of Service technologies, including CPU Agents and Non-CPU Agents.                                                                                                                                                                                                                                                 |

| I/O Intel®<br>Resource<br>Director<br>Technology<br>(Intel® RDT) | I/O Device Intel®<br>Resource Director<br>Technology | Intel RDT technologies specifically focusing on I/O devices including PCIe, CXL and integrated accelerators                                                                                                                                                                                                                                                                                 |

| МВА                                                              | Memory Bandwidth<br>Allocation                       | MBA enables approximate and indirect control over memory bandwidth available to workloads, enabling new levels of interference mitigation and bandwidth shaping for "noisy neighbors" present on the system.                                                                                                                                                                                |

| МВМ                                                              | Memory Bandwidth<br>Monitoring                       | Multiple VMs or applications can be tracked independently via Memory Bandwidth Monitoring (MBM), which provides memory bandwidth monitoring for each running thread simultaneously. Benefits include detection of noisy neighbors, characterization and debugging of performance for bandwidthsensitive applications, and more effective non-uniform memory access (NUMA)-aware scheduling. |

| Acronym | Term                          | Description                                                                                                                                                                           |

|---------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MMIO    | Memory Mapped I/O             | I/O Intel RDT defines a series of MMIO-mapped interfaces to enable association of I/O devices to RMIDs and CLOS for monitoring and control.                                           |

| PQR     | PQR                           | A shorthand for the IA32_PQR_ASSOC MSR, which associates IA threads to RMID and CLOS tags.                                                                                            |

| RMD     | Resource Management<br>Domain | A set of features defined within a particular cache domain, such as an L3 cache supporting a number of logical processors.                                                            |

| RTD     | Resource Telemetry<br>Domain  | A Resource Management Doman within which one or more resource monitoring (telemetry) controls are supported                                                                           |

| RAD     | Resource Allocation<br>Domain | A Resource Management Doman within which one or more resource allocation controls are supported                                                                                       |

| RMID    | Resource Monitoring ID(s)     | A fundamental tag used for resource monitoring in Intel RDT.                                                                                                                          |

| SoC     | System-on-Chip                | An integrated chip composed of host processors, accelerators, memory, and I/O agents.                                                                                                 |

| TC      | Traffic Class                 | A PCI Express feature that allows differentiation of transactions to apply appropriate servicing policies.                                                                            |

| VC      | Virtual Channel               | A PCI Express feature for differential bandwidth allocation. Virtual channels have dedicated physical resources (buffering, flow control management, and so on) across the hierarchy. |

| VMM     | Virtual Machine Monitor       | A software layer that controls virtualization.                                                                                                                                        |

# 1 Introduction

This document defines the architecture of the Intel® Resource Director Technology (Intel® RDT) feature set. The goal of Intel RDT is to bring new levels of monitoring and control over how shared platform resources such as last-level cache (L3) and main memory (typically DRAM) bandwidth are utilized by CPU Agents and non-CPU Agents. The monitoring and allocation are not necessarily applied across the entire system but are applied to a Resource Management Domain (RMD) which corresponds to a set of agents sharing a set of system resources, such as L2 cache capacity, L3 cache capacity, memory bandwidth, and I/O devices. A Resource Management Domain (RMD) consists of a collection of CPU agents or non-CPU agents. The set of CPU agents consist of one or more logical processors associating an RMID and/or CLOS tag with a software thread. Non-CPU agents include PCI Express\* (PCIe\*)/Compute Express Link (CXL)\* devices and integrated accelerators, thus broadly encompassing the set of agents which read from and write to either caches or memory, excluding IA cores.

The Intel RDT feature set provides a series of monitoring and allocation capabilities such as Cache Monitoring Technology (CMT), Memory Bandwidth Monitoring (MBM), Cache Allocation Technology (CAT), Code and Data Prioritization (CDP), Memory Bandwidth Allocation (MBA) and others. These technologies enable monitoring and control of shared platform resources, such as the L3 cache capacity or main memory bandwidth, which may be in use by many applications, containers or VMs running on the platform concurrently. As described in subsequent chapters, these features enable deterministic behavior and fairness in communications, real-time and other usages, and are initially introduced in Section 1.3.

The Intel RDT features are based on a set of architectural tags, described in the following section, and fundamental capabilities for enabling monitoring and control over shared platform resources under the control of an operating system (OS) or virtual machine monitor (VMM), as described in the chapter on Reference Software Architecture.

# 1.1 High Level Usage Models

A wide variety of industry deployment models find value in either enhanced visibility into system resource utilization, or control over shared resources. As a result, a broad set of customer usage models are observed with Intel RDT, including but not limited to:

- **Cloud Hosting in the datacenter** Prioritizing important Virtual Machines (VMs) and containing or mitigating "noisy neighbors".

- **Public/Private Cloud** Isolating an important infrastructure VM which provides networking services such as a VPN to bridge the private cloud to the public cloud.

- **Datacenter Infrastructure** Protecting virtual switches which provide local networking.

- **Communications** Ensuring consistent performance and containing background tasks on a network appliance built atop an Intel® Xeon® Server Platform.

- **Content Delivery Network (CDN)** Prioritizing key parts of the content serving application in order to improve throughput.

- Networking Containing the impact of consolidated or co-located containers to help reduce jitter and reduce packet loss in noisy scenarios, and protecting high-performance applications based on the Dataplane Development Kit (DPDK).

- **Industrial Control** Prioritizing important sections of code to help meet real-time requirements.

Varying usage models drive differing requirements. Datacenter usages may require control over relative container prioritization and management of tail latencies, for instance, while industrial control usages may require strict management of control loop cycle times, including the use of model-specific extended Intel RDT features. A number of examples use cases are described in more detail based on abstracted examples of real-world deployments in the chapter on Reference Software Architecture.

# 1.2 Scope

Broadly, this document discusses the following topics:

- An introduction to key Intel RDT architectural concepts and design philosophy.

- Details of architectural Intel RDT monitoring and allocation features for CPU agents and non-CPU agents.

- Details of model-specific Intel RDT monitoring and allocation features for CPU agents and non-CPU agents.

- Considerations for BIOS writers, and those consuming ACPI enumeration tables generated by BIOS.

- An overview of various real-world software usages of Intel RDT features that have been observed, and recommended software enabling strategies.

The following topics are not covered (or are covered in a limited context):

Intel RDT for CPU Agents and non-CPU Agents architectural details feature enumeration and interfaces using CPUID and configuration using

MSRs. These details are provided in the Intel® 64 Architecture Software

Developer's Manual (SDM), Volume 3B, Chapter Title: Debug, Branch

Profile, TSC, and Intel® Resource Director Technology (Intel® RDT)

Features.

#### 1.3 Audience

The intended audience for this specification includes Intel RDT consumers, users and implementers, across OS/VMM software, resource management driver and control loop developers, administrators, managers of datacenter infrastructure, workload owners and embedded and communications developers. Additionally, this specification may be of interest to those developing utilities, BIOS routines, administrative libraries and orchestration frameworks.

#### 1.4 References

#### Table 1-1. References

#### **Description**

[1] Intel® 64 and IA-32 Architectures Software Developer's Manual.

Volume 3B, Chapters 18.18 and 18.19.

https://software.intel.com/content/www/us/en/develop/articles/intel-sdm.html

[2] Intel® Architecture Instruction Set Extensions and Future Features.

Instruction Set Architecture (intel.com)

[3] Intel® Virtualization Technology for Directed I/O Specification.

http://www.intel.com/content/www/us/en/embedded/technology/virtualization/vt-directed-iospec.html

[4] Unified Extensible Firmware Interface Forum – Links to ACPI-Related Documents (incudes IRDT table title and signature).

https://uefi.org/acpi

[5] PCIe Express Specification, v5.0 or newer.

https://pcisig.com/specifications

[6] Compute Express Link Specification, v1.0 or newer.

https://www.computeexpresslink.org/download-the-specification

[7] User space software for Intel® Resource Director Technology

https://github.com/intel/intel-cmt-cat

# 2 Intel® Resource Director Technology Overview

This chapter provides an overview of Intel® RDT features, including goals, key ingredients, and the architectural framework, which are discussed in more detail in the chapters that follow.

# 2.1 Common Tags

Intel RDT provides a layer of abstraction between applications and logical processors through the use of numeric tags. Both CPU agents and non-CPU agents use the following tags for resource monitoring and allocation, respectively:

- Resource Monitoring IDs (RMIDs) are used for monitoring of shared platform resource utilization.

- Classes of Service (CLOS) are used for control of shared platform resources, such as L3 cache occupancy or memory bandwidth.

The RMID and CLOS tags are described in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B. RMID and CLOS tags are independent. Usage of RMID tags does not affect CLOS, and vice versa (however, when CLOS tags are used to affect resource allocations, the effects may be observed with RMID-based monitoring features.) An RMID-based monitoring feature does not incur hardware overhead or affect a CLOS-based allocation feature. A product may be built to implement RMID-based monitoring features, CLOS-based control features, or both.

For CPU agents, RMIDs and CLOS tags are associated with the operation of a logical processor through the IA32\_PQR\_ASSOC MSR.

For non-CPU agents, a series of MMIO interfaces is used to associate upstream traffic from I/O devices with RMID and CLOS tags, and the numerical interpretation of the tags is the same as for processor traffic. (For example, the RMID value "5" used to track processor thread resource consumption means the same thing as when the RMID value "5" is used to track the cache fill behavior of a PCIe device.) These MMIO interfaces for tagging non-CPU agents are discovered using an ACPI structure called I/O Intel RDT, that is, IRDT. (see Chapter 5.)

# 2.2 L3 Configurations

This specification describes two types of high level L3 configurations that may support Intel RDT features:

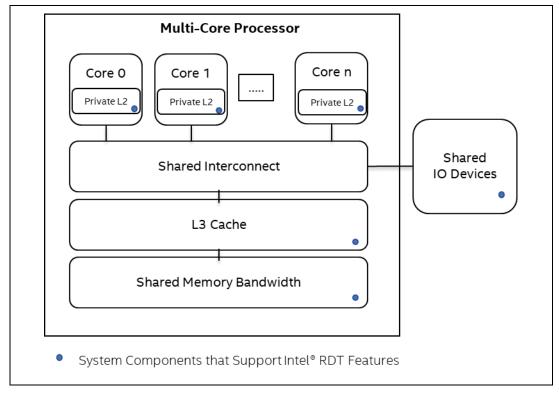

1. **Shared-L3 Configuration:** There is a common shared L3 cache for all the agents in the SoC, as shown in Figure 2-1. This SoC configuration supports interfaces for Intel RDT features based on the CPUID instruction

for feature enumeration and Model-Specific Registers (MSRs) for feature configuration and telemetry retrieval.

Figure 2-1. Shared-L3 Configuration System Model and Presence of Intel® RDT Features

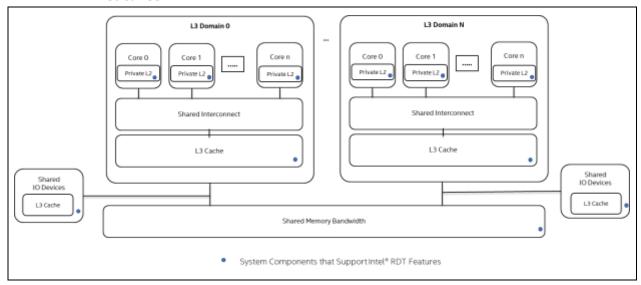

2. **Multiple-L3 Configuration:** There may be more than one L3 cache instances that are local to CPU Agents or non-CPU Agents respectively, as shown in Figure 2-2.

Figure 2-2. Multiple-L3 Configuration System Model and Presence of Intel ® RDT Features

Document Number: 356688-001US, Revision: 1.0

A set of features defined within a particular cache domain, such as an L3 cache supporting a number of logical processors, may be referred to as a Resource Telemetry Domain (RTD, for monitoring features) or a Resource Allocation Domain (RAD, for allocation features). More generally, a resource which supports Intel RDT monitoring features, allocation features or both may be referred to as a Resource Management Domain (RMD). Figure 2-2 shows example of multiple RMDs.

See <u>Appendix A.4</u> for Intel RDT feature mapping for CPU agents and non-CPU agents in different SoC configurations.

# 2.3 Intel® RDT Monitoring Technologies

## 2.3.1 Intel® RDT Monitoring Key Ingredients

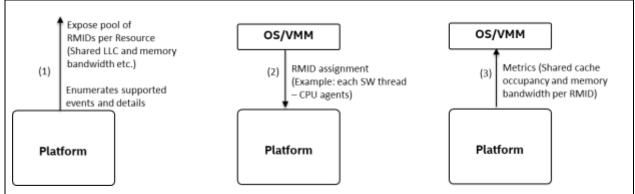

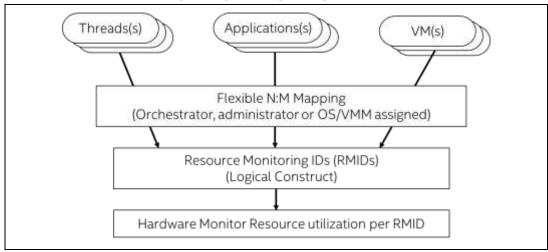

Intel RDT Monitoring enables monitoring shared platform resources, such as L3 cache occupancy and memory bandwidth, based on software-defined Resource Monitoring IDs (RMIDs) that are tagged to applications or VMs on a per-thread basis (Figure 2-3). For CPU Agents, each logical processor exposes the IA32\_PQR\_ASSOC MSR to allow the OS/VMM to specify an RMID when an application, thread or VM is scheduled on a core.

Resource monitoring for the indicated application/thread/VM is then performed by hardware based on the RMID with which it is associated, and software can read back the L3 cache occupancy for a given RMID via counter registers (if the CMT feature is supported for instance). Each thread of an application may be tracked with a distinct RMID, or threads may be grouped into a single RMID, based on the granularity of monitoring required. Threads within a VM, apps within a VM, entire VMs or groups of VMs can similarly be tracked with RMIDs with variable granularity as needed.

Figure 2-3. Intel® RDT Monitoring – Enabling RMID-Based Monitoring for Shared Resources

The basic ingredients of Intel RDT Monitoring are as follows:

CPUID and/or ACPI constructs to indicate support for Intel RDT Monitoring and sub-features (CMT, MBM, and so on) for Resource Telemetry Domains (RTD).

- Enumeration of the total number of RMIDs that can be tracked in the given RTD.

- Mechanisms to allow system software (OS/VMM) to specify the RMID of software threads and non-CPU agents.

- Mechanisms to allow system software to retrieve collected metrics on a per-RMID basis via architectural MSRs or MMIO interfaces.

The first ingredient to make use of Intel RDT Monitoring is to enumerate the set of monitoring capabilities provided on the given Resource Management domain via CPUID or ACPI and determine the number of RMIDs available for tracking on a particular Resource Telemetry Domain (RTD, that is, caching domain). This will allow the OS/VMM to determine how many unique IDs it may use. Given that certain processor topologies may include heterogenous capabilities which vary per-processor, it is recommended that software enumerate Intel RDT CPUID leaves from the perspective of each logical processor (LP) to construct the list of supported capabilities and which resources (such as L3 cache) may be shared among various LPs.

The second ingredient (Intel RDT Monitoring association) allows the OS/VMM to specify the RMID of the running software thread to the platform for CPU agents. The OS/VMM can also specify the RMID for upstream traffic and operation of non-CPU agents.

The third ingredient (Intel RDT marking and associated hardware support) enables each memory request from the CPU agents and non-CPU agents to be tagged with the RMID provided by the OS/VMM.

The fourth ingredient is Intel RDT Monitoring reporting. When the monitoring data retrieval register is programmed with the RMID and the specific event code of interest (L3 Cache Occupancy for example), this information is appropriately retrieved and provided back.

Multiple Intel RDT Monitoring features may exist within a platform, but the software should not assume that the presence of one Intel RDT Monitoring feature implies the existence of any others. Intel RDT features are independently enumerated in the sequence described in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, Section 18.18.4, in order to avoid ambiguous situations.

## 2.3.2 Shared-L3 versus Multiple-L3 Configuration

Intel RDT Monitoring features may have different scope definitions depending on L3 configuration. With the shared-L3 configuration, CPU agents and non-CPU agents allocate into a shared L3 cache. Hence, all monitoring features have a consistent definition for CPU agents and non-CPU agents.

With the multiple-L3 configuration, non-CPU agents may have a separate nearby L3 cache which is distinct from CPU agents' L3 cache. Hence, monitoring features may have different definitions for CPU agents and non-CPU agents. For example, in certain implementations, non-CPU agents with a near

L3 cache implementation may report memory bandwidth monitoring data from the near cache only.

# 2.4 Intel® RDT Allocation Technologies

## 2.4.1 Intel® RDT Allocation Key Ingredients

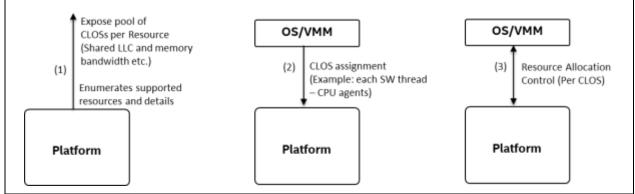

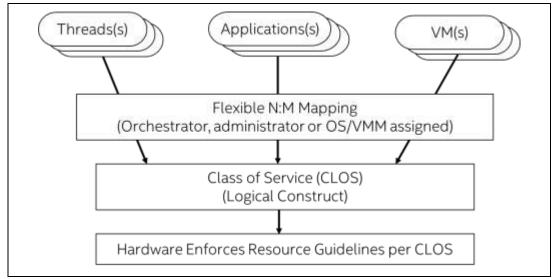

Intel RDT Allocation enables resource allocation based on Class of Service (CLOS) tags. The processor exposes Classes of Services into which applications (or individual threads) and traffic from I/O devices may be assigned. A CLOS may have multiple associated resource allocation properties. For example, there may exist controls for each CLOS to specify L2 capacity available to that CLOS, L3 capacity available, memory bandwidth available, and other properties (Figure 2-4).

In the case of L3 capacity control features, for instance, such as Cache Allocation Technology (CAT), the cache allocation for a given is restricted based on the class with which they are associated. Similarly, in certain implementations supporting non-CPU agent controls, context-associated and upstream traffic from I/O devices may be controlled as it utilizes shared system resources. Each CLOS can be configured using bitmasks which represent capacity, and the degree of overlap and isolation between classes in allocation features which influence the SOC caches.

For CPU agents, each logical processor exposes the IA32\_PQR\_ASSOC MSR to allow the OS/VMM to specify a CLOS when an application, thread or VM is scheduled. Cache Allocation for the application/thread/VM is then controlled based on the CLOS and the associated bitmask.

Figure 2-4. Intel® RDT Allocation – Enabling CLOS-based Allocation for Shared Resources

The basic ingredients of Intel RDT Allocation are as follows:

CPUID or ACPI constructs to indicate whether Intel RDT Allocation and subfeatures (CAT, MBA, and so on) for Resource Allocation Domains (RADs) are supported and enumerate the total number of CLOS that may be associated to shared platform resources on the platform.

- Mechanisms to allow system software (OS/VMM) to specify the CLOS of software threads and non-CPU agents.

- Mechanisms to allow system software to configure the shared platform resource levels available to each CLOS via architectural MSRs or MMIO interfaces.

The first ingredient to make use of Intel RDT Allocation is to enumerate the level of allocation capability provided on the given Resource Allocation Domain via CPUID and/or ACPI and determine the number of CLOSs available for allocating shared platform resources on a particular RAD (that is, a certain L3 caching domain). This will allow the OS/VMM to determine how many unique IDs it may use. Given that certain processor topologies may include heterogenous capabilities which vary per-processor, it is recommended that software enumerate Intel RDT CPUID leaves from the perspective of each logical processor (LP) to construct the list of supported capabilities and which resources (such as L3 cache) may be shared among various LPs.

The second ingredient (Intel RDT Allocation association) allows the OS/VMM to specify the CLOS of the running software thread to the platform for CPU agents. The OS/VMM can also specify the CLOS for upstream traffic and operation of non-CPU agents.

The third ingredient (Intel RDT marking and associated hardware support) enables each memory request from CPU agents and non-CPU agents to be tagged with the CLOS provided by the OS/VMM.

The fourth ingredient is Intel RDT Allocation control, when the allocation register is programmed with the CLOS and allocation control is performed by the specific shared platform resource (L3 Cache capacity for example).

Multiple Intel RDT Allocation features may exist within a platform. The software should not assume that the presence of one RDT Allocation feature implies the existence of any others. Intel RDT features are independently enumerated in the sequence described in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, in order to avoid ambiguous situations.

## 2.4.2 Shared-L3 versus Multiple-L3 Configuration

Intel RDT Allocation features may have different definitions depending on L3 configuration. With the shared-L3 configuration, CPU agents and non-CPU agents allocate into a shared-L3 cache. Hence, all allocation features have a consistent definition for CPU agents and non-CPU agents. With the multiple-L3 configuration, non-CPU agents may have a separate near L3 cache which is different from the CPU agents' L3 cache. Hence, allocation features may have different definitions for CPU agents and non-CPU agents. For example, non-CPU agents with a near L3 cache implementation provide separate interfaces for cache capacity allocation for the near L3 cache.

<u>Chapter 3</u> and <u>Chapter 4</u> provide details about each Intel RDT Monitoring and Allocation features for CPU agents and non-CPU agents.

# 3 Intel® Resource Director Technology for CPU Agents

This chapter contains an overview of the Intel RDT features for CPU agents. Chapter 4 describes details about features for non-CPU agents.

# 3.1 Intel® RDT Monitoring Features

The Intel RDT Monitoring architecture enables monitoring of the utilization level of critical shared platform resources and provides this data directly to the Hypervisor, Operating System or other privileged software. Intel RDT Monitoring supports three event codes: 1) L3 cache occupancy 2) L3 Total External bandwidth 3) L3 Local External bandwidth. This allows more efficient scheduling based on resource use, as well as application tuning and performance prediction based on resource use characterization, and optionally better reporting and billback. This functionality complements Intel RDT Allocation, which provides control over shared platform resources available to CPU agents.

#### 3.1.1 Common Framework

The following mechanisms are shared by Intel RDT Monitoring features:

- CPUID feature bits to enumerate the presence of the Intel RDT Monitoring capabilities and the details of each sub feature.

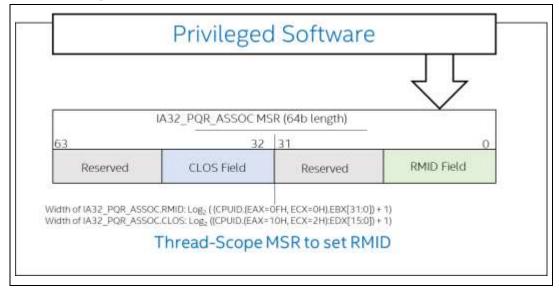

- The IA32\_PQR\_ASSOC MSR, which the OS or Hypervisor uses to specify the RMID for each software thread scheduled to run on a logical processor. See Figure 3-2.

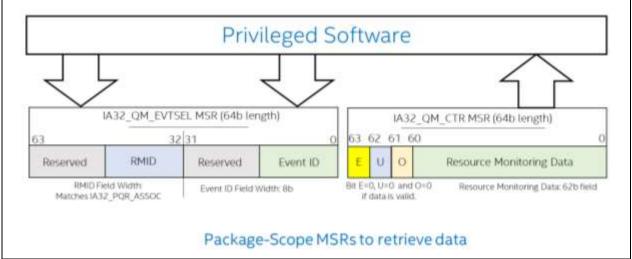

- The IA32\_QM\_EVTSEL and IA32\_QM\_CTR MSRs, to read cache occupancy and bandwidth statistics. See Figure 3-3.

Software may flexibly associate RMIDs with threads, applications, VMs, or containers. (See Figure 3-1). If multiple logical processors within a Resource Telemetry Domain (RTD) are assigned the same RMID, the total resource monitoring telemetry by these logical processors will be accumulated together and the total reported by hardware.

Monitoring data is retrieved using a window-based interface. Software writes an event ID and RMID to the IA32\_QM\_EVTSEL MSR and hardware provides the resulting data back in the IA32\_QM\_CTR MSR.

Refer to Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, for details on CPUID and MSR usage.

Figure 3-1. Resource Monitoring IDs (RMIDs) Assignment Flow

Figure 3-2. IA32\_PQR\_ASSOC MSR to Set RMID

Figure 3-3. IA32\_QM\_EVTSEL and IA32\_QM\_CTR MSRs

## 3.1.2 Cache Occupancy Monitoring Technology

Intel RDT Cache Occupancy Monitoring Technologies provide visibility into cache utilization. Features such as Cache Monitoring Technology (CMT) provide occupancy counters on a per-RMID basis such that cache occupancy by each RMID may be tracked and read back in real-time during system operation.

More specific feature details about CMT are provided in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B. Note that the MSRs are listed in <u>Appendix A.5</u>. See <u>Appendix A.2</u> for CMT feature supported product details.

## 3.1.2.1 L3 Cache Monitoring Technology

L3 Cache Monitoring Technology (CMT) allows an Operating System, Hypervisor or similar system management agent to determine the usage of L3 cache of the Resource Telemetry Domain (RTD) by applications running on the platform.

## 3.1.3 Memory Bandwidth Monitoring

Memory Bandwidth Monitoring (MBM) provides monitoring of bandwidth from one level of the cache or resource hierarchy to the next, allowing bandwidth-aware scheduling decisions, inter-RTD scheduling optimization, and enabling feedback to bandwidth allocation features which allow control over memory bandwidth.

More specific feature details about MBM are provided in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B. Note that the MSRs are listed in <u>Appendix A.5</u>. See <u>Appendix A.2</u> for MBM feature supported product details.

#### 3.1.3.1 L3 Total and Local External Memory Bandwidth Monitoring

L3 Total and Local External Memory Bandwidth Monitoring allows system software to monitor the use of bandwidth between L3 cache and local or remote memory. In certain implementations, MBM is not guaranteed to track directory and Extended Prediction Table (XPT) prefetcher traffic.

## 3.2 Intel® RDT Allocation Features

The Intel RDT Allocation architecture enables control over utilization level of critically shared platform resources and provides this control directly to the Hypervisor or Operating System. This allows more efficient resource usage as well as application prioritization and determinism restoration based on resource repartitioning. The implementation of Intel RDT Allocation features may be product-specific or architectural. These capabilities compliment Intel RDT monitoring, which provides insight into shared platform resource utilization by CPU agents.

#### 3.2.1 Common Framework

The following mechanisms are shared by Intel RDT allocation features:

- CPUID feature bits to enumerate the presence of Intel RDT Allocation capabilities and the details of each sub feature.

- The IA32\_PQR\_ASSOC MSR which software uses to specify the CLOS for each software thread. See Figure 3-5.

- Mechanisms in hardware to specify resource usage to apply to each Class of Service.

Software can flexibly associate Classes of Service with threads, applications, VMs, or containers (see Figure 3-4). CLOS values are shared across all allocation features. A particular numeric CLOS value has the same meaning from the viewpoint of all cores. Each CLOS has an associated set of mask registers as described later to associate that CLOS with a fraction of the shared platform resources. If multiple logical processors within a Resource Allocation Domain (RAD) are assigned the same CLOS, then resource allocations associated with that CLOS will be shared among that set of logical processors.

Figure 3-4. Classes of Service (CLOS) Association Flow

Figure 3-5. The IA32\_PQR\_ASSOC MSR to Set CLOS

For each resource, a block of registers is defined for software to configure the allocation values for each CLOS. The definition of the register fields depends on the type of resource being managed and is discussed in subsequent sections.

# **3.2.2 Cache Occupancy Allocation Technologies**

A family of Cache Occupancy Allocation Technologies allows control over shared cache space on a per-CLOS basis, enabling both isolation and overlap for better throughput, fairness, determinism and differentiation. Typically, these features are known as Cache Allocation Technology (CAT), which is the term used in this document. Certain processors may support architectural or model-specific forms of CAT depending on the product generation. Model-specific implementations are discussed in Appendix B.1.4.

More specific feature details about CAT are provided in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B. Note that the MSRs are listed in <u>Appendix A.5</u>. See <u>Appendix A.2</u> for CAT feature supported product details.

#### 3.2.2.1 L2 Cache Allocation Technology

L2 Cache Allocation Technology (L2 CAT) allows system software to specify the amount of L2 cache space of the Resource Allocation Domain into which an application can fill.

#### 3.2.2.2 L2 Cache Code and Data Prioritization

L2 Code Data Prioritization (L2 CDP) provides differentiation between code and data for L2 cache usage by a single Class of Service. In a case where an application has a large code footprint which can overwhelm data in the cache, or vice versa, the ability to separately prioritize code and data is valuable.

L2 CDP provides a pair of allocation bitmasks for each Class of Service (rather than a single bitmask per CLOS as in L2 CAT), to allow system software to independently configure the amount of L2 cache available to code and data.

#### 3.2.2.3 L3 Cache Allocation Technology

L3 Cache Allocation Technology (L3 CAT) allows an Operating System (OS), a Hypervisor, Virtual Machine Manager (VMM), or similar system service management agent to specify the amount of L3 cache space within a Resource Allocation Domain into which a CLOS may fill.

#### 3.2.2.4 L3 Cache and Data Prioritization

L3 Code Data Prioritization (L3 CDP) provides differentiation between code and data for L3 usage by a single Class of Service. In a case where an application has a large code footprint which can overwhelm data in the cache, or vice versa, the ability to separately prioritize code and data is valuable.

L3 CDP provides a pair of allocation bitmasks for each Class of Service (rather than a single bitmask per CLOS as in L3 CAT), to allow system software to independently configure the amount of L3 cache available to code and data.

## 3.2.3 Memory Bandwidth Allocation

Memory Bandwidth Allocation (MBA) allows the system software to control access bandwidth to memory. It allows slowing "noisy neighbor" threads which may be overutilizing bandwidth and enables the creation of closed-loop control systems (monitoring and control combined) by exposing control over a credit-based throttling mechanism.

More specific feature details about MBA are provided in the Intel $^{\$}$  64 and IA-32 Architectures Software Developer's Manual, Volume 3B. Note that the MSRs are

listed in <u>Appendix A.5</u>. See <u>Appendix A.2</u> for MBA feature supported product details.

There are three different generations of MBA, each extending additional capabilities:

- First Generation MBA (Interface Scope) This is initial implementation of the MBA feature which provides indirect and approximate control over memory bandwidth available per-core. See Section 3.2.3.1 for implementation details and see Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, for legacy enumeration, interface and per-CLOS delay value resolution details.

- 2. Second Generation MBA (Interface Scope) This enhanced MBA capability provides improved efficiency and accuracy in throttling, along with providing increased system throughput. Rather than a strict bandwidth control mechanism, a dynamic hardware controller is implemented, which can react to changing bandwidth conditions at the microsecond level. Before using the second-generation MBA feature, the MBA hardware controller requires a BIOS-assisted calibration process that may include inputs such as the number of memory channels populated and other system parameters; this is a change from the first generation of MBA.

- Intel's BIOS reference code includes a default configuration that is recommended for general usage, and BIOS profiles may be created with alternate tuning values to optimize for certain usages (such as stricter throttling). See <a href="Section 3.2.3.2">Section 3.2.3.2</a> for implementation details and Intel® 64 and the IA-32 Architectures Software Developer's Manual, Volume 3B, for legacy enumeration and interface details.

- 3. Third Generation MBA (Agent Scope) The third generation MBA feature on future processors based on the codename Granite Rapids microarchitecture further enhances MBA with per-logical-processor control and a further improved controller design. Total memory bandwidth (all L3 miss traffic) is now managed by MBA 3.0. This implementation follows the past MBA precedent of delivering significant enhancements without a major software overhaul, and while preserving backward compatibility. See <a href="Section 3.2.3.3">Section 3.2.3.3</a> for implementation details and Intel® 64 and the IA-32 Architectures Software Developer's Manual, Volume 3B, for legacy enumeration and interface details.

MBA performance properties change over time, for instance enhancing system-level efficiency. Software should not assume that performance properties or specific tunings of MBA remain identical across product generations. Third generation MBA shifts from interface-scope to agent-scope throttling support, and scheduler re-tuning to take advantage of this enhancement may be beneficial. Legacy architectural implementations of MBA are enumerated in the sequence described in Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, in order to avoid ambiguous situations.

The MBA feature provides the following architectural components:

• A mechanism to enumerate the MBA capability to control the bandwidth from each level of the cache (for example, L2, L3) to the next level.

- A mechanism for the OS or Hypervisor to configure the amount of bandwidth available to a particular Class of Service via a throttling value (discussed later).

- Mechanisms for the OS or Hypervisor to specify the Class of Service to which a thread belongs.

- Hardware mechanisms to guide and enforce the delay value at each level of the cache hierarchy when an application has been designated to belong to a specific Class of Service.

Note that in some usages such as those seeking bandwidth control in MB/s, MBA may require either application-level performance feedback or complimentary Memory Bandwidth Monitoring (MBM) to use in the most optimal way. Backward compatibility of the software interfaces is preserved, and enhanced MBA generational changes manifest as enhancements atop the MBA feature baseline.

#### 3.2.3.1 First Generation Memory Bandwidth Allocation

The Memory Bandwidth Allocation (MBA) feature provides indirect and approximate control over memory band-width available per-core and was introduced on the Intel® Xeon® Scalable Processor Family. This feature provides a method to control applications which may be over-utilizing bandwidth relative to their priority in environments such as the datacenter.

The MBA feature uses existing constructs from the Intel RDT feature set including Classes of Service (CLOS). A given CLOS used for L3 CAT for instance means the same thing as a CLOS used for MBA. Infrastructure such as the MSR used to associate a thread with a CLOS (the IA32\_PQR\_ASSOC\_MSR) and some elements of the CPUID enumeration (such as CPUID leaf 10H [Cache Allocation Technology Enumeration Leaf]) are shared.

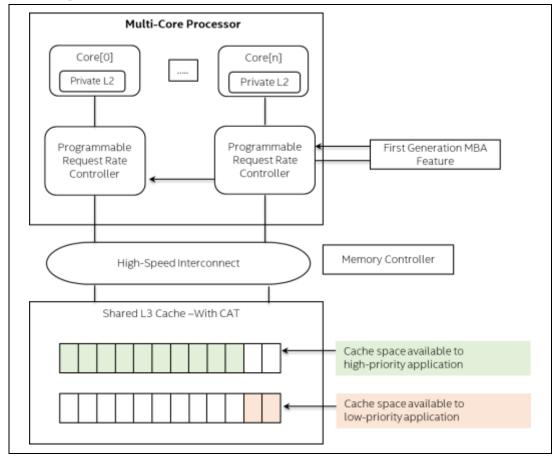

The high-level implementation of Memory Bandwidth Allocation is shown in Figure 3-6.

Figure 3-6. A High-Level Overview of the First-Generation MBA Feature

As shown here, the MBA feature introduces a programmable request rate controller between the cores and the high-speed interconnect, enabling indirect control over memory bandwidth for cores over-utilizing bandwidth relative to their priority. For instance, high-priority cores may be run un-throttled, but lower priority cores generating an excessive amount of traffic may be throttled to enable more bandwidth availability for the high-priority cores.

Because the MBA uses a programmable rate controller between the cores and the interconnect, higher-level shared caches and memory controller, bandwidth to these caches may also be reduced, so care should be taken to throttle only bandwidth-intense applications which do not use the off-core caches effectively.

The throttling values exposed by MBA are approximate and are calibrated to specific traffic patterns. As workload characteristics vary, the throttling values provided may affect each workload differently. In cases where precise control is needed, the Memory Bandwidth Monitoring (MBM) feature can be used as input to a software controller which makes decisions about the MBA throttling level to apply.

Legacy enumeration and configuration details are discussed in Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B.

#### 3.2.3.1.1 Usage Considerations

As the memory bandwidth control that MBA provides is indirect and approximate, using the feature with a closed-loop controller to also monitor memory bandwidth and how effectively the applications use the cache (via the Cache Monitoring Technology feature) may provide additional value. This approach also allows administrators to provide a bandwidth target or set point which a controller could use to guide MBA throttling values applied, and this allows bandwidth control independent of the execution characteristics of the application.

As control is provided per processor core (the max of the delay values of the per-thread CLOS applied to the core), the user should take care in scheduling threads so as to not inadvertently place a high-priority thread (with zero intended MBA throttling) next to a low-priority thread (with MBA throttling intended), which would lead to inadvertent throttling of the high-priority thread, as the maximum resolved throttling value is applied.

#### 3.2.3.2 Second Generation Memory Bandwidth Allocation

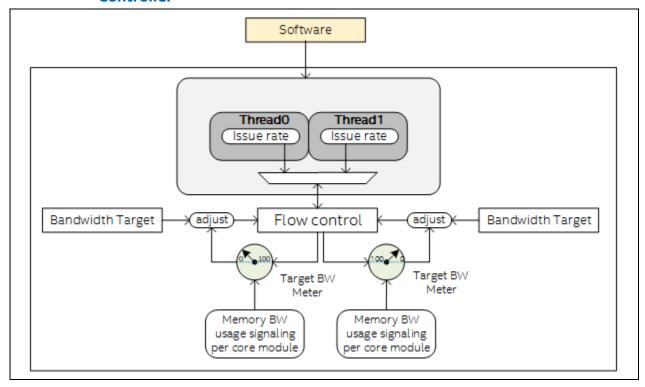

The second generation of Memory Bandwidth Allocation (MBA) is implemented in the 3<sup>rd</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor Family, and related Intel Atom<sup>®</sup> processors such as the P5000 Series. This enhanced MBA capability provides improved efficiency and accuracy in throttling, along with providing increased system throughput. Rather than a strict bandwidth control mechanism, a dynamic hardware controller is implemented, which can react to changing bandwidth conditions at the microsecond level.

Before using the second-generation MBA feature, the MBA hardware controller requires a BIOS-assisted calibration process that may include inputs such as the number of memory channels populated and other system parameters; this is a change from the first generation of MBA. Intel BIOS reference code includes a default configuration that is recommended for general usage, and BIOS profiles may be created with alternate tuning values to optimize for certain usages (such as stricter throttling) as described in the subsequent BIOS Considerations chapter.

Second generation MBA moves from static throttling at the core/uncore interface, to a more dynamic control method based on a hardware controller that tracks actual main memory bandwidth. This allows software that uses primarily the L3 cache to observe increased throughput for a given throttling level, or fine-grained throughput benefits for software that exhibits L3-bound phases. Due to the closer consideration of memory bandwidth loading, this enhancement may lead to an increase in system efficiency when using second generation MBA relative to prior implementations of the feature. Backward compatibility of the software interfaces is preserved, and second-generation MBA changes manifest as enhancements atop the MBA feature baseline.

As with the prior generation feature, the second generation MBA uses CPUID for enumeration and throttling is performed using a mapping created from software thread-to-CLOS (in the IA32\_PQR\_ASSOC MSR), which is then mapped per-CLOS to delay values via the IA32\_L2\_QoS\_Ext\_BW\_Thrtl\_n

29

MSRs. A privileged operating system or virtual machine manager software may specify a per-CLOS delay value, 0-90% bandwidth throttling for instance, though the max and granularity values are platform dependent and enumerated in CPUID.

#### 3.2.3.2.1 Second Generation MBA Advantages

Additional features added over first generation MBA are described next:

- 1. Previously, only the maximum delay value across two CLOS on a physical core could be selected in MBA. Second generation MBA allows a minimum delay value to be selected instead, which may enhance usage with Intel® Hyper-Threading Technology.

- 2. Only a single preprogrammed calibration table was possible in first generation MBA, meaning different memory configurations had the potential for different linearity and percent delay value error values depending on the configuration. This is addressed by the BIOS support in the second generation of MBA, and certain BIOS implementations may program a different calibration table per memory configuration, for instance.

- 3. The second-generation MBA controller provides the ability to more closely monitor the memory bandwidth loading and deliver more optimal results.

- 4. The new MBA hardware controller reduces the need for a fine-grained software controller to manage application phases for optimal efficiency. Note that a software controller may still be valuable to translate MBA throttling values to bandwidths in GB/s or application Service Level Objectives (SLOs), such as performance targets.

Document Number: 356688-001US, Revision: 1.0

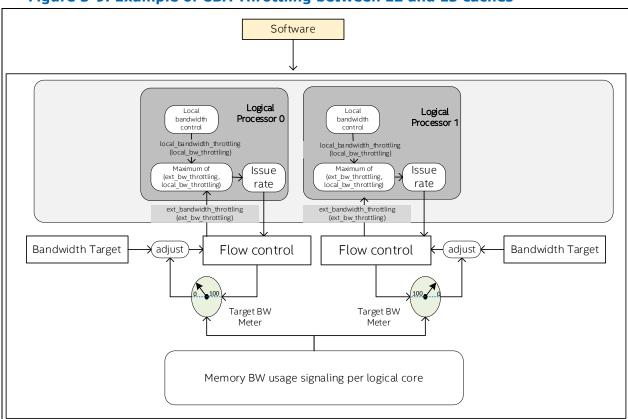

Figure 3-7. Second Generation MBA, Including a Fast-Responding Hardware Controller

The second-generation MBA implementation is shown in Figure 3-7. The feature operates through the use of an advanced hardware controller and feedback mechanism, which allows automated hardware monitoring and control around the user-provided delay value set point. This set point and associated throttling value infrastructure remains unchanged from prior generation MBA, preserving software compatibility.

MBA enhancements, in addition to the new hardware controller, include:

- 1. Configurable delay selection across threads.

- MBA 1.0 implementation statically picks the max MBA Throttling Level (MBAThrotLvl) across the threads running on a core (by calculating value = max(MBAThrotLvl(CLOS[thread0]), MBAThrotLvl(CLOS[thread1]))).

- Software may have the option to pick either maximum or minimum delay to be resolved and applied across the threads; maximum value remains the default.

- 2. Increasing CLOSIDs from 8 to 15 in certain implementations (product-specific, see CPUID)

- Previous certain implementations of the feature provided 8 CLOS tags for MBA.

- The 3<sup>rd</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor Family and related Intel Atom<sup>®</sup> processors, such as the P5000 Series, increase this value to 15 (also consistent with L3 CAT).

#### 3.2.3.2.2 Software-Visible Changes

A new model specific MSR is introduced with second generation MBA to allow software to select from the maximum (default) or minimum of resolved throttling values (see the previous formula). This capability is controlled via a bit in the new MBA\_CFG MSR, shown in Table 3-1.

Table 3-1. MBA\_CFG MSR Definition

| Register Address |         | Architectural MSR Name | Description                                                          |

|------------------|---------|------------------------|----------------------------------------------------------------------|

| Hex              | Decimal | / Bit Fields           | Description                                                          |

| C84H             | 3204    | MBA_CFG                | MBA Configuration Register                                           |

|                  |         | 0                      | Min (1) or max (0) of per-thread MBA delays.                         |

|                  |         | 63:1                   | Reserved. Attempts to write to reserved bits result in a $\#GP(0)$ . |

Note that bit[0] for min/max configuration is supported in second generation MBA but is removed in the third generation MBA when the controller logic becomes capable of managing throttling values on a per-logical-processor or per-agent basis. The transient nature of this enhancement is why the min/max control remains model specific.

To enumerate and manage support for the model-specific min/max feature, software may use processor family/model/stepping to match supported products, then CPUID to later detect enhanced third generation MBA support.

### **3.2.3.3 Third Generation Memory Bandwidth Allocation**

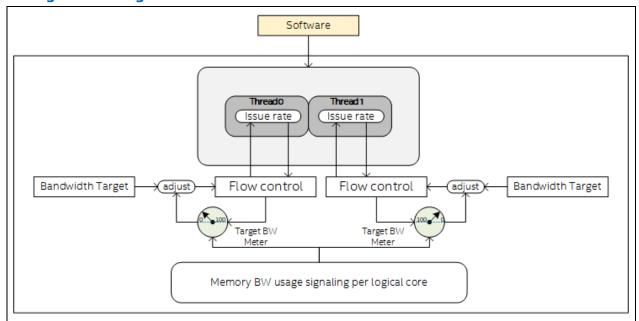

The third-generation MBA feature on future processors based on the codename Granite Rapids microarchitecture further enhances the feature with per-logical-processor control and a further improved controller design. Total memory bandwidth (all L3 miss traffic) is now managed by MBA.

This implementation follows the past MBA precedent of delivering significant enhancements without a major software overhaul, and while preserving backward compatibility.

#### 3.2.3.3.1 Hardware Changes

The third generation of MBA builds upon the hardware controller introduced in the previous generation, which enabled significant system-level benefits, while providing the new capability to independently throttle logical processors, rather than more coarse-grained per-core throttling in prior generations. Throttling values are no longer selected as the "min" or "max" of the two throttling values for the threads running on the core; instead, throttling values are independently and directly applied to each logical processor. The third generation MBA implementation is shown in Figure 3-8.

Figure 3-8. High-Level Overview of the Third Generation MBA Feature

While this enhancement means that more direct throttling of threads is possible, re-tuning of software may be helpful to comprehend the effects of Intel® Hyper-Threading Technology contention versus cache and memory contention, and the effects on software performance.

#### **3.2.3.3.2 Software-Visible Changes**

In order to allow software to change its tuning behavior and detect that perlogical-processor throttling is supported on a particular product generation, a CPUID bit is added to the MBA CPUID leaf to indicate support. See "CPUID—CPU Identification" in Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B for details.

Despite another significant improvement of the hardware controller infrastructure architecture and improved capabilities, controller responsiveness, new internal microarchitecture, and transient-arresting capabilities, no new software interface changes are required to make use of the third generation of MBA relative to prior generations. Software previously using the second-generation MBA min/max selection capability should discontinue the use of the MBA\_CFG MSR. The third-generation MBA capabilities are the default mode of operation on the codename Granite Rapids server microarchitecture.

Note that the MBA MSRs are listed in <u>Appendix A.5</u> for completeness, but details of these legacy MSRs are available in Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B. See <u>Appendix A.2</u> for MBA feature supported product details.

#### 3.2.4 Cache Bandwidth Allocation

Cache Bandwidth Allocation (CBA) allows an Operating System, Hypervisor, or similar system management agent to control internal core and downstream memory bandwidth for each of the logical processors. This feature is complimentary to MBA and provides OS/VMMs with the ability to throttle threads within the core.

The CBA feature along with the existing MBA feature provides a system-wide mechanism to throttle the bandwidth across different caches in the system including external memory, as well as control within a processor core or module. In combination, CBA and MBA provide both deterministic control and dynamic management of bandwidth resources to meet system Service Level Objectives (SLOs). The CBA feature reuses and extends existing constructs from the Intel RDT feature set including Classes of Service (CLOS).

A given CLOS used for L3 CAT for instance means the same thing as a CLOS used for CBA. Infrastructure such as the MSR used to associate a thread with a CLOS (the IA32\_PQR\_ASSOC\_MSR) and some elements of the CPUID enumeration (such as CPUID leaf 10H (Cache Allocation Technology Enumeration Leaf)) are shared.

The Cache Bandwidth Allocation (CBA) feature provides control over bandwidth available between Level 1 (L1) caches, Level 2 (L2) Caches, and Level 3 (L3) Caches (as applicable) for each of the logical processors. Since reducing upstream bandwidth can also reduce bandwidth to external memory, this also provides an indirect control of memory bandwidth. This indirect control of external memory bandwidth can also reduce memory bandwidth. The CBA feature along with the MBA provides a mechanism to control the bandwidth of different applications.

Software should understand that the effective throttling of an application may be whichever of CBA or MBA specifies more throttling.

Similar to Intel RDT features, CBA includes the following key ingredients:

- A mechanism to enumerate the CBA capability to control the bandwidth from each level of the cache (for example, L1, L2, L3) to the next level (CPUID).

- A mechanism for the OS or Hypervisor to configure the amount of bandwidth available to a logical processor with a particular Class of Service via a throttle Level (MSRs, discussed later).

- Mechanisms for the OS or Hypervisor to signal the Class of Service to which an application belongs (the PQR MSR).

- Hardware mechanisms to guide and enforce the bandwidth throttle level across the cache hierarchy.

In some usages, the software may measure the memory bandwidth consumed by a given thread, application, VM or container at different Levels of cache hierarchy and external memory using performance monitor events and Memory Bandwidth Monitoring (MBM). Once the memory bandwidth is measured software can dynamically adjust the bandwidth throttling level for the class of

service (CLOS) used by that application. In other usages, software control loops may monitor application performance and adjust throttling levels dynamically to achieve certain performance targets.

More specific feature details about CBA are provided in the Intel<sup>®</sup> Architecture Instruction Set Extensions and Future Features. Note that the MSRs are listed in <u>Appendix A.5</u>. See <u>Appendix A.2</u> for CBA feature supported product details.

#### 3.2.4.1 CBA Overview

The CBA feature implements a local hardware controller which when enabled provides the capability to independently throttle memory bandwidth of the logical processors across cache hierarchy and complements the MBA controller which throttles the external memory bandwidth.

#### 3.2.4.2 Example of CBA Throttling Mechanism

An example of the bandwidth throttling enforced between L2 cache and L3 cache is the maximum of the bandwidth throttling from the local CBA controller within the logical processor and the MBA hardware controller. An example of CBA implementation is shown in Figure 3-9.

Figure 3-9. Example of CBA Throttling between L2 and L3 caches

#### 3.2.4.3 Software Interface

In order to allow software to adapt its tuning behavior and detect that cache bandwidth throttling is supported on a particular product generation, a CPUID bit is added to the Intel RDT A CPUID leaf to indicate support (details are provided in the Intel® Architecture Instruction Set Extensions Manual).