# **Programmer's Guide**

# Intel® QuickAssist Technology

Hardware Version 2.0

December 2024

Document Number: 743912-007

Performance varies by use, configuration and other factors. Learn more on the Intel's Performance Index site.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure.

Your costs and results may vary.

Intel technologies may require enabled hardware, software or service activation.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

See Intel's Legal Notices and Disclaimers.

© Intel Corporation. Intel, the Intel logo, Atom, Xeon, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

# Contents

| 1 | <b>Abc</b><br>1.1 | out this Document<br>Conventions and Terminology         | <b>1</b><br>1 |

|---|-------------------|----------------------------------------------------------|---------------|

| 2 | Arc               | hitecture                                                | 3             |

| 3 | Infra             | astructure                                               | 5             |

|   | 3.1               | Queues and Queue Pairs                                   | 5             |

|   |                   | 3.1.1 Queues Pairs                                       | 5             |

|   |                   | 3.1.2 Queue Bundles                                      | 6             |

|   | 3.2               |                                                          | 7             |

|   |                   | 3.2.1 Configurable Items (via config file)               | 7             |

|   | 3.3               | Memory Management                                        | 7             |

|   |                   | 3.3.1 Shared Virtual Memory                              | 7             |

|   |                   | 3.3.1.1 SVM Kernel Requirements                          | 8             |

|   |                   | 3.3.2 DMA-able Memory                                    | 8             |

|   |                   | 3.3.3 Memory Type Determination                          | 9             |

|   |                   | 3.3.4 Buffer Formats                                     | 9             |

|   |                   | 3.3.4.1 Flat Buffers                                     | 9             |

|   |                   | 3.3.4.2 Scatter-Gather List (SGL) Buffers                | 9             |

|   |                   | 3.3.5 Huge Pages                                         |               |

|   | 3.4               | Modes of Operation                                       |               |

|   |                   | 3.4.1 Calling Semantics                                  | 12            |

|   |                   | 3.4.1.1 Asynchronous (Polled)                            | 12            |

|   |                   | 3.4.1.2 Asynchronous (Interrupts)                        | 12            |

|   |                   | 3.4.1.3 Synchronous                                      | 12            |

|   |                   | 3.4.1.4 Pros And Cons                                    | 12            |

|   | 3.5               | Load Balancing                                           |               |

|   |                   | 3.5.1 Per Endpoint                                       | 16            |

|   |                   | 3.5.2 Across Endpoints                                   | 18            |

|   |                   | 3.5.2.1 Load Sharing Criteria                            | 18            |

|   |                   | 3.5.3 Dimensions                                         | 19            |

|   | 3.6               | Debugability                                             | 19            |

|   |                   | 3.6.1 Overview of Intel <sup>®</sup> QAT debugfs entries | 19            |

|   |                   | 3.6.1.1 Entries in /sys/kernel/debug/qat_*               |               |

|   |                   | 3.6.1.2 Memory driver queries (qae_mem_slabs)            |               |

|   | 3.7               | Heartbeat                                                |               |

|   |      | 3.7.1  | Heartbeat Operation                                                      | 21 |

|---|------|--------|--------------------------------------------------------------------------|----|

|   |      |        | 3.7.1.1 Initialization                                                   |    |

|   |      |        | 3.7.1.2 Heartbeat Monitoring                                             |    |

|   |      |        | 3.7.1.3 Resetting a Failed Device                                        |    |

|   |      | 3.7.2  | Incorporating Heartbeat into Intel <sup>®</sup> QAT Applications         |    |

|   |      | 3.7.3  | Restart Sequence                                                         |    |

|   |      | 3.7.4  | Status of Packets in Flight (Crypto Applications Only)                   |    |

|   |      | 3.7.5  | Determining Device ID                                                    |    |

|   |      | 3.7.6  | Testing Heartbeat                                                        |    |

|   |      | 0.7.0  | 3.7.6.1 Simulated Heartbeat Failure Configuration                        |    |

|   |      |        | 3.7.6.2 Simulating Heartbeat Failure                                     |    |

|   |      | 3.7.7  | Handling Device Failures in a Virtualized Environment                    |    |

|   |      | 3.7.8  |                                                                          |    |

|   | 20   |        | Incorporating Dummy Responses into an Intel <sup>®</sup> QAT Application |    |

|   | 3.8  |        | netry                                                                    |    |

|   |      | 3.8.1  | Telemetry Usage                                                          |    |

|   |      |        | 3.8.1.1 Out-Of-Tree                                                      |    |

|   |      |        | 3.8.1.2 In-Tree                                                          |    |

|   |      | 3.8.2  | Telemetry Control                                                        |    |

|   |      |        | 3.8.2.1 Telemetry Commands                                               |    |

|   |      |        | 3.8.2.2 Device Level Telemetry Values                                    |    |

|   |      |        | 3.8.2.3 Ring Pair Level Telemetry Values                                 |    |

|   |      | 3.8.3  | Monitoring Telemetry - Text Based                                        |    |

|   |      |        | 3.8.3.1 Out-Of-Tree                                                      |    |

|   |      |        | 3.8.3.2 In-Tree                                                          |    |

|   | 3.9  |        | _imiting                                                                 |    |

|   |      | 3.9.1  | Service Level Agreement (SLA)                                            |    |

|   |      | 3.9.2  |                                                                          |    |

|   |      | 3.9.3  | SLA Manager Application                                                  |    |

|   |      |        | 3.9.3.1 SLA Commands                                                     |    |

|   | 3.10 |        | r Management                                                             |    |

|   |      | 3.10.1 | Configuration                                                            |    |

|   |      |        | 3.10.1.1 Out-of-Tree                                                     |    |

|   |      |        | 3.10.1.2 In-Tree                                                         | 37 |

|   |      | 3.10.2 | Usage                                                                    | 37 |

|   |      | 3.10.3 | Considerations                                                           | 38 |

|   | 3.11 | Reliab | pility, Availability, and Stability (RAS)                                | 38 |

|   |      | 3.11.1 | RAS Usage                                                                | 38 |

|   |      | 3.11.2 | AER Errors                                                               | 39 |

| _ | _    |        |                                                                          |    |

| 4 |      |        |                                                                          | 0  |

|   | 4.1  |        | olling the Driver                                                        |    |

|   |      | 4.1.1  | qat_service                                                              |    |

|   |      |        | 4.1.1.1 qat_service Usage                                                |    |

|   |      | 4.1.2  | adf_ctl                                                                  |    |

|   |      |        | 4.1.2.1 adf_ctlUsage                                                     |    |

|   |      |        | 4.1.2.2 Examples                                                         |    |

|   | 4.2  | • •    | cation Payload Memory Allocation                                         |    |

|   |      | 4.2.1  | Services                                                                 | łЗ |

|   |            | 4.2.2  | Thread S   | Specific USDM                                                               | <br> | 43 |

|---|------------|--------|------------|-----------------------------------------------------------------------------|------|----|

|   | 4.3        | Retur  | n Codes    | ·<br>· · · · · · · · · · · · · · · · · · ·                                  | <br> | 44 |

|   | 4.4        | Linux' | * Device D | river Operations Return Codes                                               | <br> | 45 |

| _ | _          |        |            |                                                                             |      |    |

| 5 |            |        | tion Files |                                                                             |      | 47 |

|   | 5.1        |        | 2          | ile Overview                                                                |      |    |

|   | 5.2        |        |            | 1                                                                           |      |    |

|   |            | 5.2.1  |            | Enabled                                                                     |      |    |

|   |            |        |            | Performance Considerations                                                  |      |    |

|   |            | 5.2.2  | Services   | Profile                                                                     | <br> | 50 |

|   |            |        | 5.2.2.1    | General Default Configuration Parameters                                    | <br> | 51 |

|   |            | 5.2.3  | Concurre   | ent Requests                                                                | <br> | 51 |

|   |            | 5.2.4  | Power M    | anagement Parameters                                                        | <br> | 52 |

|   |            | 5.2.5  | Shared V   | /irtual Memory (SVM) Parameters                                             | <br> | 52 |

|   |            |        | 5.2.5.1    | SVMEnabled                                                                  | <br> | 52 |

|   |            |        | 5.2.5.2    | ATEnabled                                                                   | <br> | 53 |

|   | 5.3        | Logic  |            | es Section                                                                  |      |    |

|   |            | 5.3.1  |            | L] Section                                                                  |      |    |

|   |            | 5.3.2  | -          | cess [xxxxx] Sections                                                       |      |    |

|   |            | 5.3.3  |            | aphic Logical Instance Parameters                                           |      |    |

|   |            | 5.3.4  |            | npression Logical Instance Parameters                                       |      |    |

|   |            | 5.3.5  |            | he Core Affinity Parameter for a Logical Instance                           |      |    |

|   | 5.4        |        |            | per of Process Calculations                                                 |      |    |

|   | 5.4        | 5.4.1  |            | g the Maximum Number of Processes/Instances                                 |      |    |

|   |            | 0.4.1  |            | Invalid Configurations                                                      |      |    |

|   |            |        |            | Configuring Instances for Virtual Functions                                 |      |    |

|   | 5.5        | Confi  |            | Itiple Intel <sup>®</sup> QuickAssist Technology Endpoints in a System      |      |    |

|   | 5.6        |        |            | Itiple Processes on a System with Multiple Intel <sup>®</sup> QAT Endpoints |      |    |

|   | 5.0<br>5.7 |        |            |                                                                             |      |    |

|   | 5.7        | Samp   | le coningt |                                                                             | <br> | 05 |

| 6 | Ser        | vices  |            |                                                                             |      | 66 |

| - | 6.1        |        | Compress   | ion                                                                         | <br> |    |

|   | • • •      |        | •          | ssion Features                                                              |      |    |

|   |            |        |            |                                                                             |      |    |

|   |            | 6.1.3  | •          | ssion Session Setup                                                         |      |    |

|   |            | 6.1.4  |            | ression Session Setup                                                       |      |    |

|   |            | 0.1. 1 |            | Deflate Decompression                                                       |      |    |

|   |            |        |            | LZ4 Decompression                                                           |      |    |

|   |            |        |            | LZ4 Decompression Limitations                                               |      |    |

|   |            |        |            | Multi-frame decompression support                                           |      |    |

|   |            | 6.1.5  |            | ance Considerations                                                         |      |    |

|   |            |        |            |                                                                             |      |    |

|   |            | 6.1.6  | Flush Fla  |                                                                             |      |    |

|   |            | 6.1.7  |            | ms                                                                          |      |    |

|   |            | 6.1.8  |            | mpressed Data Block format                                                  |      |    |

|   |            | (10    |            | LZ4 Compression Support                                                     |      |    |

|   |            | 6.1.9  | •          | ss-and-Verify                                                               |      |    |

|   |            |        |            | Compress and Verify Error log in Sysfs                                      |      |    |

|   |            |        | 6.1.9.2    | Compress and Verify and Recover (CnVnR)                                     | <br> | 73 |

|     | 6.1.10     | Dynami               | c Compression                                                 | 74 |

|-----|------------|----------------------|---------------------------------------------------------------|----|

|     | 6.1.11     |                      | Im Expansion with Auto Select Best Feature (ASB)              |    |

|     | 6.1.12     |                      | Im Compression Expansion                                      |    |

|     | 6.1.13     | No Sess              | sion API                                                      | 76 |

|     | 6.1.14     | Compre               | ession Levels                                                 |    |

|     | 6.1.15     | Compre               | ession Status Codes                                           |    |

|     | 6.1.16     | Intel <sup>®</sup> Q | uickAssist Technology Compression API Errors                  | 78 |

|     |            | 6.1.16.1             | Compression API Errors                                        | 78 |

|     | 6.1.17     | Overflov             | ws Errors                                                     | 83 |

|     |            | 6.1.17.1             | Traditional API Overflow Exception                            | 84 |

|     |            | 6.1.17.2             | Data Plane API Overflow Error                                 | 85 |

|     |            | 6.1.17.3             | Handling Overflow Errors                                      |    |

|     |            | 6.1.17.4             | Compression Overflows in a Virtual Environment                |    |

|     |            | 6.1.17.5             | Avoiding Compression Overflow Exceptions                      |    |

|     | 6.1.18     |                      | y Checksums                                                   |    |

|     |            | 6.1.18.1             | Verify HW Integrity CRC's                                     |    |

|     | 6.1.19     |                      | ompression Applications                                       |    |

|     |            | 6.1.19.1             | Compression for Storage                                       |    |

| ( ) | <b>•</b> • |                      | Data Deduplication and WAN Acceleration                       |    |

| 6.2 | <i>,</i> , |                      | Services                                                      |    |

|     | 6.2.1      | 6.2.1.1              |                                                               |    |

|     |            | 6.2.1.1<br>6.2.1.2   | Supported Cipher Algorithms                                   |    |

|     |            | 6.2.1.2<br>6.2.1.3   | Supported Hash/Authenticate Algorithms                        |    |

|     | 6.2.2      |                      | graphy Applications                                           |    |

|     | 0.2.2      | 6.2.2.1              | IPsec and SSL VPNs                                            |    |

|     |            | 6.2.2.2              | Encrypted Storage                                             |    |

|     |            | 6.2.2.3              | Web Proxy Appliances                                          |    |

|     |            | 0121210              |                                                               |    |

| Sup | portec     |                      |                                                               | 94 |

| 7.1 |            | -                    | ist Technology APIs                                           |    |

|     | 7.1.1      |                      | graphic and Data Compression API Descriptions                 |    |

|     |            | 7.1.1.1              | Data Plane APIs Overview                                      |    |

|     |            | 7.1.1.2              | IA Cycle Count Reduction When Using Data Plane APIs $\ . \ .$ |    |

|     |            | 7.1.1.3              | Usage Constraints on the Data Plane APIs                      |    |

|     | 7.1.2      | -                    | AT API Limitations                                            |    |

| 7.2 |            | ional API:           |                                                               |    |

|     | 7.2.1      | ,                    | c Instance Allocation Functions                               |    |

|     |            | 7.2.1.1              | icp_sal_userCyGetAvailableNumDynInstances                     |    |

|     |            | 7.2.1.2              | icp_sal_userDcGetAvailableNumDynInstances                     |    |

|     |            | 7.2.1.3              |                                                               |    |

|     |            | 7.2.1.4<br>7.2.1.5   | <pre>icp_sal_userDcInstancesAlloc</pre>                       |    |

|     |            | 7.2.1.5<br>7.2.1.6   | icp_sal_userCyFreeInstances                                   |    |

|     |            | 7.2.1.0              | icp_sal_userCyGetAvailableNumDynInstancesByDevPkg             |    |

|     |            | 7.2.1.7              | icp_sal_userCyGetAvailableNumDynInstancesByDevPkg             |    |

|     |            | 7.2.1.8              | icp_sal_userCyInstancesAllocByDevPkg                          |    |

|     |            | 7.2.1.7              | icp_sal_userDcInstancesAllocByDevPkg                          |    |

|     |            |                      |                                                               |    |

|   |            | 7.2.1.11 icp_sal_userCyGetAvailableNumDynInstancesByPkgAccel | 106        |

|---|------------|--------------------------------------------------------------|------------|

|   |            | 7.2.1.12 icp_sal_userCyInstancesAllocByPkgAccel              | 106        |

|   | 7.2.2      | IOMMU Remapping Functions                                    | 107        |

|   |            | 7.2.2.1 icp_sal_iommu_get_remap_size                         |            |

|   |            | 7.2.2.2 icp_sal_iommu_map                                    |            |

|   |            | 7.2.2.3 icp_sal_iommu_unmap                                  |            |

|   |            | 7.2.2.4 IOMMU Remapping Function Usage                       |            |

|   | 7.2.3      | Polling Functions                                            |            |

|   |            | 7.2.3.1 icp_sal_pollBank                                     | 110        |

|   |            | 7.2.3.2 icp_sal_pollAllBanks                                 |            |

|   |            | 7.2.3.3 icp_sal_CyPollInstance                               |            |

|   |            | 7.2.3.4 icp_sal_DcPollInstance                               |            |

|   |            | 7.2.3.5 icp_sal_CyPollDpInstance                             |            |

|   |            | 7.2.3.6 icp_sal_DcPollDpInstance                             |            |

|   | 7.2.4      | User Space Access Configuration Functions                    |            |

|   | , <u> </u> | 7.2.4.1 icp_sal_userStart                                    |            |

|   |            | 7.2.4.2 icp_sal_userStop                                     |            |

|   | 7.2.5      | Version Information Function                                 |            |

|   | 7.2.0      | 7.2.5.1 icp_sal_getDevVersionInfo                            |            |

|   | 7.2.6      | Reset Device Function                                        |            |

|   | 7.2.0      | 7.2.6.1 icp_sal_reset_device                                 |            |

|   | 7.2.7      | Thread-Less APIs                                             |            |

|   | 7.2.7      | 7.2.7.1 icp_sal_poll_device_events                           |            |

|   |            | 7.2.7.2 icp_sal_find_new_devices                             |            |

|   | 7.2.8      | Compress and Verify (CnV) Related APIs                       |            |

|   | 7.2.0      | 7.2.8.1 icp_sal_get_dc_error                                 |            |

|   |            | 7.2.8.2 icp_sal_dc_simulate_error                            |            |

|   | 7.2.9      | Heartbeat APIs                                               |            |

|   | 1.2.7      | 7.2.9.1 icp_sal_check_device                                 |            |

|   |            | 7.2.9.1 icp_sal_check_all_devices                            |            |

|   |            | 7.2.9.3 icp_sal_heartbeat_simulate_failure                   |            |

|   | 7.2.10     |                                                              |            |

|   | 7.2.10     |                                                              |            |

|   |            | 7.2.10.1 icp_sal_poll_device_events                          |            |

|   |            | 7.2.10.2 cpaCyInstanceSetNotificationCb                      |            |

|   | 7011       | 7.2.10.3 cpaDcInstanceSetNotificationCb                      |            |

|   | 7.2.11     |                                                              |            |

|   |            | 7.2.11.1 icp_sal_SymGetInflightRequests                      |            |

|   |            | 7.2.11.2 icp_sal_AsymGetInflightRequests                     |            |

|   | 7010       | 7.2.11.3 icp_sal_dp_SymGetInflightRequests                   |            |

|   | 7.2.12     | Service Specific Polling APIs                                |            |

|   |            | 7.2.12.1 icp_sal_CyPollSymRing                               |            |

|   |            | 7.2.12.2 icp_sal_CyPollAsymRing                              |            |

|   | 7.2.13     | Check Device Availability APIs                               |            |

|   |            | 7.2.13.1 icp_sal_userlsQatAvailable                          | 126        |

| 0 | \/:        | ion                                                          | 100        |

| ð |            |                                                              | <b>128</b> |

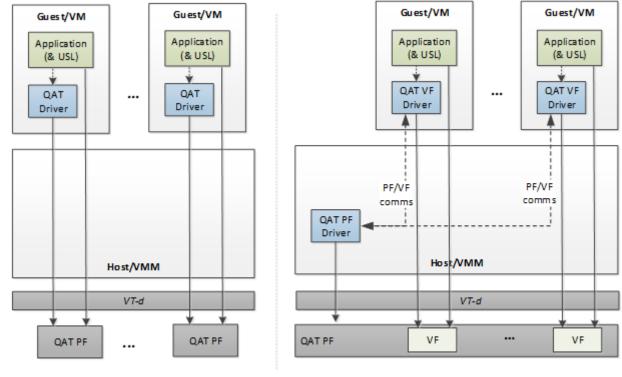

|   |            | alization Deployment Model for Intel® QAT 2.0                |            |

|   | 8.2 Physic | cal Device Direct Assignment                                 |            |

|   | 8.3<br>8.4 |         | e Root IOV (SR-IOV)                                |    |

|---|------------|---------|----------------------------------------------------|----|

| 9 | Sec        | ure Arc | chitecture Considerations 13                       | 32 |

|   | 9.1        | Termi   | nology                                             | 32 |

|   |            | 9.1.1   | Threat Categories                                  |    |

|   |            | 9.1.2   | Attack Mechanism                                   |    |

|   |            | 9.1.3   | Attacker Privilege                                 | 33 |

|   |            | 9.1.4   | Deployment Models                                  |    |

|   | 9.2        | Threa   | t/Attack Vectors                                   |    |

|   |            | 9.2.1   | General Mitigation                                 |    |

|   |            | 9.2.2   | General Threats                                    |    |

|   |            |         | 9.2.2.1 DMA                                        |    |

|   |            |         | 9.2.2.2 Intentional Modification of IA Driver      |    |

|   |            |         | 9.2.2.3 Modification of the QAT Configuration File |    |

|   |            |         | 9.2.2.4 Malicious Application Code                 |    |

|   |            |         | 9.2.2.5 Denial of Service                          |    |

|   |            | 9.2.3   | Threats Specific to Cryptographic Service          |    |

|   |            |         | 9.2.3.1 Reading Cryptographic Keys                 |    |

|   |            |         |                                                    |    |

#### 10 Revision History

138

# **List of Tables**

| 1                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                                                              |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | Pros and cons of modes of operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19<br>19<br>20<br>22<br>31<br>32<br>35<br>35<br>36<br>37<br>38 |

| 18<br>19<br>20                                                                       | Acceleration Driver Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                                             |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28                                         | General Section ParametersGeneral Default Configuration Parameters[KERNEL] Section Parameters[User Process] Section Parameters[User Process] Section ParametersGeneral Default Logical Instance ParametersData Compression Logical Instance ParametersGeneral Default Logical Instance ParametersConfiguration VariationsGeneral Default Configuring Physical Functions and Virtual Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51<br>54<br>55<br>56<br>56<br>58                               |

| 29<br>30<br>31<br>32<br>33                                                           | Compression CpaDcSessionSetupData Properties       Compression CpaDcSessionSetupData Properties       Compression CpaDcSessionSetupData Properties         Flush Flags       Compression CpaDcSessionSetupData Properties       Compression CpaDcSessionSetupData Properties         Checksums       Compression CpaDcSessionSetupData Properties       Compression CpaDcSessionSetupData Properties         Differences between LZ4 and LZ4s block format       CompressionSetupData Properties       CompressionSetupData Properties | 67<br>69<br>70                                                 |

| 34 | Compress and Verify and Recover (CnVnR) Behaviors | 73  |

|----|---------------------------------------------------|-----|

| 35 | ASB Settings                                      | 75  |

| 36 | Compression Levels                                | 77  |

| 37 | Compression API Errors                            | 78  |

| 38 | Overflows Errors                                  | 84  |

| 39 | Integrity Checksums                               | 86  |

| 40 | Supported Cipher Algorithms                       | 89  |

| 41 | Supported Hash/Authenticate Algorithms            | 90  |

| 42 | Supported Public Key Algorithms                   | 91  |

| 43 | Key Generation Cryptographic API Limitations      | 97  |

| 44 | Threat Categories                                 | 132 |

| 45 | Attack Mechanism                                  |     |

| 46 | Attacker Privilege                                |     |

| 47 | Deployment Models                                 | 134 |

# **1 About this Document**

This programmer's guide provides information on the architecture of the software and usage guidelines.

Information on the use of Intel<sup>®</sup> QuickAssist Technology (Intel<sup>®</sup> QAT) APIs, which provide the interface to the acceleration services (cryptographic and data compression), is documented in the related Intel<sup>®</sup> QAT software library documentation referenced in the Release Notes.

In this document, for convenience:

- *Software package* is used as a generic term for the Intel® QAT Software Package for Hardware Version 2.0.

- Acceleration driver is used as a generic term for the software that allows the Intel® QAT Software Library APIs to access the Intel® QAT Endpoint(s).

Note: Refer to the Release Notes for a list of supported platforms.

**Note:** Current version of this document covers the out-of-tree acceleration driver. Future version of this document will be updated to cover in-tree driver as well.

For additional details on in-tree driver refer to https://github.com/intel/qatlib.

# 1.1 Conventions and Terminology

The following conventions are used in this manual:

- Code text code examples, command line entries, Application Programming Interface (API) names, parameters, filenames, directory paths, and executables.

- Bold text graphical user interface entries, buttons, and actions in instructions.

- Italic text key terms and publication titles.

The following terms and acronyms are used in this manual.

#### Table 1: Terminology

| Term                   | Description                               |

|------------------------|-------------------------------------------|

| API                    | Application Programming Interface         |

| asym                   | Asymmetric Cryptography                   |

| BDF                    | Bus Device Function                       |

| BOM                    | Bill of Materials                         |

| CBC                    | Cipher Block Chaining                     |

| су                     | Cryptography                              |

| dc                     | Data Compression                          |

| GRUB                   | Grand Unified Bootloader                  |

| OS                     | Operating System                          |

| PCI                    | Peripheral Component Interconnect         |

| PF                     | PCIe Physical Function                    |

| Intel <sup>®</sup> QAT | Intel <sup>®</sup> QuickAssist Technology |

| SKU                    | Stock Keeping Unit                        |

| SR-IOV                 | Single Root-I/O Virtualization            |

| VF                     | Virtual Function                          |

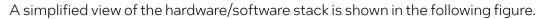

# 2 Architecture

Because the hardware is accessed via the Intel® QAT APIs, it is not necessary to know all of the hardware and software architecture details, but some knowledge of the underlying hardware and software is helpful for performance optimization and debug purposes.

The flow can be broken down as:

- 1. Application submits payloads via the Intel® QuickAssist API as part of the request. The user space library converts these requests into descriptors and places these in the Transmit (Tx) *hardware-assisted queues* (aka ring).

- 2. Firmware parses the descriptor and configures the accelerators accordingly. Upon a job completion firmware returns the processed payload (either encrypted or compressed or both) and generates a response message. This response message is inserted in the response ring.

- 3. A polling thread owned by the application queries the response ring via the Intel<sup>®</sup> Quick-Assist Library. If the application chooses non-blocking calls the user space library will issue a callback to the application to inform that the operation is complete.

**Note:** The UIO (to be replaced with VFIO) layer is a framework present in both Linux Kernel and user space library libudev. This framework enables exchanging data between Kernel and user space. It offers better latency performance than IOCTL.

# **3** Infrastructure

The following sections describe the building blocks of the Intel® QAT Endpoints' architecture.

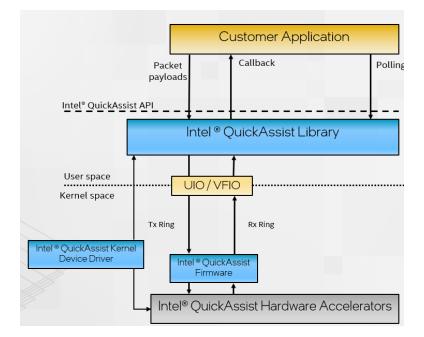

# 3.1 Queues and Queue Pairs

Communication between CPU and Intel<sup>®</sup> QuickAssist Technology hardware is via hardware-assisted queues (aka rings):

- Queues are circular buffers.

- Memory is in System DRAM.

- Device is configured with base address, entry size and number of entries via device CSRs.

- Head and Tail pointers are in device CSRs (MMIO space).

### 3.1.1 Queues Pairs

- To send a request, software writes request descriptor to next available entry in the request queue, and updates the tail pointer.

- Device firmware reads request descriptor from request queue, updating the head pointer. It then

processes the request, writes response descriptor onto response queue, and updates the tail

pointer.

- Response queues can be configured to generate an interrupt when device firmware updates the tail pointer, or can be polled.

## 3.1.2 Queue Bundles

Queues are grouped into bundles of 8 queues (4 Queue Pairs (QPs)).

• When SR-IOV is enabled, each bundle shows up as a separate Virtual Function.

Within each bundle, by default, a separate QP is used for each of the three possible services:

- 1. Public Key Crypto

- 2. Symmetric Crypto

- 3. Data Compression

- Public Key Crypto

- Symmetric Crypto

- Data Compression

|--|

Max of 2 service types per QAT device at a time. Each QP can be allocated to a specific service, in a bare metal environment.

# 3.2 Service Instances

At the Intel<sup>®</sup> QuickAssist Technology API, we abstract queue pairs using the concept of service instances.

- To use a service, an application must first get a handle to a service instance.

- Corresponds to one or more queue pairs:

- Data compression instance contains I queue pair.

- Cryptographic instance:

- \* QAT Gen2: contains 2 queue pairs, one for each sub-service of crypto (symmetric crypto, public key crypto).

- \* QAT Gen4: crypto instances can be specified as either sym (symmetric) or asym (asymmetric) cryptography and contain I queue pair.

# 3.2.1 Configurable Items (via config file)

- Queue depth (for each queue).

- Number of service instances per process for a given device (limited by available rings), for example:

- One per address space (e.g. user space processes).

- One per software or hardware thread (logical core), to avoid contention.

- Number of queue pairs per service, per bundle/VF, will be configurable in future.

# 3.3 Memory Management

This section describes memory management requirements for submitting buffers to the QAT hardware.

### 3.3.1 Shared Virtual Memory

Shared Virtual Memory (SVM) is a new feature in QAT 2.0 hardware. In QAT 1.x hardware, memory needs to be submitted to the hardware as pinned and physically contiguous memory. In QAT 2.0, SVM allows direct submission of an applications buffer, thus removing the memcpy cycle cost, cache thrashing, and memory bandwidth. The SVM feature enables passing virtual addresses to the QAT hardware for processing acceleration requests.

With SVM:

- Virtually contiguous (can also deal with Scatter Gather Lists of virtually addressed buffers).

- Virtually addressed.

• Can tolerate page faults but Pinning (i.e. locked, guaranteed resident in physical memory) is recommended for performance.

#### 3.3.1.1 SVM Kernel Requirements

In order to use SVM, ensure that kernel version v6.1 or higher is used. Alternatively verify the following kernel patches are applied.

- 81c95fbaebfa5990c3c786c8c3e87426a33106fe

- e65a6897be5e4939d477c4969a05e12d90b08409

Verification can be done with the following steps:

git tag --contains 81c95fbaebfa5990c3c786c8c3e87426a33106fe git tag --contains e65a6897be5e4939d477c4969a05e12d90b08409

This requirement provides mitigation for the issue QAT20-23616 described in the Release Notes.

The following kernel boot parameters need to be defined in order to utilize SVM.

```

intel_iommu=on,sm_on

```

Refer to *Shared Virtual Memory Parameters* for details on QAT configuration files updates required to support SVM.

### 3.3.2 DMA-able Memory

If SVM is not enabled, Memory passed to Intel<sup>®</sup> QuickAssist Technology hardware must be DMA'able.

- Physically contiguous (can also deal with Scatter Gather Lists).

- Physically addressed.

- If VT-d is enabled (e.g. in virtualized system), then Intel IOMMU will translate to host physical addresses as needed.

- Pinned (i.e. locked, guaranteed resident in physical memory).

Intel provides a User Space DMA-able Memory (USDM) component (kernel driver and corresponding user space library) which allocates/frees DMA-able memory, mapped to user space, performs virtual to physical address translation on memory allocated by this library

This component is used by the sample code supplied with the user space library.

## 3.3.3 Memory Type Determination

QAT 2.0 hardware offers the application to use virtual memory directly to sending the acceleration requests and saving the memory copy overhead. However, different SVM configurations will result in different memory types. The QAT package offers memory management library called User Space DMAable Memory(USDM) to help user space applications using the pinned memory.

| SVMEnabled | ATEnabled | Memory Type                            |

|------------|-----------|----------------------------------------|

| FALSE(0)   | FALSE(0)  | Pinned Memory (USDM)                   |

| TRUE(1)    | FALSE(0)  | Pinned Memory (USDM)                   |

| FALSE(0)   | TRUE(1)   | Invalid configuration                  |

| TRUE(1)    | TRUE(1)   | Pinned Memory (USDM) or Dynamic Memory |

|            |           | (malloc/ zalloc/mmap)                  |

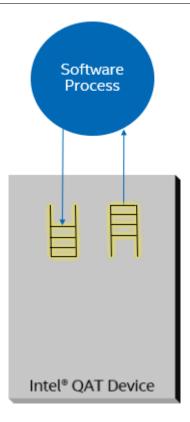

## 3.3.4 Buffer Formats

Data buffers are passed across the API interface in one of the following formats:

- Flat Buffers represent a single region of physically contiguous memory.

- Scatter-Gather Lists (SGL) are essentially an array of flat buffers, for cases where the memory is not all physically contiguous.

### 3.3.4.1 Flat Buffers

Flat buffers are represented by the type CpaFlatBuffer, defined in the file cpa.h. It consists of two fields:

- Data pointer **pData**: points to the start address of the data or payload. The data pointer is a virtual address; however, the actual data pointed to is required to be in contiguous and DMAable physical memory. This buffer type is typically used when simple, unchained buffers are needed.

- Length of this buffer: dataLenInBytes specified in bytes.

For data plane APIs (cpa\_sym\_dp.h and cpa\_dc\_dp.h), a flat buffer is represented by the type CpaPhys-FlatBuffer, also defined in cpa.h. This is similar to the CpaFlatBuffer structure; the difference is that, in this case, the data pointer, bufferPhysAddr, is a physical address rather than a virtual address.

#### 3.3.4.2 Scatter-Gather List (SGL) Buffers

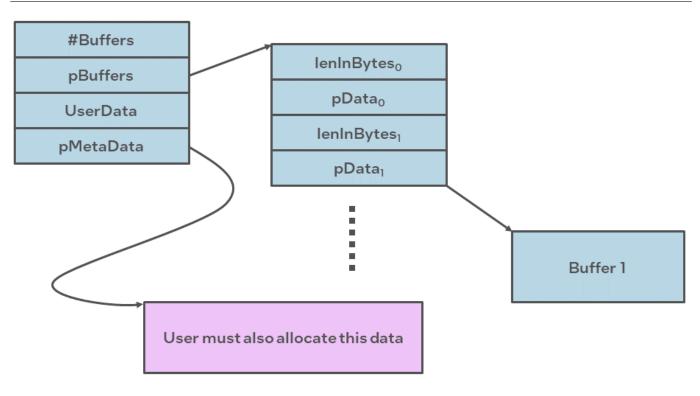

A scatter-gather list is defined by the type **CpaBufferList**, also defined in the file **cpa.h**. This buffer structure is typically used where more than one flat buffer can be provided to a particular API. The buffer list contains four fields, as follows:

- The number of buffers in the list.

- pBuffers: pointer to an unbounded array of flat buffers.

# intel

- UserData: an opaque field; is not read or modified internally by the API. This field could be used to provide a pointer back into an application data structure, providing the context of the call.

- pMetaData: pointer to metadata required by the API:

- The metadata is required for internal use by the API. The memory for this buffer needs to be allocated by the client as contiguous data. The size of this metadata buffer is obtained by calling cpaCyBufferListGetMetaSize for crypto, cpaBufferLists, and cpaDcBufferListGetMeta-Size for data compression.

- The memory required to hold the **CpaBufferList** structure and the array of flat buffers is not required to be physically contiguous. However, the flat buffer data pointers and the metadata pointer are required to reference physically contiguous DMAable memory.

- There is a performance impact when using scatter-gather lists instead of flat buffers. Refer to the Performance Optimization Guide for additional information.

- Scatter-Gather list (SGL) buffers should not have more than 256 entries.

For data plane APIs (cpa\_sym\_dp.h and cpa\_dc\_dp.h) a region of memory that is not physically contiguous is described using the CpaPhysBufferList structure. This is similar to the CpaBufferList structure; the difference, in this case, the individual flat buffers are represented using physical rather than virtual addresses.

# 3.3.5 Huge Pages

The included User space DMAable Memory driver **usdm\_drv.ko** supports 2MB pages. This allows direct access to main memory by devices other than the CPU and the actual supported maximum memory size in one individual allocation when huge pages is enabled is 2MB - 5KB. Where the 5KB is used for memory management for the memory driver. The use of 2MB pages provides benefits, but also requires additional configuration. Use of this capability assumes that a sufficient number of huge pages are allocated in the operating system for the particular use case and configuration.

Here are some example use cases:

• Default settings applied:

modprobe usdm\_drv.ko

• Set maximum amount of Non-uniform Memory Access (NUMA) type memory that the User Space DMAable Memory (USDM) driver can allocate to 32MB for all processes. Huge pages are disabled:

modprobe usdm\_drv.ko max\_mem\_numa=32768

• Set maximum number of huge pages that the USDM can allocate to 50 in total and 5 per process:

modprobe usdm\_drv.ko max\_huge\_pages=50 max\_huge\_pages\_per\_process=5

Note: This configuration works for up to the first 10 processes.

Here are examples of invalid use cases to avoid:

• This is erroneous configuration, maximum number of huge pages that USDM can allocate is 3 totals: 3 for a first process, 0 for the next processes:

insmod ./usdm\_drv.ko max\_huge\_pages=3 max\_huge\_pages\_per\_process=5

• This command results in huge pages being disabled because max\_huge\_pages is 0 by default:

insmod ./usdm\_drv.ko max\_huge\_pages\_per\_process=5

This command results in huge pages being disabled because max\_huge\_pages\_per\_process is 0 by default: insmod ./usdm\_drv.ko max\_huge\_pages=5

**Note:** The use of huge pages may not be supported for all use cases. For instance, depending on the driver version, some limitations may exist for an Input/Output Memory Management Unit (IOMMU).

# 3.4 Modes of Operation

## 3.4.1 Calling Semantics

#### 3.4.1.1 Asynchronous (Polled)

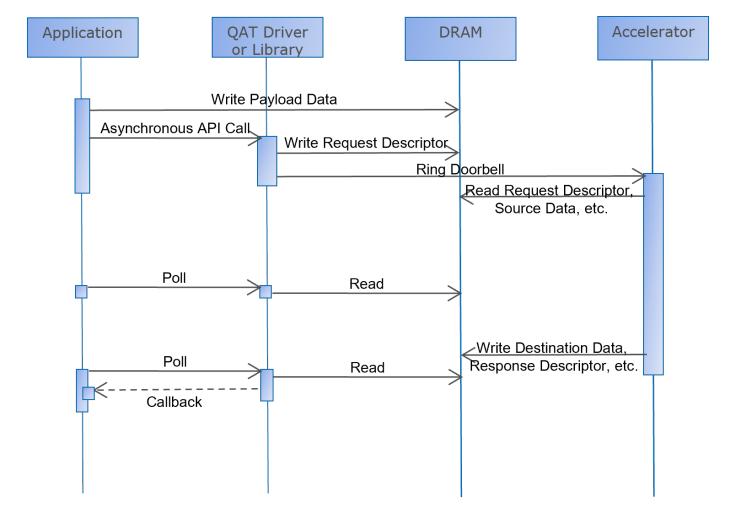

Hardware "request/response" interface is inherently asynchronous (non-blocking).

- Calling function returns once request submitted.

- Callback invoked when response available (polled).

#### 3.4.1.2 Asynchronous (Interrupts)

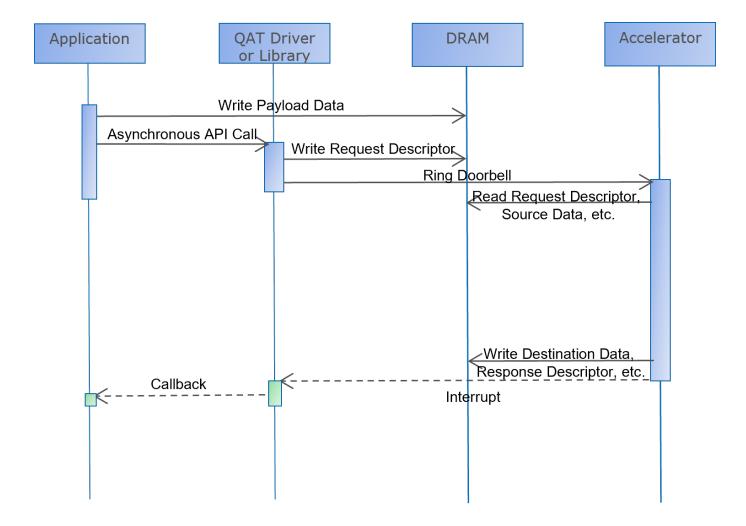

Hardware "request/response" interface is inherently asynchronous (non-blocking).

- Calling function returns once request submitted.

- Callback invoked when response available (interrupt-driven).

#### 3.4.1.3 Synchronous

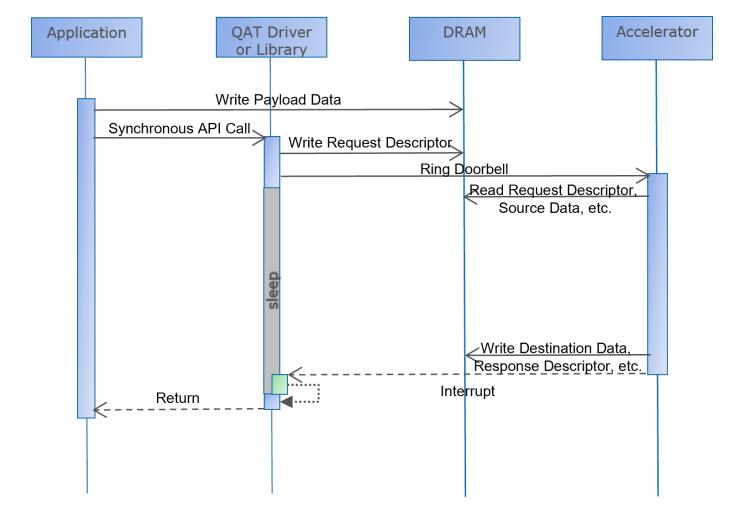

Software interface is traditionally synchronous (blocking).

- Calling function blocks until response available.

- Can be implemented "on top of" asynchronous hardware semantics.

#### 3.4.1.4 Pros And Cons

intel.

|                             | Asynchronous                                                                                                       | Synchronous                                                                                                                  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| CPU Utilization             | Software thread can do other things<br>while hardware processes job, without<br>need for expensive context switch. | Software thread blocked or idle<br>awaiting response. Can use<br>multi-threading, but context switching<br>can be expensive. |

| Acceleration<br>Utilization | A single software thread can have<br>multiple requests outstanding,<br>keeping multiple accelerator engines.       | Hardware has at most one request<br>outstanding per CPU/software thread,<br>remaining threads are idle.                      |

| Ease of Use                 | Can be difficult if application is designed to use synchronous APIs.                                               | Easier to integrate if application is designed to use synchronous APIs.                                                      |

Table 2: Pros and cons of modes of operation

Note: Asynchronous API tends to be optimal for performance, but harder to integrate.

# 3.5 Load Balancing

# 3.5.1 Per Endpoint

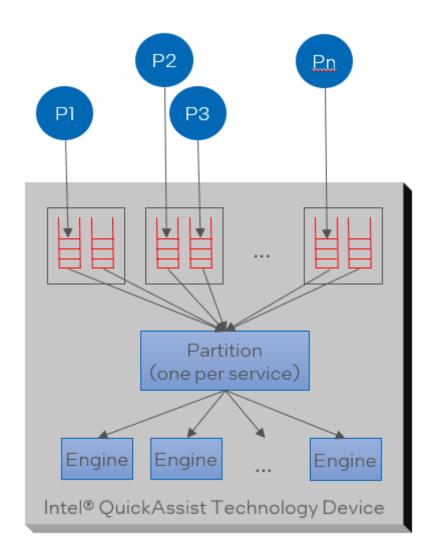

There are four arbiters, which by default are used for the different services (with one spare/unused). Each partition:

- Arbitrates across two request queues per bundle/VF, to pick a request.

- Load balances all of these requests across all available "engines".

Within a partition, arbitration uses round robin.

• Ensures fairness (in terms of number of requests) across queue pairs and guests

# 3.5.2 Across Endpoints

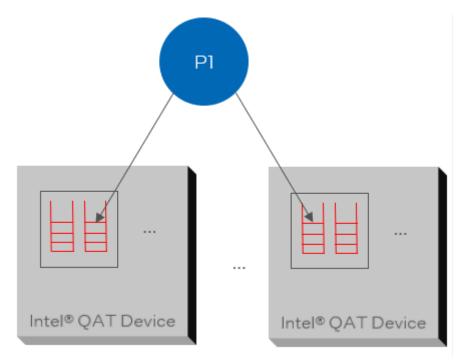

In a platform or CPU with multiple Intel® QAT devices, software is responsible for load sharing across devices/endpoints. Sapphire Rapids has up to four Intel® QAT devices/endpoints in a single CPU package (depending on SKU) PCIe card may have multiple (QAT 1.x) devices across one or more chipsets.

Software-based Load Sharing can be implemented at various layers:

- For applications using the Intel<sup>®</sup> QuickAssist Technology API, the application must implement load balancing.

- For applications using a framework (e.g. OpenSSL), the framework implements load balancing.

#### 3.5.2.1 Load Sharing Criteria

- Simple round-robin scheme recommended.

- May want to consider "locality" in a multi-socket (NUMA) platform.

## 3.5.3 Dimensions

Table 3: Dimensions Gen 1 & Gen 2

|                                        | Gen 1                                                  | Gen 2               |                                |

|----------------------------------------|--------------------------------------------------------|---------------------|--------------------------------|

|                                        | Intel® Communication<br>Chipset 8925 to 8955<br>Series | Intel® C62x Chipset | Intel Atom® Processor<br>C3000 |

| Number PCIe End-<br>points             | 1                                                      | 3                   | 1                              |

| Number of Bundles<br>/VFs per Endpoint | 32                                                     | 16                  | 16                             |

| Number of Queue Pairs<br>per Bundle    | 8                                                      |                     |                                |

Table 4: Dimensions Gen 3 & Gen 4

|                       | Gen 3                            | Gen 4                                                                 |

|-----------------------|----------------------------------|-----------------------------------------------------------------------|

|                       | Intel® Atom P5000 Processor/ Ice | Intel <sup>®</sup> 4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scal- |

|                       | Lake D                           | able Processor (per socket)                                           |

| Number PCIe End-      | 1                                | 4                                                                     |

| points                |                                  |                                                                       |

| Number of VFs per     | 128                              | 16                                                                    |

| Endpoint              |                                  |                                                                       |

| Number of Queue Pairs | 8                                | 4                                                                     |

| per Bundle            |                                  |                                                                       |

# 3.6 Debugability

## 3.6.1 Overview of Intel<sup>®</sup> QAT debugfs entries

Some useful debugging information for the driver and configuration is available via the Linux debugfs file system, with the entries /sys/kernel/debug/qat\_\* and /sys/kernel/debug/qae\_mem\_dbg/ qae\_mem\_slabs.

### 3.6.1.1 Entries in /sys/kernel/debug/qat\_\*

This includes:

| Table 5: Intel® QuickAssist Technology /sys/kernel/debug |

|----------------------------------------------------------|

| Entries                                                  |

| Entry        |        | Description                                          | Supported | Plat- |

|--------------|--------|------------------------------------------------------|-----------|-------|

|              |        |                                                      | forms     |       |

| cnv_errors   |        | Indicates number of <i>compressAndVerify</i> errors. | All       |       |

|              |        | Refer to Compress and Verify Error log in Sysfs.     |           |       |

| dev_cfg      |        | Displays internal device configuration informa-      | All       |       |

|              |        | tion.                                                |           |       |

| frequency    |        | Displays frequency of Acceleration Engines.          | All       |       |

| fw_counters  |        | Displays Acceleration Engine firmware re-            | All       |       |

|              |        | quests/responses.                                    |           |       |

| heartbeat,   | heart- | Refer to System Virtual Files.                       | All       |       |

| beat_failed, | heart- |                                                      |           |       |

| beat_sent    |        |                                                      |           |       |

| pm_status    |        | Displays power management status. Refer to           | QAT 2.0   |       |

|              |        | Power Management for additional information.         |           |       |

| transport    |        | Contains firmware request/response data. Avail-      | All       |       |

|              |        | able only for kernel space instances.                |           |       |

| version      |        | Includes package version information.                | All       |       |

#### 3.6.1.2 Memory driver queries (qae\_mem\_slabs)

Debug features are also available by reading and writing the file /sys/kernel/debug/qae\_mem\_dbg/ qae\_mem\_slabs. When *reading* the virtual/physical address, size and slab id together with the pid of the allocating process are shown. *Writing* a string to the file will start executing debug commands.

For example:

```

# cat /sys/kernel/debug/qae_mem_dbg/qae_mem_slabs

Pid 78854, Slab Id 10550771712

Virtual address 00000000b39412d, Physical Address 274e00000, Size 2097152

Pid 78854, Slab Id 10309599232

Virtual address 000000003670dd45, Physical Address 266800000, Size 2097152

...

```

There are three commands supported, and the below table shows their output:

| Writing these strings                                          | will output this when the file is read           |  |

|----------------------------------------------------------------|--------------------------------------------------|--|

| d <pid> <virtual address="" or="" physical=""></virtual></pid> | The 256 byte in hex and ascii from the start ad- |  |

|                                                                | dress                                            |  |

Table 6: Read/Write to /sys/kernel/debug/qae\_mem\_dbg/qae\_mem\_slabs

continues on next page

| Table 6 – continued from previous page                            |                                                      |  |  |

|-------------------------------------------------------------------|------------------------------------------------------|--|--|

| Writing these strings                                             | will output this when the file is read               |  |  |

| "c <pid> <slab id="">" (pid should be the process id</slab></pid> | The allocation bit map for the given slab identifier |  |  |

| that can be obtained by a previous read)                          |                                                      |  |  |

| "t"                                                               | Total size of NUMA memory allocated in kernel        |  |  |

|                                                                   | space                                                |  |  |

For example, by combining a write to the file and a subsequent read, you can see the total allocated NUMA memory, e.g.:

```

# echo "t" > /sys/kernel/debug/qae_mem_dbg/qae_mem_slabs ; cat /sys/kernel/debug/qae_mem_dbg/

→qae_mem_slabs

Total allocated NUMA memory: 142606336 bytes

```

As above, the "d" and "c" commands will output their respective information.

# 3.7 Heartbeat

Under some circumstances, firmware in the Intel® QAT devices could become unresponsive, requiring a device reset to recover. The Intel® QAT Heartbeat feature provides a mechanism for the customer application to detect and reset unresponsive devices. It also notifies the application processes of the start and end of the reset operation and suspends all Intel® QAT instances between the events.

### 3.7.1 Heartbeat Operation

A Heartbeat-enabled Intel<sup>®</sup> QAT device firmware periodically writes counters to a specified physical memory location. A pair of counters per thread is incremented at the start and end of the main processing loop within the firmware. Checking for Heartbeat consists of checking the validity of the pair of counter values for each thread. Stagnant counters indicate a firmware hang.

#### 3.7.1.1 Initialization

At startup, the Intel<sup>®</sup> QAT device driver allocates memory for the counter pairs to be written by the firmware and then sends a message to the firmware to start the Heartbeat functionality.

#### 3.7.1.2 Heartbeat Monitoring

Heartbeat check/monitoring refers to invocation of one of the two API calls that checks if the device is responsive. Heartbeat failure refers the API returning failure.

The Intel<sup>®</sup> QAT driver does not monitor for Heartbeat. It should be initiated by a Heartbeat management thread calling one of the following APIs periodically:

- icp\_sal\_check\_device(Cpa32U accelId)

- icp\_sal\_check\_all\_devices(void)

A failure return code implies the device has failed or hung.

The Heartbeat management thread should satisfy the following conditions:

- For any given device, only one such process/thread should monitor.

- One process can monitor one or more devices.

- It can be a user application that uses Intel<sup>®</sup> QAT services, or a separate management/control plane process.

- In virtualized environment, monitoring process(es)/thread(s) must run in the context of the host or hypervisor.

#### 3.7.1.3 Resetting a Failed Device

A device can be configured for automatic reset by the Intel<sup>®</sup> QAT framework or manually reset by the application by using the AutoResetOnError field in the device configuration file /etc/<device>.conf, as shown below.

| AutoResetOnError Value | Action on Heartbeat Failure    |

|------------------------|--------------------------------|

| O (default)            | Do not reset the device        |

| 1                      | Reset the device automatically |

If an Intel<sup>®</sup> QAT device is not configured for automatic reset, the management thread should reset it using the **icp\_sal\_reset\_device(Cpa32U accelId)** API.

The icp\_sal\_reset\_device() function starts an asynchronous reset sequence and returns immediately. The reset function should not be called again until the device has completed the reset to avoid a reset storm. The icp\_sal\_check\_device(<device id>) function could be called in a loop to check if the device reset is still in progress.

If the application devices are all configured for automatic reset then the icp\_sal\_check\_all\_devices() function could be used; otherwise, the function should not be used because it does not return the identity of the failed device, which is a required parameter for the icp\_sal\_reset\_device() function.

#### **Function Signatures**

The details of the above functions, parameters, and return values can be found in *Supported APIs > Additional APIs*.

## 3.7.2 Incorporating Heartbeat into Intel<sup>®</sup> QAT Applications

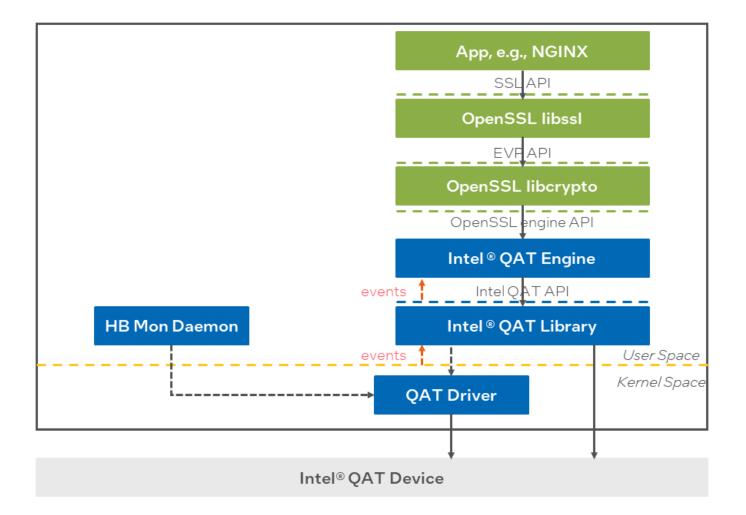

A typical Intel<sup>®</sup> QAT user application consists of two tasks:

- The first task is typically an application thread that initializes Intel<sup>®</sup> QAT instances and sessions, and then submits service requests for Intel<sup>®</sup> QAT crypto or compression.

- If an application employs polling to receive Intel<sup>®</sup> QAT service responses, then this task is also an application thread. Alternatively, responses are received as an interrupt handler.

Two more tasks are required to support Heartbeat:

- The first is a management task to monitor the devices for failure or hang and then resets them, when required. As discussed earlier, this could be an application thread of an independent management process.

- The second task is an application thread that polls for device reset events:

- Device is restarting: CPA\_INSTANCE\_EVENT\_RESTARTING

- Device restart is complete: CPA\_INSTANCE\_EVENT\_RESTARTED

If the application employs polling to receive Intel<sup>®</sup> QAT service responses, then this task could be included in the same polling loop.

The polling for device events is done using the API: icp\_sal\_poll\_device\_events().

The two callback functions for crypto and compression are registered using the following APIs:

- cpaCyInstanceSetNotificationCb

- cpaDcInstanceSetNotificationCb

The details of the above functions, parameters, and return values can be found in *Supported APIs > Additional APIs*.

### 3.7.3 Restart Sequence

During the restart sequence, the user space library releases the memory used for rings and other data structures as part of the shutdown and reallocates them when the restart is completed. This is transparent to the user application, so it can continue to use the same logical instance after reset to submit Intel<sup>®</sup> QAT service requests. Any memory allocated by the user application for the Intel<sup>®</sup> QAT service is untouched during device reset.

A typical Heartbeat error use-case is as follows:

1. The driver and the firmware is loaded, initialized and started.

- 2. The user-space application registers to receive instance notifications by calling **cpaCyInstance-SetNotificationCb** and **cpaDcInstanceSetNotificationCb**.

- 3. The management thread monitors for the device's heartbeat. When a device is unresponsive, a device reset is initiated by this thread or by the Intel<sup>®</sup> QAT framework depending on the device configuration.

- 4. The kernel-space process sends the restarting event to the user-space process.

- 5. The user-space driver passes the device restarting event to all the registered application instances. It also frees memory and rings associated with the registered instances.

- 6. The kernel-space driver triggers the device reset.

- 7. During reset, the Intel<sup>®</sup> QAT service request made by the user application returns one of:

- CPA\_STATUS\_FAIL

- CPA\_STATUS\_RETRY

- CPA\_STATUS\_RESTARTING

- 8. When the device reset is complete, the kernel-space driver sends a device restarted event to the user space driver.

- 9. The user space driver allocates the memory and rings and then forwards the device Restarted event to each of the registered instances.

# 3.7.4 Status of Packets in Flight (Crypto Applications Only)

When a device has fatal errors, the application ordinarily cannot determine whether or not inflight requests have been processed successfully.

The current Intel<sup>®</sup> QAT release includes a dummy response feature that creates mock responses to all requests submitted during a fatal error condition, so the application can detect them and, therefore, know which requests need to be resubmitted to the available devices or to the software.

**Note:** The sequence of dummy responses will match the sending request sequence for all requests submitted during a fatal error.

Since the dummy response feature only supports Public Key Encryption (PKE), dummy responses may be generated only when the **icp\_sal\_cyPollInstance()** function is called, since it is the function for crypto services.

The icp\_sal\_poll\_device\_events() function should also be called by the application, so that the application get a notification when the device encounters a failure and dummy responses are generated when calling icp\_sal\_CyPollInstance() for the inflight requests.

## 3.7.5 Determining Device ID

The *<device id>* that is passed as a parameter to several Heartbeat API is the numeric suffix of the device name displayed by the following command. (device name: *qat\_dev0*):

service qat\_service status

The output will look like:

```

There is 1 QAT acceleration device(s) in the system: qat_dev0 - type: c3xxx, inst_id: 0, node_

id: 0, bsf: 01:00.0, #accel: 3 #engines: 6 state: up

```

The Intel<sup>®</sup> QAT library has no API to discover the device number easily. However, an application can use the IOCTLs **IOCTL\_GET\_NUM\_DEVICES** and **IOCTL\_STATUS\_ACCEL\_DEV** to find the device\_id of a particular device if they know the Bus Device Function (BDF). Refer to **perform\_query\_dev()** in **./adf\_ct1.cpp**.

### 3.7.6 Testing Heartbeat

Two debug capabilities are available to assist the developers incorporating Heartbeat into their applications:

- Simulation of Heartbeat failure.

- System virtual files under /sys/kernel/debug/.

#### 3.7.6.1 Simulated Heartbeat Failure Configuration

The Heartbeat feature is always enabled in the package. However, a debug capability that simulates device failure can be enabled during the configure step as follows:

./configure --enable-icp-hb-fail-sim

#### 3.7.6.2 Simulating Heartbeat Failure

Simulating Heartbeat failure can be accomplished using two methods:

- Using the APlicp\_sal\_heartbeat\_simulate\_failure(<device id>).

- Executing the command:

cat /sys/kernel/debug/<device>/heartbeat\_sim\_fail

#### **System Virtual Files**

**Note:** The heartbeat /sys/kernel/debug files are associated with the QAT Physical Function (PF).

The Heartbeat feature implements the following system virtual files under the /sys/kernel/debug/qat\_<device>\_<your\_device\_BDF>/ directory. For additional details refer to debugfs-driver-gat documentation.

Table 8: Heartbeat System Virtual Files

| File             | Content                                                                  |

|------------------|--------------------------------------------------------------------------|

| heartbeat        | 0: Device is responsive1: Device is NOT responsive.                      |

| heartbeat_failed | Number of times the device became unresponsive.                          |

| heartbeat_sent   | Number of times the control process checked if the device is responsive. |

A developer could simulate the Heartbeat management process by running the following script in the background:

| #!/bin/bash                                                       |         |

|-------------------------------------------------------------------|---------|

| while : do                                                        |         |

| cat /sys/kernel/debug/ <device>/heartbeat &gt; /dev/null</device> | sleep 1 |

| done                                                              |         |

#### **Heartbeat Polling Frequencies**

The application developer should decide on the following two Heartbeat polling frequencies:

- Device Heartbeat monitoring.

- Checking for device reset events.

#### **Device Heartbeat Monitoring**

Consider the following points when determining the frequency of Heartbeat monitoring:

- Increasing Heartbeat monitoring frequency will minimize the customer's system downtime.

- However, since device unresponsiveness should be an infrequent event, high frequency Heartbeat monitoring wastes CPU cycles.

- Also, if there are large Intel<sup>®</sup> QAT service requests that take some time to complete, high frequency Heartbeat monitoring could result in false reports of unresponsiveness.

- With QAT Gen4 devices, heartbeat update timer in firmware is a constant value of 200ms (unconfigurable). With QAT Gen2 devices this value is configurable with configuration item **Heartbeat-Timer** (the default value is 500ms and the minimal allowed value is 200ms)

#### **Programmer's Guide**

• For both QAT Gen2 and Gen4 monitoring interval should be larger or equal than the Heartbeat update interval. (e.g. if user configure HeartbeatTimer=300, polling interval should be >=300ms)

#### **Checking for Device Reset Events**

If the application uses polling for reading Intel<sup>®</sup> QAT service responses, there is no value in checking for resets more frequently. Since device unresponsiveness is an infrequent occurrence, frequency of checking for reset events could be a fraction of the frequency of polling for Intel<sup>®</sup> QAT service responses.

## 3.7.7 Handling Device Failures in a Virtualized Environment

The Heartbeat feature in the acceleration software can be used in a virtualized environment. Refer to the Using Intel® Virtualization Technology (Intel® VT) with Intel® QuickAssist Technology Application Note for more details on enabling SR-IOV and the creation of Virtual Functions (VFs) from a single Intel® QuickAssist Technology acceleration device to support acceleration for multiple Virtual Machines (VMs).

The following sequence describes a possible use case for using the Heartbeat feature in a virtualized environment.

- 1. The Intel<sup>®</sup> QAT Physical Function driver (PF driver) isloaded, initialized and started.

- 2. The Intel<sup>®</sup> QAT Virtual Function driver (VF driver) is loaded, initialized and started in the Guest OS in the VM.

- 3. The PF driver detects that the firmware is unresponsive (using either of the following methods: User Proc Entry Read (not Enabled by Default) on page 47 or User Application Heartbeat APIs (not Enabled by Default) on page 48).

- 4. The PF driver sends the "Restarting" event message to the VF via the internal PF-to-VF communication messaging mechanism.

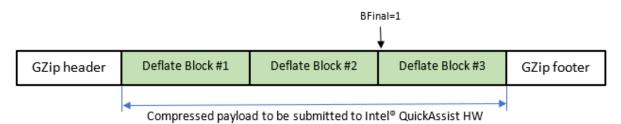

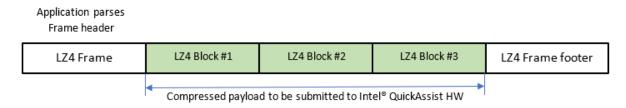

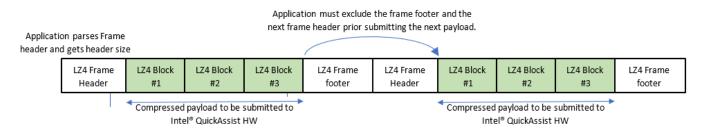

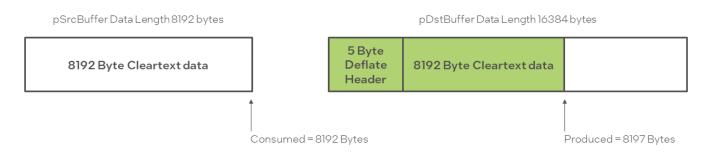

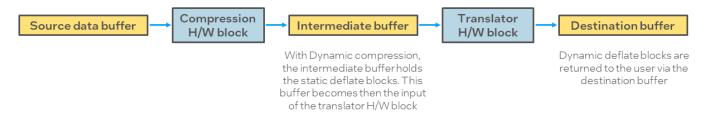

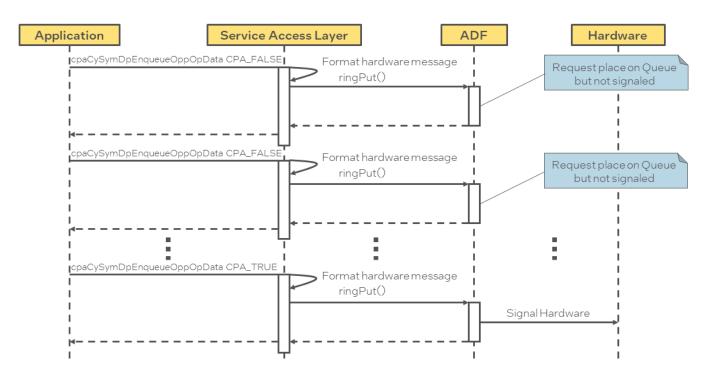

- 5. The VF driver sends the "Restarting" event to the application's registered callback. The callback is registered using either of the Intel<sup>®</sup> QAT API functions **cpaDcInstanceSetNotificationCb()** or **cpaCyInstanceSetNotificationCb()** in the Guest OS. (The application's callback function may perform any application-level cleanup.)